# Charge-carrier Transport in VLS (Vapour-Liquid-Solid) Grown Silicon Nanowires

Submitted in partial fulfilment of the requirements for the degree of

#### **DOCTOR OF PHILOSOPHY**

by

SANCHAR ACHARYA (Roll No. 124073003)

under the guidance of

**Prof. Anil Kottantharayil**

**Department of Electrical Engineering**

### INDIAN INSTITUTE OF TECHNOLOGY BOMBAY

2019

Dedicated to

my Teachers

and Taxpayers

Thesis Approval

The Thesis entitled

### Charge-carrier Transport in VLS (Vapour-Liquid-Solid) Grown Silicon Nanowires

by

Sanchar Acharya (Roll No. 124073003)

is approved for the degree of

Doctor of Philosophy

45 2019 Prof. Roy.P. Paily

Prof. Anil Kottantharayii

Date: May 2, 2019 Place: IIT Borshay, Munitas

Prof. Indrisder S. Samajdar

Pmf. P R. Nair

### Declaration

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

SANCHAR ACHARYA Roll No. 124073003

26. February 2019.

### Abstract

This work presents a study of electrical characteristics and charge carrier transport through vapour-liquid-solid (VLS) grown silicon nanowires using gold as catalyst. The silicon nanowires used for the study are grown using a simple cold-wall catalytic chemical vapour deposition (cat-CVD) tool. Silane (SiH<sub>4</sub>) is used as the source of silicon in VLS growth process. The gas is flown into the spherical reaction chamber from top, the sample is kept just below the gas inlet, on top of a heated chuck. The exhaust is placed below the sample holder, which carried unreacted SiH<sub>4</sub> and reaction byproduct H<sub>2</sub>, out of the chamber. Pressure inside the chamber is regulated by adjusting the gate valve fitted at the exhaust. Detailed overview of the growth process and details of optimisations are presented in this work. The simplicity of the process equipment and low thermal budget of the growth process described in this work should make VLS process accessible to a wider group of researchers and bring down the cost of production as well. It has been observed that, the current-voltage (IV) characteristics of the silicon nanowires exhibit a typical inverse-'S' like shape. The IV characteristics are almost linear at small voltages. However, at higher voltages, the conductivity of the nanowires vary linearly with square root of the applied voltage. Transition between these two regimes of conduction shifts to higher voltages as the temperature is reduced. This is a clear trait of Poole-Frenkel (PF) transport. PF is a well known form of hopping transport, where charge carriers are trapped inside a series of coulomb traps. At higher voltages (electric field), charge carriers are ripped from these traps and made available for conduction inside the solid. PF transport is always associated with disorderedness in the material. This is unlikely of a single crystal such as VLS grown silicon nanowires. Detailed physical characterisations are performed using transmission electron microscope (TEM) to investigate the structure of the nanowires. It has been found that the VLS grown silicon nanowires have several defects. Residue catalyst-silicon alloy are found trapped inside the native oxide shell and the surface of silicon nanowires. Two types of twin boundaries are found. One oriented along the axis of the silicon nanowires, the other spanning

as body diagonal of the nanowires. The biggest contributor to the origin of PF transport in these nanowires are hypothesised to be small ( $<25 \ nm^2$ ) regions of crystallographic misorientation found throughout the nanowires. These regions appear as dark patches in bright field TEM, but have no effect on the selected area electron diffraction (SAED) patterns, collected from the samples. This means that, the overall misorientation should be within 5° deviation from exact s-vector.

### Acknowledgements

This thesis would never be possible without persistent guidance of my supervisor, Prof. Anil kottantharayil. He not only mentored my doctoral research, but taught me important subjects and skills. I am eternally grateful for his lessons on technical writing and VLSI technology. He taught me physics of solid state devices by numerical problem solving and practice sessions. It is through his teaching, I learnt how to approach a problem, analyse results and gather my thoughts into a document. I feel immensely fortunate to have him as my teacher.

I thank Department of Science and Technology (DST), Government of India for funding my Ph.D. through INSPIRE fellowship (grant no. IF 120531). Simulation, fabrication and electrical characterisation reported in this work were carried out at the IIT Bombay Nanofabrication Facility (IITBNF), which is supported by the Ministry of Electronics and Information Technology, Government of India (grant no. 20(5)2005-Nano dt. 26.12.2005 and 5(2)/2010-NANO dt. 28.12.2011). Electron microscopy investigations were carried out at the Sophisticated Analytical Instrument Facility (SAIF), IIT Bombay which is supported by the Department of Science and Technology, Government of India.

I would like to express my sincere gratitude to my grandfather, Akhil Acharya, for creating the academic environment, in which future generations had the privilege of growing-up. His eccentric obsession of prioritising academic cultivation over prosperity, inspired me in difficult times. I would like to thank my father, Prof. Sankar Acharya, for instilling irrational positivity in me. I am also grateful for the countless sessions of english grammar lessons and proofreading he did for me.

I would like to thank my mother, Sudesna Acharya and my wife, Sayani Bose for their continuous support and encouragement.

## Contents

| Abstract            |                     |                 |                                                 |            |  |  |

|---------------------|---------------------|-----------------|-------------------------------------------------|------------|--|--|

| Ac                  | Acknowledgements iv |                 |                                                 |            |  |  |

| List of Figures vii |                     |                 |                                                 |            |  |  |

| Li                  | st of 7             | <b>[ables</b> ] | XV                                              | <b>/ii</b> |  |  |

| Li                  | st of A             | Abbrevi         | ations xv                                       | iii        |  |  |

| 1                   | Intro               | oductio         | n                                               | 1          |  |  |

| 2                   | Lite                | rature 1        | review                                          | 3          |  |  |

|                     | 2.1                 | An ove          | erview of silicon nanowire synthesis techniques | 3          |  |  |

|                     |                     | 2.1.1           | Top-down techniques                             | 3          |  |  |

|                     |                     | 2.1.2           | Solution based techniques                       | 5          |  |  |

|                     |                     | 2.1.3           | Silicon monoxide evaporation                    | 6          |  |  |

|                     |                     | 2.1.4           | Laser ablation                                  | 6          |  |  |

|                     |                     | 2.1.5           | Vapour-Liquid-Solid (VLS) method                | 7          |  |  |

|                     | 2.2                 | Growt           | n models                                        | 9          |  |  |

|                     | 2.3                 | Structu         | re of VLS grown nanowires                       | 12         |  |  |

|                     | 2.4                 | Applic          | ations of VLS grown nanowires                   | 14         |  |  |

|                     |                     | 2.4.1           | Templates                                       | 14         |  |  |

|                     |                     | 2.4.2           | Solar cells                                     | 14         |  |  |

|                     |                     | 2.4.3           | Lithium ion batteries                           | 16         |  |  |

|                     |                     | 2.4.4           | Thermoelectricity                               | 16         |  |  |

|                     |                     | 2.4.5           | Sensors                                         | 17         |  |  |

|   |      | 2.4.6 Targeted delivery into biological cells and tissues                      | 18 |

|---|------|--------------------------------------------------------------------------------|----|

|   | 2.5  | Discussion on the electrical properties of 'non-quantum' silicon nanowires     | 19 |

|   | 2.6  | Transport through silicon nanowires                                            | 22 |

| 3 | Exp  | erimental techniques                                                           | 26 |

|   | 3.1  | Cold-wall catalytic chemical vapour deposition (cat-CVD)                       | 26 |

|   | 3.2  | Scanning Electron Microscope (SEM)                                             | 28 |

|   | 3.3  | Transmission Electron Microscope (TEM)                                         | 30 |

|   | 3.4  | Selected Area (Electron) Diffraction (SAED)                                    | 31 |

|   | 3.5  | Energy-Dispersive X-ray spectroscopy (EDX)                                     | 32 |

|   | 3.6  | Electron Beam Lithography (EBL)                                                | 34 |

|   | 3.7  | Semiconductor device parameter analyser (Electrical characterisation)          | 35 |

|   | 3.8  | Technology computer aided design (TCAD)                                        | 38 |

| 4 | VLS  | growth of silicon nanowires in cold wall cat-CVD chamber                       | 40 |

|   | 4.1  | Introduction                                                                   | 40 |

|   | 4.2  | Details of experiment                                                          | 41 |

|   | 4.3  | Results and discussions                                                        | 43 |

|   | 4.4  | Effect of separation of the catalyst nanoparticles on the structure of the VLS |    |

|   |      | grown silicon nanowires                                                        | 48 |

| 5 | Stuc | ly of electrical transport through silicon nanowires                           | 52 |

|   | 5.1  | Introduction                                                                   | 52 |

|   | 5.2  | Experimental                                                                   | 54 |

|   | 5.3  | Transport models                                                               | 55 |

|   | 5.4  | Role of metal contact                                                          | 59 |

|   | 5.5  | Simulation                                                                     | 61 |

|   | 5.6  | Temperature dependent electrical characterisation                              | 67 |

|   | 5.7  | Conclusion                                                                     | 71 |

| 6 | Phys | sical origin of Poole-Frenkel transport in VLS grown silicon nanowires         | 72 |

|   | 6.1  | Introduction                                                                   | 72 |

|   | 6.2  | Physical characterisation                                                      | 74 |

|   | 6.3  | Effect of defects on transport                                                 | 79 |

|    | 6.4              | Conclusion                                          | 81 |  |

|----|------------------|-----------------------------------------------------|----|--|

| 7  | Con              | clusions and future work                            | 82 |  |

| Ap | opend            | ices                                                | 85 |  |

| A  | Met              | hods                                                | 86 |  |

|    | A.1              | Optimisation of catalyst nanoparticle formation     | 86 |  |

|    | A.2              | Silicon nanowire growth                             | 87 |  |

|    | A.3              | Physical characterisation                           | 88 |  |

|    | A.4              | Device fabrication                                  | 88 |  |

|    | A.5              | Device characterisation                             | 89 |  |

|    | A.6              | Details of simulation                               | 89 |  |

| B  | Cod              | es for simulation                                   | 90 |  |

|    | <b>B</b> .1      | Structure editor: to create the device structure    | 90 |  |

|    | B.2              | Device simulation: to obtain the IV characteristics | 92 |  |

| Bi | Bibliography 96  |                                                     |    |  |

| Pu | Publications 108 |                                                     |    |  |

## **List of Figures**

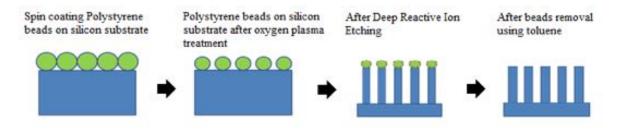

| 2.1 | Schematic diagram of simplified process flow of a typical nanosphere lithogra-       |              |

|-----|--------------------------------------------------------------------------------------|--------------|

|     | phy process                                                                          | 4            |

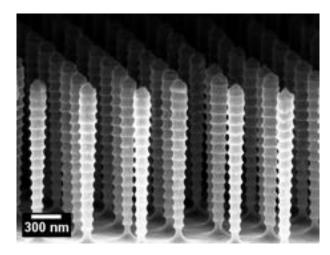

| 2.2 | $45^{\circ}$ tilted Scanning Electron Microscope (SEM) images of an array of silicon |              |

|     | nanowires synthesised by a top-down method similar to what is described in           |              |

|     | figure 2.1. The image is taken from the work of Raja Sekhar Baddula, CRNTS,          |              |

|     | IIT Bombay with permission from the author.                                          | 4            |

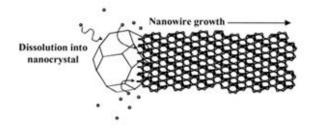

| 2.3 | Schematic diagram explaining silicon nanowire growth in solution phase. The          |              |

|     | figure is taken from reference [5].                                                  | 5            |

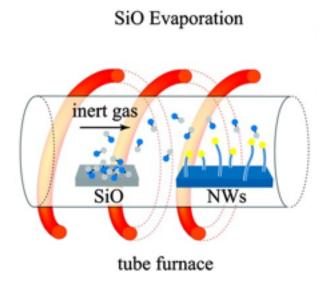

| 2.4 | Schematic diagram of silicon nanowire growth by silicon monoxide evaporation         |              |

|     | in a tube furnace. The figure is taken from reference [6].                           | 5            |

| 2.5 | Schematic digram of silicon nanowire growth process by laser ablation in a tube      |              |

|     | furnace. The figure is taken from reference [6].                                     | 6            |

| 2.6 | Schematic representation of silicon nanowire growth by VLS method. Image             |              |

|     | taken from Prof. Wei Cai's (Stanford university) blog (URL: http://imechanica.org/   | node/17430). |

| 2.7 | Schematic diagram for the understanding of the model proposed by Lu et al.           |              |

|     | Figure taken from reference [23]                                                     | 10           |

| 2.8 | (a) Schematic diagram of a silicon nanowire with hexagonal cross section and         |              |

|     | crystallographically defined sidewall facets. (b) Schematic diagram of a nanowire    |              |

|     | with three sawtooth faces. (c) TEM image of such a nanowire. The image is            |              |

|     | taken from reference [25]                                                            | 13           |

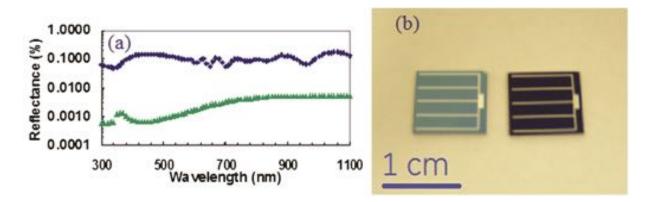

| 2.9 | (a) Specular reflectance, in log scale, of conventional solar cell (blue curve) and  |              |

|     | silicon nanowire solar cell (green curve). (B) Photographs of conventional solar     |              |

|     | cell (faint green) and silicon nanowire solar cell (dark blue). Figures taken from   |              |

|     | reference [34]                                                                       | 15           |

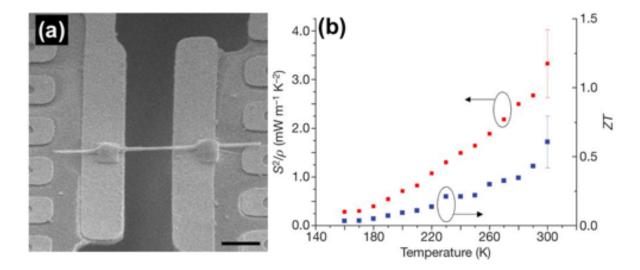

| 2.10 | (a) A silicon nanowire device made to study the thermoelectric performance of                                     |                   |

|------|-------------------------------------------------------------------------------------------------------------------|-------------------|

|      | the silicon nanowire. (b) Power factor, $S^2/\rho$ (red squares) and thermoelectric                               |                   |

|      | figure of merit ZT (blue squares) of a silicon nanowire of diameter 52 nm. The                                    |                   |

|      | figures are taken from reference [38]                                                                             | 16                |

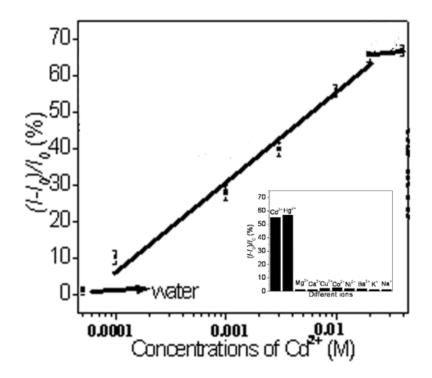

| 2.11 | Percentage change in current vs Cd <sup>2+</sup> concentration. Inset shows the selectivity                       |                   |

|      | of the sensor over different metal ions. The figure is taken from reference [46].                                 | 18                |

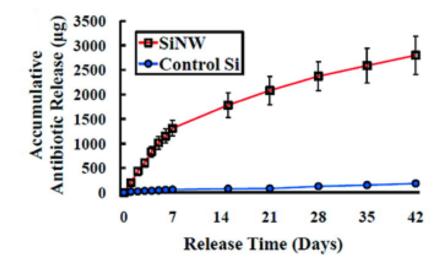

| 2.12 | Absolute release of penicillin + streptomycin solution plotted as a function                                      |                   |

|      | of sampling time. The average release amount is represented by the discrete                                       |                   |

|      | points. The figure is taken from reference [48].                                                                  | 19                |

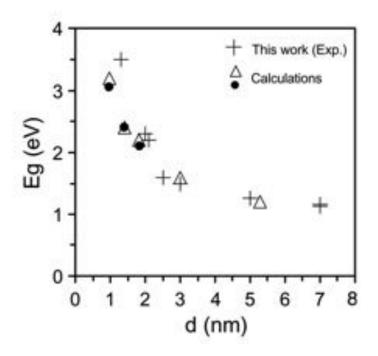

| 2.13 | Experimentally determined band-gap of ultrathin silicon nanowires. The figure                                     |                   |

|      | is taken from reference [29] in which the authors compared the results of their                                   |                   |

|      | experiment with mathematical models such as reference [52]                                                        | 20                |

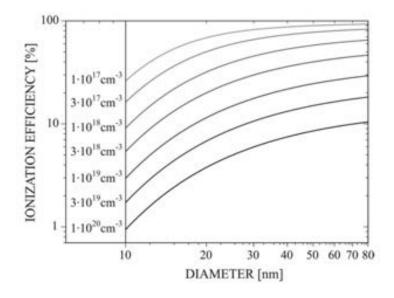

| 2.14 | Variation of impurity ionization efficiency with diameter of silicon nanowires.                                   |                   |

|      | Image taken from reference [54].                                                                                  | 21                |

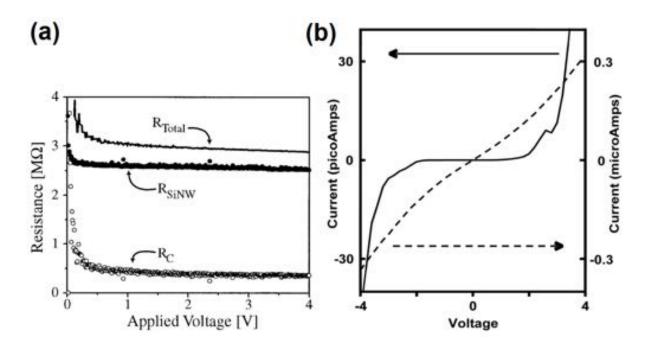

| 2.15 | (a) Comparison of contact resistance with resistance of silicon nanowire (which                                   |                   |

|      | is acting as channel). The graph is taken from reference [59]. (b) IV character-                                  |                   |

|      | istics of silicon nanowires (diameter 20 nm) contacted with Ti/Au electrodes,                                     |                   |

|      | before (solid) and after (dashed) annealing at 750°C for 1 hour. The graph is                                     |                   |

|      | taken from reference [60].                                                                                        | 23                |

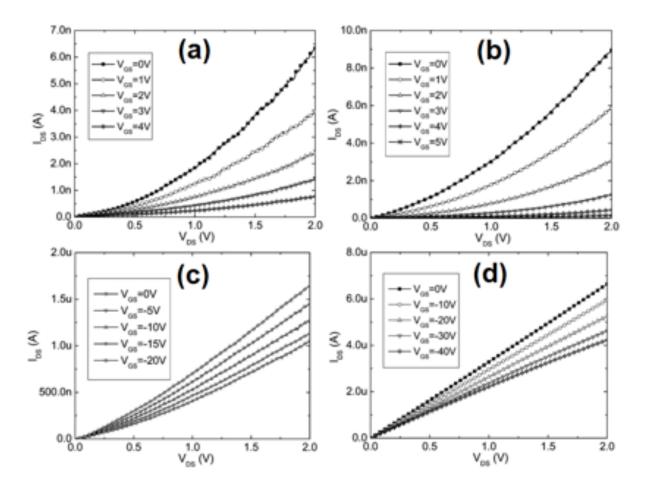

| 2.16 | Output characteristics of back-gated SiNWs grown with the following volumet-                                      |                   |

|      | ric ratios of dopant to precursor in the inlet gas to the process chamber. (a)                                    |                   |

|      | $[P:Si] = 0$ , (b) $2 \times 10^{-5}$ , (c) $7 \times 10^{-5}$ , and (d) $2 \times 10^{-4}$ . The plots are taken |                   |

|      | from reference [55]                                                                                               | 24                |

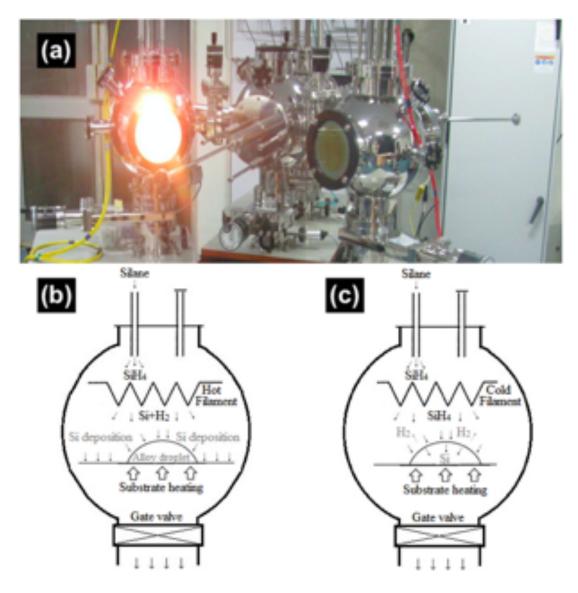

| 3.1  | (a) Photograph of the cat-CVD instrument used for the silicon nanowire growth                                     |                   |

| 5.1  | by VLS method. The image is taken from our laboratory website (URL: http://www                                    | an iith an inla   |

|      | (b) Schematic diagram explaining the tool's operation in HWCVD mode (glow-                                        | /.cen.ntb.ac.ni/c |

|      | ing reaction chamber in the photograph). (c) Schematic diagram of the tool's                                      |                   |

|      | operation in CVD mode (the right reaction chamber in the photograph)                                              | 27                |

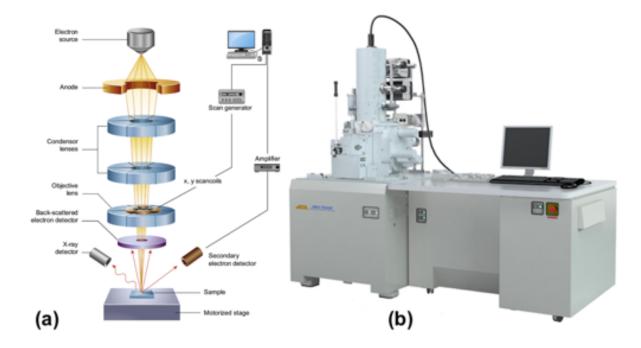

| 3.2  | (a) Schematic diagram exhibiting the operating principe of an SEM instrument.                                     | 21                |

| 5.2  | The figure is taken from reference [64]. (b) Photograph of the instrument used                                    |                   |

|      | in this work. The image is taken from the website of the manufacturer (URL:                                       |                   |

|      |                                                                                                                   | 28                |

|      | http://www.jeol.co.jp/en/products/detail/JSM-7600F.html).                                                         | 20                |

### ix

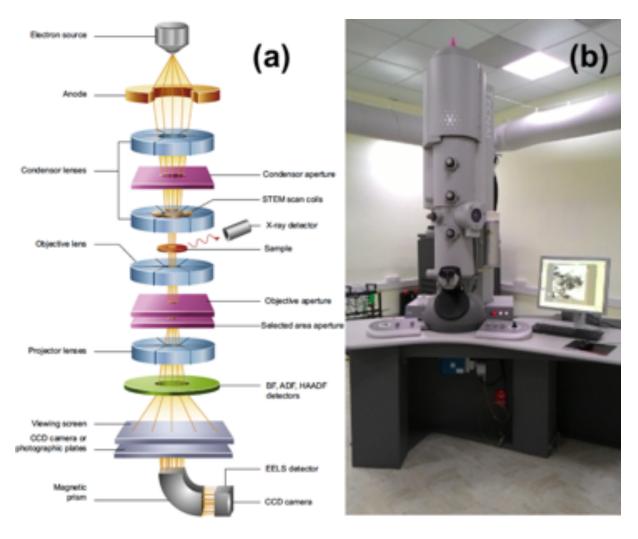

| 3.3                                           | (a) Schematic diagram exhibiting the operating principle of an TEM instrument.                                                                                                                                                                        |                 |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                                               | Figure taken from reference [64]. (b) Photograph of the instrument used in this                                                                                                                                                                       |                 |

|                                               | work. Image taken from IIT Bombay sophisticated analytical instrument facility                                                                                                                                                                        |                 |

|                                               | website (URL: http://http://www.rsic.iitb.ac.in/hr-tem300kv.html)                                                                                                                                                                                     | 31              |

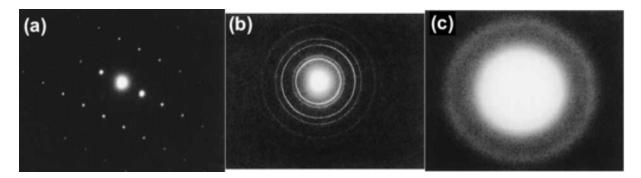

| 3.4                                           | (a) Electron diffraction pattern of a typical single crystalline sample. (b) Elec-                                                                                                                                                                    |                 |

|                                               | tron diffraction pattern of a polycrystalline sample. (c) Electron diffraction pat-                                                                                                                                                                   |                 |

|                                               | tern of a amorphous sample. Figures are taken from reference [65]                                                                                                                                                                                     | 32              |

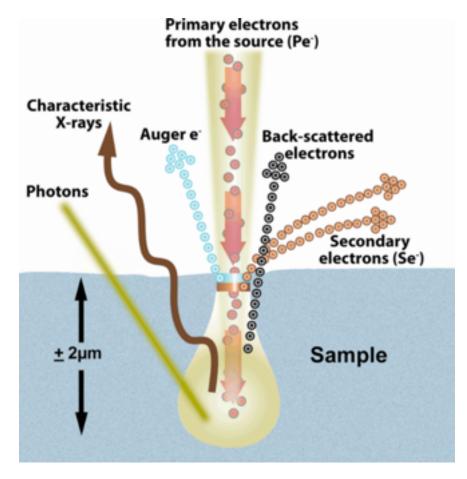

| 3.5                                           | A schematic diagram explaining important features of interaction of a high-                                                                                                                                                                           |                 |

|                                               | energy electron beam with a solid sample. The figure is taken from reference [66].                                                                                                                                                                    | 33              |

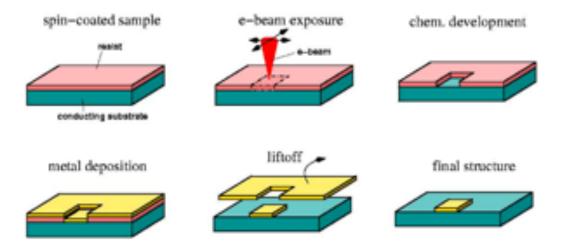

| 3.6                                           | A schematic diagram explaining contact formation using EBL and liftoff. The                                                                                                                                                                           |                 |

|                                               | figure is taken from Nano-Optics Group, Institute of Physics - Karl Franzens                                                                                                                                                                          |                 |

|                                               | University Graz website (URL: http://nanooptics.uni-graz.at/ol/work/m_ebl.html).                                                                                                                                                                      | 35              |

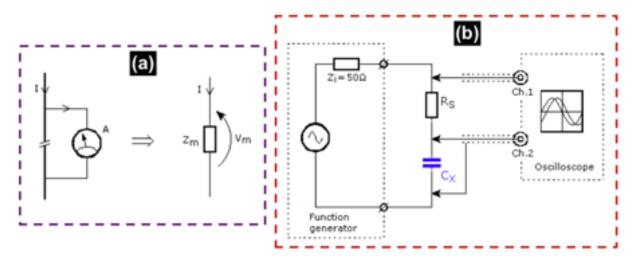

| 3.7                                           | Schematic diagram of (a) current measurement and (b) capacitance measure-                                                                                                                                                                             |                 |

|                                               | ment circuit. The figures are taken from Meettechniek website by Freddy Alferink                                                                                                                                                                      |                 |

|                                               | (URL: https://meettechniek.info/main.html)                                                                                                                                                                                                            | 36              |

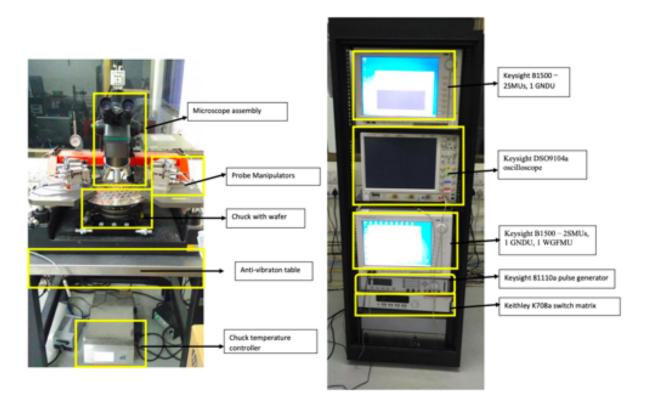

| 3.8                                           | Picture of one of the semiconductor device parameter analysers used in this                                                                                                                                                                           |                 |

|                                               |                                                                                                                                                                                                                                                       |                 |

|                                               | work. The figure is taken from our laboratory website (URL: http://www.cen.iitb.ac                                                                                                                                                                    | .in/slotbooking |

| 4.1                                           | work. The figure is taken from our laboratory website (URL: http://www.cen.iitb.ac<br>Binary phase diagram of gold and silicon. The figure is taken from reference [6].                                                                               | -               |

| 4.1<br>4.2                                    |                                                                                                                                                                                                                                                       | -               |

|                                               | Binary phase diagram of gold and silicon. The figure is taken from reference [6].                                                                                                                                                                     | -               |

|                                               | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon                                                                                      | -               |

|                                               | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in              | 41              |

| 4.2                                           | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode. | 41              |

| 4.2                                           | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41              |

| 4.2                                           | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41              |

| 4.2                                           | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42        |

| 4.2<br>4.3                                    | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42        |

| 4.2<br>4.3                                    | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42        |

| 4.2<br>4.3                                    | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42<br>43  |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42<br>43  |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Binary phase diagram of gold and silicon. The figure is taken from reference [6].<br>Schematic diagram of the indigenous cat-CVD instrument used to grow silicon<br>nanowires by VLS method (a) Operation in HWCVD mode (b) Operation in<br>CVD mode  | 41<br>42<br>43  |

Х

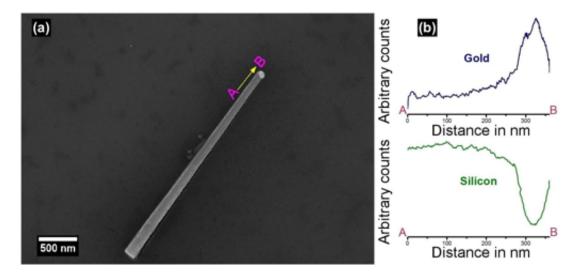

| 4.6  | (a) SEM image of a silicon nanowire transferred to $SiO_2$ substrate for physical      |    |

|------|----------------------------------------------------------------------------------------|----|

|      | characterisation. (b) Energy-dispersive X-ray spectroscopy results obtained by         |    |

|      | scanning from point A to point B. The blue curve indicates variation of gold           |    |

|      | concentration and the green curve indicates silicon concentration along the line-      |    |

|      | scan from A to B                                                                       | 45 |

| 4.7  | Transmission Electron Microscope image of a single silicon nanowire after VLS          |    |

|      | growth in CVD mode (inset shows the Electron Diffraction pattern of the same           |    |

|      | nanowire).                                                                             | 46 |

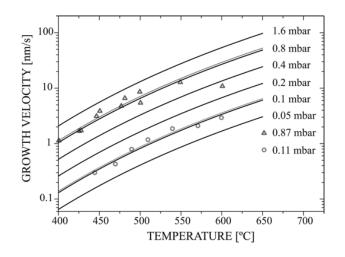

| 4.8  | Dependence of gold catalysed silicon nanowire growth rate on temperature and           |    |

|      | pressure. The discrete data points indicate experimental results. The figure is        |    |

|      | taken from reference [6].                                                              | 47 |

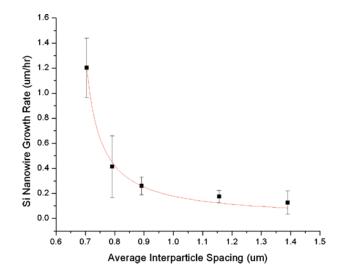

| 4.9  | Plot comparing the Si nanowire growth rate vs the average inter-particle spac-         |    |

|      | ing. Error bars in the y-direction were determined from the standard deviation         |    |

|      | of wire lengths in each SEM image taken at the corresponding spacing. The              |    |

|      | figure is taken from reference [18]                                                    | 48 |

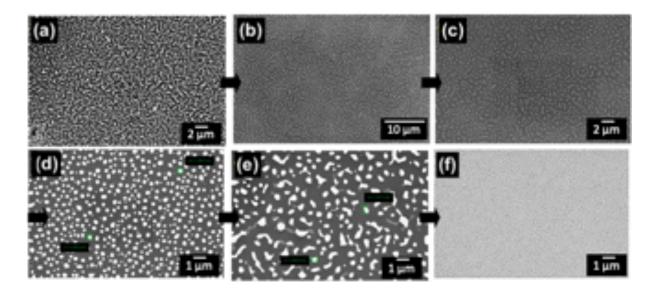

| 4.10 | (a-c) SEM images of the substrates with patterned resist on top. The average           |    |

|      | distance between the features are, (a) 4.6 $\mu$ m, (b) 800 nm and (c) 250 nm. (d-f)   |    |

|      | SEM images of the substrates after gold deposition and lift-off. The average           |    |

|      | distance between the gold pads are, (d) 4.6 $\mu$ m, (e) 800 nm and (f) 250 nm.        |    |

|      | (g-i) 45 $^{\circ}$ tilted Scanning Electron Microscope images of the substrates after |    |

|      | VLS growth of silicon nanowires. The average distance between the silicon              |    |

|      | nanowires are, (g) 4.6 $\mu$ m, (h) 800 nm and (i) 250 nm                              | 49 |

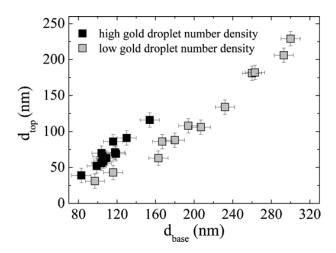

| 4.11 | Measurement of the diameters of VLS grown silicon nanowires at the top $d_{top}$       |    |

|      | vs at the bottom $d_{base}$ . The figure is taken from reference [70]                  | 50 |

| 5.1  | (a) IV characteristics of a silicon nanowire device. Inset: the IV characteris-        |    |

|      | tics for a larger voltage range. The figure is taken from reference [63]. (b) IV       |    |

|      | characteristics of a silicon nanowire device before (top) and after (bottom) an-       |    |

|      | nealing at 550 °C. The figure is taken from reference [60]. (c) Current-voltage        |    |

|      | characteristics of a silicon nanowire device measured using two terminal (green        |    |

|      | curve) and four terminal (red curve) measurement. The figure is taken from             |    |

|      | reference [57]                                                                         | 53 |

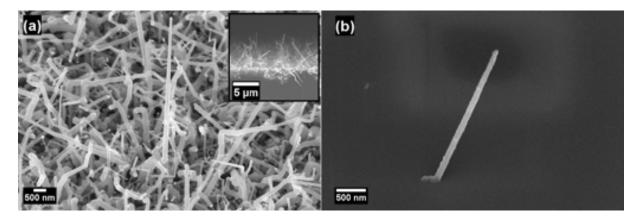

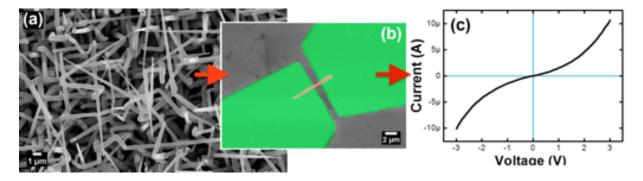

5.2 (a) 45° tilted SEM image of the substrate after VLS growth of silicon nanowires.

(b) SEM image of a test structure made after transferring the VLS grown silicon nanowires to oxide substrate and metal contact formation using lithography. The nanowire is marked in transparent red and the Ti/Au contacts in transparent green. (c) Current-voltage characteristics of the silicon nanowire device shown in (b).

54

56

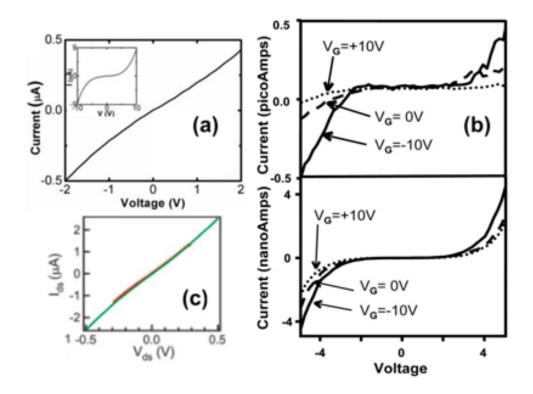

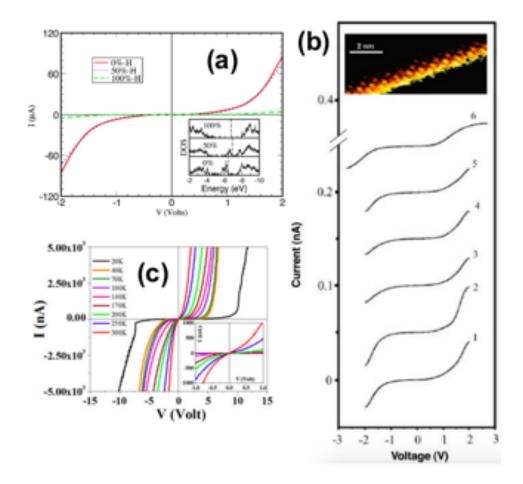

- 5.3 (a) Inverse-'S' like IV characteristics obtained by numerical calculations. The figure is taken from the work of Ponomareva et al. [53]. The inset shows the effect of unsaturated bonds on the surface of the nanowire on its density of states. (b) Inverse-'S' like IV characteristics obtained by STS measurements of very thin nanowires. Diameters of wires, marked with 1 to 6, are 7, 5, 3, 2.5, 2, and 1.3 nm, respectively. The figure is taken from the work of Ma et al. citeDDDMa. (c) Inverse-'S' like IV characteristics obtained from silicon nanowire metal-semiconductor-metal devices. The figure is taken from the work of Samanta et al. [82]. Inset exhibits the same characteristics for lower voltages.

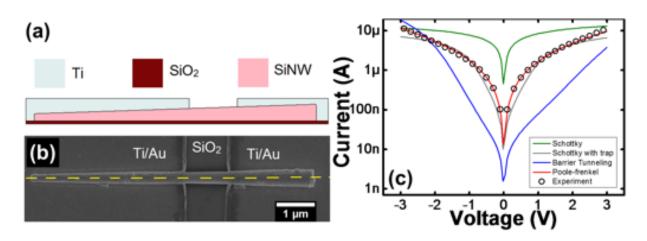

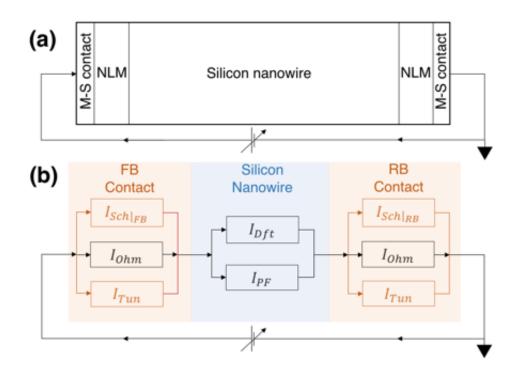

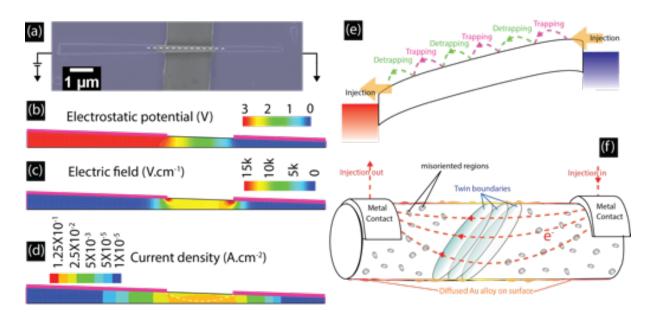

- 5.4 (a) The structure used in simulator. (b) SEM micrograph of the fabricated device. The structure for simulation is obtained by taking a 2D cut along the yellow dashed line to have smaller computation time. (c) Comparison of simulation and experimental results. Open circles represent experimental data. The green and grey lines are simulation result considering Schottky model without and with traps, red line is for Poole-Frenkel model, and blue line is for barrier tunneling at metal-semiconductor contact.

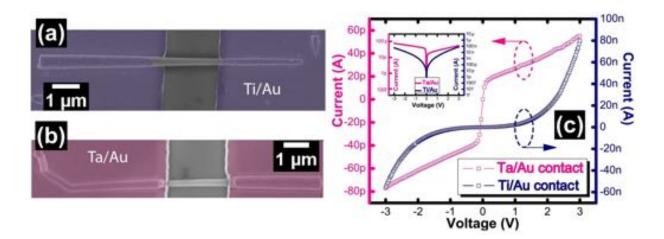

- 5.6 (a) SEM image of a silicon nanowire device with Ti/Au contacts. (b) SEM image of a silicon nanowire device with Ta/Au contact. The devices shown in (b) and (c) are almost identical in dimensions. Both nanowires are 9.5μm long. Both devices have a channel length of 2.2μm. Mean diameter of both nanowires in the channel region is around 250 nm. (c) IV characteristics obtained from the two devices. Magenta curve is obtained with Ta/Au contacts and blue curve is obtained with Ti/Au contacts. Inset exhibits these curves in log scale.

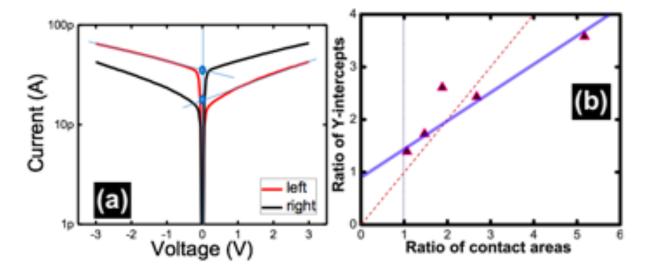

- (a) Reversibility of the IV characteristics of the device shown in figure 5.6(b). The red curve is obtained by applying potential to the left metal contact and connecting ground to the right terminal. The black curve is obtained by applying potential to the right metal contact and connecting ground to the left terminal.

(b) Ratio of the intercepts (blue circles in (a)) vs the ratio of the contact areas of several devices. Slope of the red dashed line is = 1 and slope of the blue line is = 0.5.

59

60

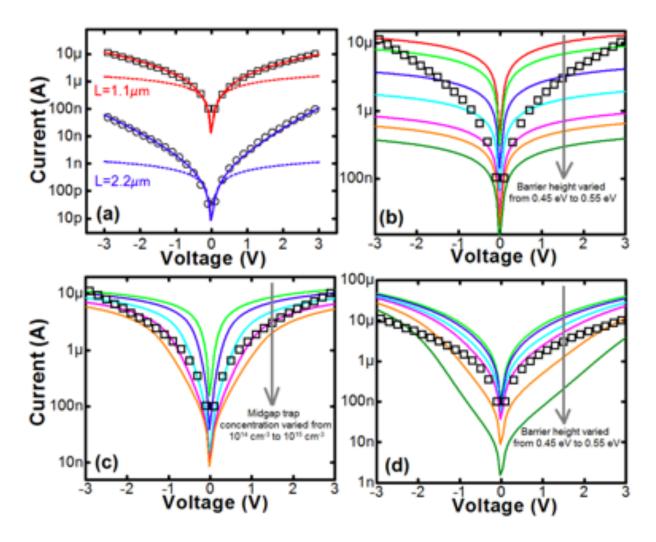

5.8 (a) IV characteristics in log scale. The red curves are for nanowire devices with channel length of 1.1 μm and blue curves for channel length of 2.2 μm. Solid lines represent simulation results obtained by adopting Poole-Frenkel transport model for the nanowire channel. Dotted lines present the results of exact same simulation except Poole-Frenkel model. Discrete points (hollow squares and circles) represent experimental results. (b) Comparison of simulation results for silicon nanowire device with channel length of 1.1 μm with experimental results (hollow squares) when Schottky contacts are assumed for Ti-Si contacts.

(c) Same as (b) with addition of mid-gap traps. (d) Same as (b) except when WKB based barrier tunneling models are assumed for Ti-Si contacts.

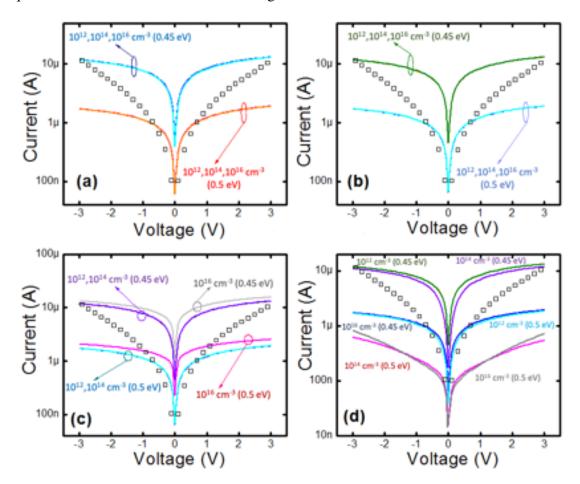

- 5.9 Effect of trap distribution on simulation results assuming Schottky model for Ti-Si contacts. (a) For exponential distribution of eNeutral traps spanning 0.1 eV from peak at conduction band minima. (b) For exponential distribution of hNeutral traps spanning 0.1 eV from peak at valance band maxima. (c) Considering the effect of (a) and (b) simultaneously. (d) Gaussian distribution of eNeutral traps spanning 0.1 eV from its peak at an energy 0.275 eV below conduction band minima together with Gaussian distribution of hNeutral traps spanning 0.1 eV from its peak at an energy 0.275 eV below conduction band minima together with Gaussian distribution of hNeutral traps spanning 0.1 eV from its peak at an energy 0.275 eV above valance band maxima. In all four cases (a)-(d), capture cross section of electrons and holes are considered as  $10^{-12} cm^{-2}$ . Barrier lowering due to image charge is considered. The metal-silicon contact barrier height used for each simulation is given within braces.

65

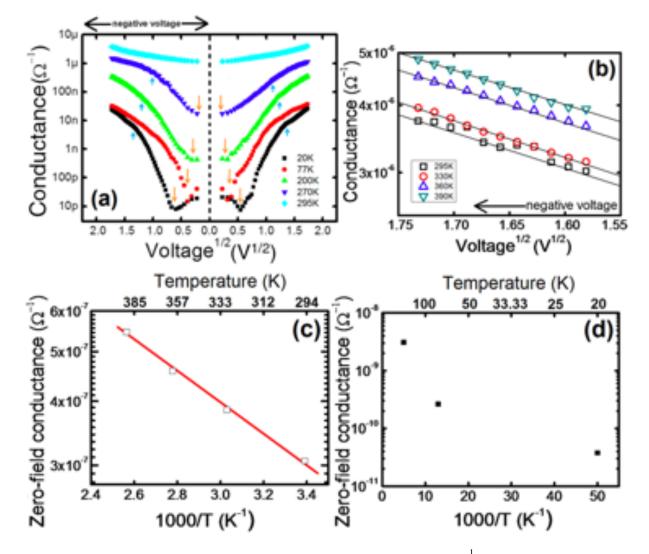

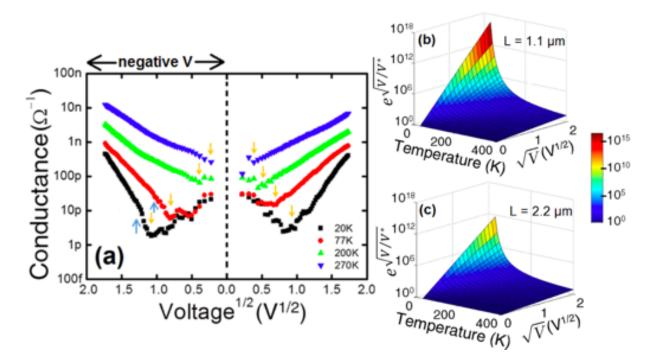

- 5.11 (a) Low temperature conductance vs  $V^{\frac{1}{2}}$  characteristics of a long channel (2.2  $\mu$ m) silicon nanowire device. (b) Plot of voltage exponent of the Poole-Frenkel expression with respect to temperature and  $\sqrt{V}$  for the device with channel length of 1.1  $\mu$ m. (c) Same plot for device with channel length of 2.2  $\mu$ m. . . . 69

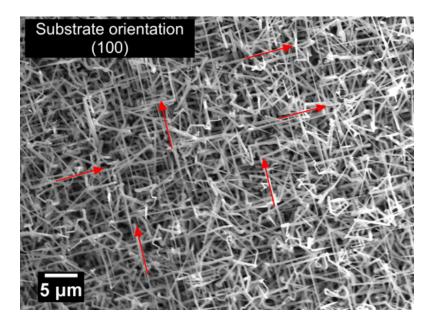

- 6.1 Planer Scanning Electron Microscope (SEM) image of a silicon (100) substrate after silicon nanowire growth. The red arrows indicate equivalent (111) directions. 75

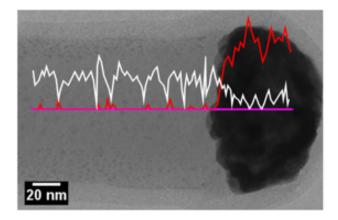

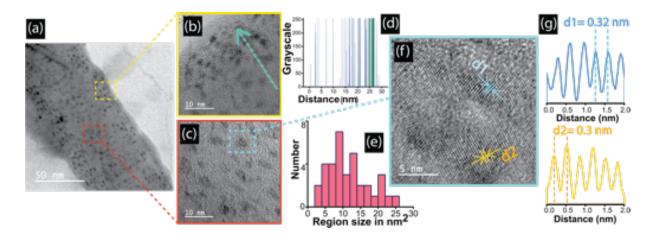

- 6.2 (a) TEM image of a gold catalysed, VLS grown silicon nanowire. Dark patches are visible on the nanowire. (b) The region inside the dashed yellow square in (a) at a higher magnification. (c) The region inside dashed orange square in (a) at a higher magnification. (d) A scan along the dashed cyan arrow showing how the frequency of the dark patches increases when moving towards the shell of the nanowire. In this graph, a spike in grayscale represents presence of a dark patch as the image is vectorised and inverted before taking this measurement.

(e) Size distribution of the dark patches in (c). (f) HRTEM of the region inside the dashed sky blue square in (c) showing that the patches in images a-c appear due to the local presence of crystallographic misorientation on an otherwise single crystal silicon nanowire. (g) Scan showing the presence of two different d-spacing (d1 and d2) in HRTEM.

76

77

77

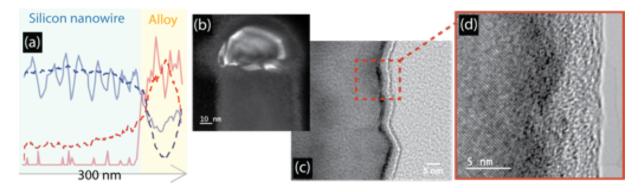

6.4 (a) EDX line-scan from FESEM and TEM of the VLS grown silicon nanowires. The dashed blue curve represents silicon concentration obtained from FESEM tool with an accelerating voltage of 20 kV. The same obtained from TEM with accelerating voltage of 200 kV is represented by the solid blue line. The dashed red curve represents gold concentration obtained from FESEM tool with 20 kV and the same obtained by 200 kV TEM is represented by the solid red line. The regions from which the data is taken are marked by the hues. Sky blue region represents the silicon nanowire and yellow tint represents the alloy nanoparticle on top of it. (b) Dark field TEM image near the tip of the silicon nanowire. The bright hemisphere on top of the nanowire is the catalyst nanoparticle. (c) TEM image exhibiting the sawtooth faceting of the nanowires. The native oxide shell of the nanowire can be seen in this image. A dark region can be seen just below the native oxide. (d) The region inside the dashed brick red square in (c) in higher magnification.

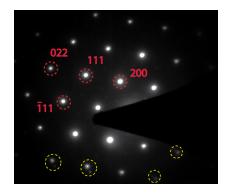

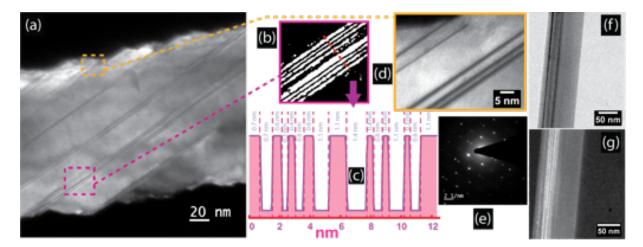

6.5 (a) Dark field TEM image of a silicon nanowire showing multiple twin boundaries spanning as diagonals on silicon nanowires. (b) Vectorised image for analysis from the region inside the dashed magenta square in (a). (c) Line scan along the dashed red line in (b) to investigate the periodicity of the defects. (d) The region inside dashed yellow square in (a) in higher magnification. One of the twin boundaries can be seen to terminate before reaching the shell of the nanowire in this image. (e) Electron diffraction showing patterns from a region with twin boundaries. (f) Axial twin bounderies spanning throughout the length of silicon nanowire. (g) The image of (f) in dark field and in slightly higher magnification.

78

## **List of Tables**

5.1 Models used in TCAD simulations. Colours refer to those used in figure 5.4(c). 58

## List of abbreviations

| CVD   | Chemical vapour deposition                  |

|-------|---------------------------------------------|

| EBL   | Electron Beam Lithography                   |

| EDX   | Energy-dispersive X-ray spectroscopy        |

| FECA  | Foreign Element Catalytic Agent             |

| FESEM | Field emission scanning electron microscope |

| HWCVD | Hot wire chemical vapour deposition         |

| IV    | Current-voltage                             |

| LPCVD | Low pressure chemical vapour deposition     |

| PECVD | Plasma-enhanced chemical vapour deposition  |

| PF    | Poole-Frenkel                               |

| SEM   | Scanning electron microscope                |

| SAED  | Selected area (electron) diffraction        |

| ТВ    | Twin boundary                               |

| TCAD  | Technology computer aided design            |

| TEM   | Transmission electron microscope            |

| VLS   | Vapour-liquid-solid                         |

### Chapter 1

### Introduction

Research on novel semiconductor devices is one of the important frontiers of modern science and technology. The improvement of semiconductor device technology, in terms of cost and performance, in last few decades, has impressed consumers and researchers alike. However, many experts believe that this rate of improvement will not be sustainable for the years to come, unless researchers keep on exploring new materials and technologies to improve the collective knowledge. This will increase the possibility for a paradigm shift. In this work, a material with potential application in making future electronic devices and interconnects is studied. Even though there are plenty of work in past which reported several aspects of the material, we have reasons to believe that the characteristics of the material is not completely understood.

Silicon nanowires are a type of nanostructure. They usually refer to rod shaped crystals of silicon, with diameter in the nanometer range. Publications throughout the last two decades exhibit its usefulness in making sensors and other electronic devices. Arrays of silicon nanowires can also be used as templates or as a light trapping layer to enhance the efficiency of solar cells. Even though all these applications of silicon nanowires have been explored relatively recently, the research on silicon nanowires started more than half a century ago. The first report on silicon nanowire (formerly termed as whiskers) is dated 1957 by Treuting and Arnold [1]. This unusual discontinuity between the discovery of the material and gaining recognition as a substance with application, can be attributed to the lack of demand of such a material in the decades in-between, in general. With the advancement of microelectronics and semiconductor fabrication technologies, and synthesis of silicon nanowires of nanoscale diameter by Morales and Lieber in 1998 [2], the scenario changed quite a lot. The development of "bottom-up" technology, in which nanostructures like silicon nanowires are assembled atom-by-atom from

their fundamental components, elevated research in silicon nanowires to a completely new level. Traditional "top-down" technology, in which materials in bulk form are shaped down to make nanostructures by removing excess material, fell short of high-yield production of nanoscale materials. One dimensional structures and alternative materials, such as carbon nanotubes, demanded a massive alteration of the existing technology.

This work provides an in-depth study of several steps of making silicon nanowire devices. A study of previous literature is presented in chapter 2, followed by an overview of the experimental techniques used for this work in chapter 3. In chapter 4, the most versatile and promising method of silicon nanowire growth, the vapour liquid solid (VLS) growth, is studied in detail. It has also been vividly documented, how, using a simple, low-cost reactor, good quality silicon nanowires can be produced. The grown silicon nanowires are used to fabricate test devices. After that, by specially designed study of electrical characteristics of the nanowires, the dominant mode of charge carrier transport through them is determined. The goal was to find out whether using VLS method for growth induces any characteristic peculiarity in these nanowires. It has been found, for the first time, that the current through the VLS grown silicon nanowires are dominated by Poole-Frenkel (PF) transport. The results are presented in chapter 5. Previous works missed this because of the nature of doping and contact formation of the nanowires. The onset of the phenomenon is experimentally demonstrated with electrical characteristics, and through rigorous physical characterisation and simulations. The physical origin of the transport (PF) is explained in chapter 6. We believe, this document would aid future researchers to develop functioning electronic devices, sensors or interconnects using silicon nanowires, as they can either intentionally make silicon nanowire devices within PF dominated regime, or out of it.

### Chapter 2

### Literature review

### 2.1 An overview of silicon nanowire synthesis techniques

Many techniques to synthesise silicon nanowires have been discovered and studied in the last five decades. The abundance of growth techniques actually stems from the diversity of applications, because a particular growth technique is useful for only a handful of applications. Different techniques of silicon nanowire growth can be roughly divided into two categories. 'Top-down', in which bulk silicon is turned into nanowires by removing excess materials. 'Bottom-up', in which nanowires are made by self-assembly of individual atoms or clusters of atoms. The top-down approach to growth is usually preferred for photovoltaic applications to make arrays of silicon nanowires for light trapping. Bottom-up technique is more useful for microelectronic applications such as nanowire transistors. Keeping the plethora of available growth techniques in mind, only the most commonly used growth techniques are discussed here. The physical and chemical etching based techniques are discussed under the name- top-down techniques. Followed by short discussions on bottom-up techniques such as, solution based techniques, silicon monoxide evaporation, laser ablation, and VLS method.

#### **2.1.1** Top-down techniques

Top-down techniques for silicon nanowire synthesis mostly rely on lithography and etching processes. One of the most commonly used top-down techniques is Langmuir-Blodgett assembly and etching [3]. In this, nanosphere lithography is used to make array of vertical nanopillars of silicon. This is then oxidised to make silicon nanowires. A typical process flow is de-

Figure 2.1: Schematic diagram of simplified process flow of a typical nanosphere lithography process.

Figure 2.2:  $45^{\circ}$  tilted Scanning Electron Microscope (SEM) images of an array of silicon nanowires synthesised by a top-down method similar to what is described in figure 2.1. The image is taken from the work of Raja Sekhar Baddula, CRNTS, IIT Bombay with permission from the author.

scribed with the help of schematic diagrams in figure 2.1. Figure 2.2 exhibits an array of silicon nanowires on silicon substrate, fabricated using a process similar to what is described in figure 2.1. However, to obtain horizontal nanowires, an approach other than nanosphere lithography has to be used. One such method is performing electron-beam lithography (EBL) with silicon-on-insulator (SOI) wafers [4]. This produces silicon nanowires parallel to the buried silicon surface. A major disadvantage of using top-down method is creation of surface defects. Since, in this process, the desired geometry is obtained by aggressive processing and removal of materials. Often times, this leads to a high number of defects on the surface. To counter this effect, nanowires synthesised using this method are advised to be passivated before use.

#### 2.1.2 Solution based techniques

Solution based techniques are also referred to as supercritical fluid based techniques. In this method, a liquid silicon precursor is used along with a highly pressurised supercritical organic fluid. This fluid contains the catalyst. To synthesise silicon nanowires, silicon diffuses through the surface of the catalyst to initiate one-dimensional growth [5]. In this method, silicon nanowires are grown suspended in a solution rather than attached to a growth substrate. This has several advantages, such as physical characterisation. There are disadvantages as well, such as growth without a substrate limits these nanowires' usability in several applications like photovoltaics.

Figure 2.3: Schematic diagram explaining silicon nanowire growth in solution phase. The figure is taken from reference [5].

Figure 2.4: Schematic diagram of silicon nanowire growth by silicon monoxide evaporation in a tube furnace. The figure is taken from reference [6].

#### 2.1.3 Silicon monoxide evaporation

This method requires a rather complex setup. A tube furnace is heated with multi-zone external heating elements. In which silicon monoxide (SiO) is kept on the hottest zone of the furnace. A steady flow of inert gas needs to be monitored from the hotter parts to the colder parts of the furnace. This allows the SiO to evaporate and get carried by the inert gas flow towards the colder zones. In the colder zones of the tube furnace, the evaporated SiO undergoes a disproportionation reaction to form Si and SiO<sub>2</sub>. This reaction results in silicon nanowires with an oxide shell [7]. Nanowires grown by this method have less surface defects as the surface is passivated by the oxide shell. However, for many applications, this brings extra complexity. In order to establish electrical contact with the nanowires, one has to remove the shell either locally or completely.

#### 2.1.4 Laser ablation

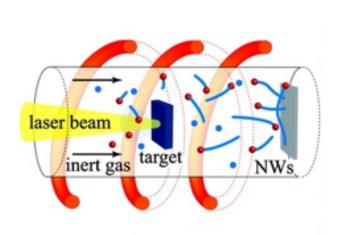

Figure 2.5: Schematic digram of silicon nanowire growth process by laser ablation in a tube furnace. The figure is taken from reference [6].

A striking characteristic of growth of silicon nanowires by laser ablation technique is that the actual growth of silicon nanowires happens in the gas phase. A target is prepared by fusing silicon and a catalyst material together in proper ratio. This is then kept inside a tube furnace. The furnace is heated before the pulsed laser hits the prepared target and elevated temperature is maintained throughout the process. At this point, the laser ablates silicon-catalyst alloy particles from the target in the heated tube. These particles are carried by a flow of inert gas to the other end of the tube where a substrate is placed. As the inert gas carries the ablated alloy particles far from the target, the particles condense to form liquid droplets. These droplets then initiate growth of silicon nanowires. The nanowires collected on a substrate usually have a crystalline core and amorphous shell [2]. When invented, this method revolutionised research in silicon nanowires. The first truly 1-D nanowires (diameter less than 10 nm) were grown using this method.

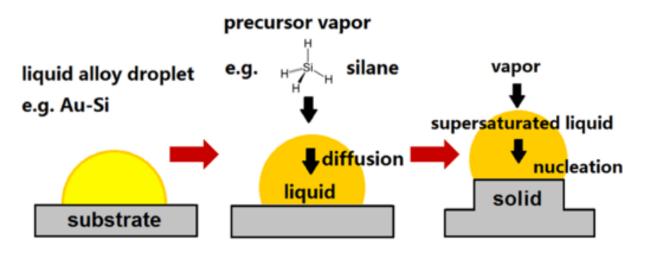

#### 2.1.5 Vapour-Liquid-Solid (VLS) method

Since its invention in 1964 by Wagner and Ellis [8], the VLS (Vapour-Liquid-Solid) method of nanowire synthesis has been heavily studied. The interest is mainly because of the fact that this method can be used for a wide range of process conditions. As a result, nanowires with different physical properties and dimensions can be produced with repeatability [6]. Considering the diversity of applications of silicon nanowires [9], it is not surprising that such a method would become widely used. The name, VLS growth, came from the trail of the element silicon during the growth process. In this process, the silicon from the gaseous precursor (vapour) diffuses through an eutectic alloy droplet (liquid) until gets crystallised and finally forms nanowire (solid) [8]. Usually the process takes place inside a Chemical Vapour Deposition (CVD) system. A silicon rich, oxygen free, gas supplies silicon to the CVD chamber. Typical choices of the precursor gas are silane (SiH<sub>4</sub>), disilane (Si<sub>2</sub>H<sub>6</sub>), dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>), and tetrachlorosilane (SiCl<sub>4</sub>). The growth conditions depend on the selection of the precursor gas. For example, VLS growth using tetrachlorosilane (SiCl<sub>4</sub>) as a precursor gas necessitates a process temperature from about 800°C [10] to well beyond 1000°C [11]. On the other hand, VLS growth using silane as a precursor gas requires only 400 - 600 °C [12]. This is because of the difference in the activation energy required to dissociate each precursor. There are other effects to be considered as well. Using chlorinated precursor results in etching of the substrate as well as the wall of the reaction chamber. Depending on the aim of the experiment, this could be desired or unacceptable.

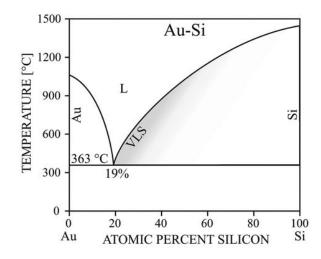

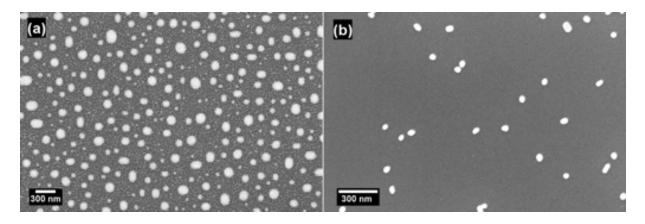

The VLS method requires a Foreign Element Catalytic Agent (FECA) for nanowire growth. An FECA is a metal, capable of forming eutectic alloy with silicon, below the VLS growth temperature. The most frequently used FECA in published literature is gold [12]. A close look at the binary phase diagram [6] of gold and silicon reveals the fact that the binary phase of silicon and gold is of simple eutectic type. It is characterised by a single eutectic point at 363 °C. When

Figure 2.6: Schematic representation of silicon nanowire growth by VLS method. Image taken from Prof. Wei Cai's (Stanford university) blog (URL: http://imechanica.org/node/17430).

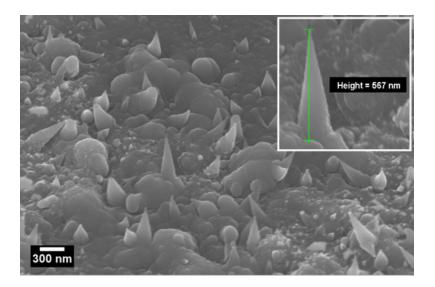

a silicon wafer, containing gold thin film or gold nanoparticles on top, is heated over 363 °C, liquid Au-Si eutectic droplets form in a silicon-abundant environment. These liquid droplets act as FECA during VLS growth of silicon nanowires. But the process needs even higher temperature for dissociation of the precursor gas. This precursor gas dissociates on the surface of the FECA into solid silicon and a gaseous byproduct. This results in supersaturation of silicon inside the eutectic droplet, followed by crystallisation of silicon at the FECA-substrate interface. The silicon nanowire grows with the FECA droplet on the top if steady supply of precursor gas is maintained. The diameter of the growing nanowire becomes equal to that of the liquid droplet. This process is exhibited schematically in figure 2.6. In this study, gold is used as FECA for simplicity of optimisation and abundance of available literatures to compare the results with.

As mentioned earlier, this process is heavily optimised and studied ever since its discovery for quite a few precursor gases and FECA [6]. These experiments have resulted in silicon nanowires which are diverse in geometry and physical properties. This, to a large extend, can be attributed to the choice of the equipment used for the process as well. The equipments range from Low-Pressure Chemical Vapour Deposition (LPCVD) [13], Plasma-Enhanced Chemical Vapour Deposition (PECVD) [14] to tube furnaces [15]. Sometimes more complicated systems like Transmission Electron Microscope with integrated CVD process [16], Molecular-Beam Epitaxy (MBE) [17] or Metal-Organic Chemical Vapour Deposition reactor (MOCVD) [18] are also being used to carry out VLS growth of silicon nanowires. In this work, a rather simple, and indigenous, instrument has been used to grow silicon nanowires by VLS method. The results

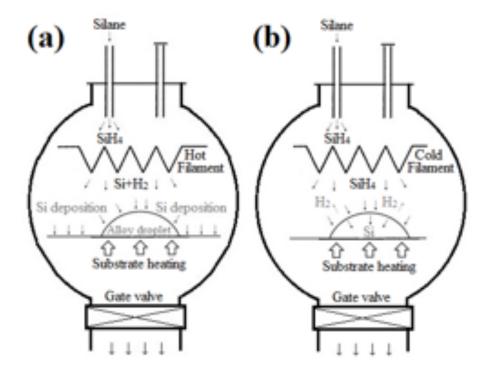

are presented in chapter 4. The instrument is a Cold Wall cat-CVD with spherical reaction chambers. We believe this to be quite significant for mass production. This instrument clearly brings down the complexity of the equipment needed for VLS growth process. The thermal budget is significantly lower than traditional VLS process, where the entire process chamber is heated up to the growth temperature. As a result, the cost to produce VLS grown silicon nanowires should go down significantly, if this method is implemented.

### 2.2 Growth models

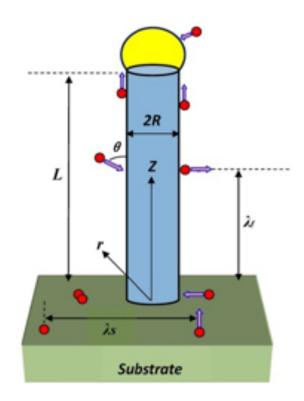

In last five decades of silicon nanowire research, attempts of modelling the VLS growth has been quite scarce compared to the bountiful reports of experiments. It can be said that the quantitative understanding of the growth process is still evolving. Over the years, the concepts have been rethought many times with the insights created by experimental results. Bootsma et al. [19] attempted to model VLS growth in 1971. According to their understanding, VLS growth was controlled by a single activation step. The conclusion was that, the decomposition of the gaseous precursor at the vapour-liquid interface is the controlling step for growth rate. The concepts reached a dialectical phase in 1975, when Givargizov et al. [11] claimed that the nucleation at the solid-liquid interface to be the defining step for growth rate. This disagreement continued untill recent times as well [20]. A new epoch of understanding started when Schmidt et al. [21] and Dubrovskii et al. [22] applied the steady state hypothesis to nanowire growth. They proposed that, for a growth mechanism involving a series of steps, it is feasible to not have a single rate defining step. In our work, we chose to explicate the VLS growth of silicon nanowires using the model of Lu et al. [23]. The choice is made based on correctness and simplicity of the model. Conventionally, the VLS growth process is divided roughly into the following four steps: (i) supply of precursor material to the vapour phase, (ii) reaction at the vapour-liquid droplet interface, (iii) diffusion of the species through the liquid FECA and (iv) crystallisation at the liquid droplet - solid substrate interface. But Lu et al. [23] have divided the transport of the material, contributing to the nanowire growth, into three kinetic parts: (i) 'Direct effective impingement of deposit atoms on the catalyst liquid droplet', (ii) 'Diffusion of the atoms that hit the sidewall area of the NW at an incident angle  $\theta$ ' and (iii) 'Diffusion flux of adatoms from the substrate surface toward the droplet along the nanowire sidewalls'. The model is based on two steady-state diffusion equations. One describing the diffusion of the

Figure 2.7: Schematic diagram for the understanding of the model proposed by Lu et al. Figure taken from reference [23].

adatoms on the substrate surface and the other describing the diffusion of the adatoms on the nanowire sidewall. These equations describing the adatom flux are continuous at the base of the growing silicon nanowires. The adatoms concentration on the substrate surface,  $n_s$  should satisfy the following equation:

$$\frac{\partial n_s}{\partial t} = D_s \nabla^2 n_s - \frac{n_s}{\tau_s} + J \cos\theta$$

(2.1)

Where  $D_s$  is the diffusion coefficient of adatoms on the substrate surface.  $\tau_s$  is the average time, an adatom spends on the substrate surface, before deposition, J is the impinging flux of adatoms from the vapour phase and  $\nabla^2$  is the 2D Laplace vector. Similarly the adatoms concentration on the sidewall of nanowires,  $n_f$  should satisfy the following equation:

$$\frac{\partial n_f}{\partial t} = D_f \frac{\partial^2 n_f}{\partial^2 z} - \frac{n_f}{\tau_f} + J \sin\theta$$

(2.2)

Where  $D_f$  is the diffusion coefficient of adatoms on the nanowire sidewall and  $\tau_f$  is the average time, an adatom spends on the nanowire sidewall, before deposition. In order to achieve steady

state  $(\frac{\partial n_s}{\partial t} = 0)$  solution for equation (2.1), we may assume the boundary condition  $n_s(R) = 0$ , where R is the radius of the growing nanowires. Finally, the solution can be expressed in terms of the modified Bessel function of the second kind,  $K_0(x)$ .

$$n_s(r) = R_s \tau_s \left[ 1 - \frac{K_0(\frac{r}{\lambda_s})}{K_0(\frac{R}{\lambda_s})} \right]$$

(2.3)

Here,  $\lambda_S = \sqrt{D_s \tau_s}$ , is the diffusion length of the adatoms at the substrate surface. This solution is valid only if the separations of the adjoint nanowires are very large. Using an analogous approach the steady state solution for equation (2.2) can be achieved using the following boundary conditions.  $\left[D_s \frac{\partial n_f}{\partial r}\right]_{r=R} = \left[-D_f \frac{\partial n_f}{\partial z}\right]_{z=0}$  at the bottom of the nanowires and  $[n_f]_{z=L}$  at the top of the nanowires. Where, L is the length of the growing silicon nanowires. The solution can be expressed as,

$$n_f = J\tau_f \sin \theta \left[ 1 - \frac{\cosh(\frac{z}{\lambda_f})}{\cosh(\frac{L}{\lambda_f})} \right] + \frac{\lambda_f}{D_f} \frac{\sinh(\frac{L-z}{\lambda_f})}{\cosh(\frac{L}{\lambda_f})} \frac{J \cos \theta \lambda_s K_1 \frac{R}{\lambda_s}}{K_0 \frac{R}{\lambda_s}}$$

(2.4)

here,  $\lambda_f$  is the diffusion length of the adatoms on the nanowire sidewall. Therefore the total adatom diffusion flux to the FECA droplet can be written as,

$$J_{diff}(L) = \left[ -D_f 2 \frac{\partial n_f}{\partial z} \right]_{z=L}$$

(2.5)

The net flux impinging on the FECA droplet from vapour phase can be written as,

$$J_{top} = \frac{P - P_{\infty} exp(\frac{2\sigma_{lv}\Omega_l}{RK_BT})}{\sqrt{2\pi m K_B T}}$$

(2.6)

Here, P is the partial pressure of the precursor inside the reactor chamber.  $P_{\infty}$  is the pressure of the reactant species in a droplet of infinite radius of curvature.  $\sigma_{lv}$  is the surface energy density at the vapour-liquid interface and  $\Omega_l$  is volume per atom in the liquid phase. Now, using steady state hypothesis, the number of atoms transferred from vapour phase to the FECA droplet per unit time can be equated with the number of atoms crystallised at the FECA droplet - substrate interface per unit time.

$$\therefore 2\pi R^2 J_{top} \alpha + J_{diff}(L) \alpha' = \left(\frac{\pi R^2}{\Omega_s}\right) \frac{dL}{dt}$$

(2.7)

Where  $\Omega_s$  is the volume per atom in crystal phase,  $\alpha$  is the sticking coefficient of the atoms impinging on FECA droplet from the vapour phase and  $\alpha'$  is the sticking coefficient of the substrate surface. Substituting equation (2.4), (2.5) and (2.6) into equation (2.7) we get the following.

$$\frac{dL}{dt} = \left[\frac{2\Omega_s J \sin\theta\lambda_f}{R} \tan(\frac{L}{\lambda_f}) + \frac{2\Omega_s}{R\cosh(\frac{L}{\lambda_f})} \frac{J\cos\theta\lambda_s K_1 \frac{R}{\lambda_s}}{K_0(\frac{R}{\lambda_s})}\right] \alpha' + 2\Omega_s \frac{P - P_\infty exp(\frac{2\sigma_l,\Omega_l}{RK_BT})}{\sqrt{2\pi m K_B T}} \alpha \quad (2.8)$$

The first term of the above expression represents the diffusion of atoms impinging on nanowire sidewall. The second term represents diffusion from substrate surface along the nanowire. And the third term represents atoms impinging directly on the FECA from vapour phase. It has been experimentally observed that the sticking coefficient of the FECA droplet,  $\alpha$  is two orders of magnitude higher than that of substrate surface,  $\alpha'$  [19],[24]. This confirms the direct dependence of nanowire growth rate,  $\frac{dL}{dt}$  on the effective impingement of the precursor material from the vapour phase, partial pressure of the precursor inside the reactor chamber, P and growth temperature, T.

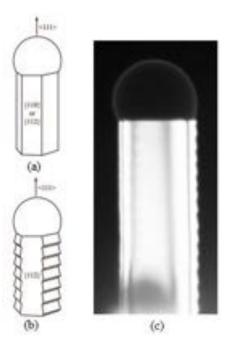

### 2.3 Structure of VLS grown nanowires

Physical characteristics of a silicon nanowire is extremely important as electrical, mechanical and optical properties of the silicon nanowire depend on it. Growing nanowires with definite crystallographic orientation also helps maintaining a uniform separation between nanowires and assists in-place growth. Typically, VLS grown nanowires exhibit  $\langle 110 \rangle$ ,  $\langle 112 \rangle$  and  $\langle 111 \rangle$  growth directions. The growth direction is almost independent of the method used for growth. However, the growth direction and crystallography of the nanowires do depend on growth conditions such as temperature and pressure [6]. Another important phenomenon is the diameter dependence of silicon nanowire growth direction [26]. It has been observed that nanowires having diameter larger than 50 nm favour  $\langle 111 \rangle$  orientation.  $\langle 110 \rangle$  direction is preferred by nanowires having diameter less than 20 nm. There is always a probability that a fraction of nanowires would grow in the  $\langle 112 \rangle$  direction. This probability is significantly higher for wire diameters between 20 nm to 50 nm [27]. This diameter dependence can be associated with the scaling behaviour of different energetic contributions. The two most prominent of them are the contribution of the side faces and the contribution of the liquid FECA - solid interface. Both components are dependent

Figure 2.8: (a) Schematic diagram of a silicon nanowire with hexagonal cross section and crystallographically defined sidewall facets. (b) Schematic diagram of a nanowire with three sawtooth faces. (c) TEM image of such a nanowire. The image is taken from reference [25].

on the diameter of the growing nanowire. The thicker nanowires grow in such a direction which minimises the contribution of the FECA - solid interface and the thinner nanowires grow in a direction that minimises the contribution of the sidewalls. Like all other crystalline materials, silicon nanowires have a natural tendency to grow crystallographically defined surfaces. This behaviour becomes prominent at higher temperatures as surface diffusion becomes faster. It has been observed that (111) silicon nanowires exhibit hexagonal cross section with (110) or (112)surface facets [28]. This is schematically shown in figure 2.8(a). Similarly (110) oriented nanowires exhibit hexagonal cross section with four  $\{111\}$  and two  $\{100\}$  facets [29]. Silicon nanowires can also exhibit sawtooth faceting. For example, an [111] oriented silicon nanowire with hexagonal cross section and six {112} faces can demonstrate a structure where three of the faces are flat planes and the other three are roughened in a regular sawtooth-like pattern [25]. A schematic diagram of such a nanowire is shown in figure 2.8(b). Figure 2.8(c) exhibits TEM image of one such nanowire. The crystal structure of silicon nanowires are typically assumed to be diamond like, identical to bulk silicon. Although Fontcuberta et al. [30] claimed to find evidence of silicon nanowires exhibiting wurtzite crystal structure. Properties of any material primarily depend on its fundamental structure. However the situation with nanomaterials are a bit different. Due to small size of nanoparticles and nanowires, the surface to volume ratio of these materials is extremely high. Because of this, the properties of these materials are heavily influenced by their surface properties.

### 2.4 Applications of VLS grown nanowires

Silicon nanowires have found use in quite a large number of applications. Where some applications take advantage of the typical geometry, some rely on its size dependant or surface dominated properties. Extremely thin (<10 nm) silicon nanowires also exhibit quantum mechanical confinement effect. However, the focus of this report is on electrical characteristics of silicon nanowires, outside the realm of quantum mechanical effects. The following section presents a summary of the most common applications of silicon nanowires.

#### 2.4.1 Templates

Silicon nanowires can be used as a template to make other nanostructures which are otherwise difficult to synthesise. For example, in a study, silicon nanowires coated with gold were subsequently furnace annealed at 880 °C and treated with HF. The SiOx formed by the earlier process were etched by HF in the later process, leaving only gold nanowires [31]. This process can also be used to synthesise magnetically hard materials. In another study, silicon nanowire templates were used to assemble Ni particles to form a quasi one-dimensional structure. This exhibits an enhanced coercivity of 315.2 Oe at room temperature [32]. Other than metal nanostructures, silicon nitride nanowires have also been grown using this method [33].

#### 2.4.2 Solar cells

Solar cells are one of the most common applications of silicon nanowires. The main reason behind introducing silicon nanowires to photovoltaics is to reduce the cost of the effective material. Studies show a solar cell constructed using silicon nanowires can achieve efficient photon absorption by using just 1% of the active material required to construct a conventional silicon solar cell [35]. The solar cells constructed using silicon nanowires have few other advantages over conventional crystalline silicon solar cells fabricated using silicon wafers. For instance, unlike silicon wafers the substrate made of silicon nanowires can be of any shape and size. As a result, the short circuit current through the cell can be engineered. On the other hand, the shape

Figure 2.9: (a) Specular reflectance, in log scale, of conventional solar cell (blue curve) and silicon nanowire solar cell (green curve). (B) Photographs of conventional solar cell (faint green) and silicon nanowire solar cell (dark blue). Figures taken from reference [34].

and size of the silicon wafers is constricted by the wafer growth processes which has certain limitations. The short circuit current through a solar cell can be described using the following equation [36].

$$I_{sc} = qAG(L_n + W + L_p) \tag{2.9}$$

Here  $L_n$  and  $L_p$  are the minority carrier diffusion length of electron and hole. W is width of the depletion layer. G is the rate of carrier generation and A is the substrate area exposed to the incident illumination. This is why modulating A has such enormous effect on  $I_{sc}$ . Another advantage of using silicon nanowires as substrate is that thin layers of silicon nanowires are reasonably flexible. This property makes the silicon nanowires more interesting for solar cell application as it leads to the fabrication of flexible solar cell and roll-to-roll processing. Experiments also confirm that silicon nanowires demonstrate significant light trapping property. As a result, the energy conversion efficiency of silicon nanowire based solar cells may become as high as 12% [34] even after using so little material. After generation, separation of the charge carriers is of prime importance for the operation of a solar cell. A huge advantage of silicon nanowires is that they allow lateral diffusion of minority carriers, as in most cases the junction is located along the radial direction [34]. This phenomenon can dramatically increase  $I_{sc}$  and hence the efficiency of the solar cell as the efficiency is related to  $I_{sc}$  by the following equation [36].

$$\eta = \frac{I_{sc}V_{oc}FF}{P_{in}} \tag{2.10}$$

Here,  $P_{in}$  is the power of the input illumination,  $V_{oc}$  is the open circuit voltage and FF is the fill factor of the solar cell.

#### 2.4.3 Lithium ion batteries

In conventional lithium ion batteries, to store one lithium ion in the anode, six carbon atoms are needed. On the other hand, one silicon atom can make alloy with more than four lithium ions. This was the motivation behind the research on silicon nanowires as an efficient anode material for lithium ion batteries. Other reasons behind the use of silicon nanowires as anode material for rechargeable lithium ion batteries are, its low-cost, good conductivity and scalability. It has been experimentally proven that silicon nanowire anode lithium ion batteries show larger charge capacity and longer cycling stability than conventional lithium ion batteries [37]. This is mostly because of the efficient charge transport and extraction-insertion of Li ions through the nanometer-scale rough surface of the anode.

#### 2.4.4 Thermoelectricity

Figure 2.10: (a) A silicon nanowire device made to study the thermoelectric performance of the silicon nanowire. (b) Power factor,  $S^2/\rho$  (red squares) and thermoelectric figure of merit ZT (blue squares) of a silicon nanowire of diameter 52 nm. The figures are taken from reference [38].

The simplest measure of how good a thermoelectric material, is to look at a quantity known as thermoelectric figure of merit. Most commonly used thermoelectric material is bismuth telluride ( $Bi_2Te_3$ ) and its alloys. Their thermoelectric figure of merit,  $ZT \approx 1$ . The thermoelectric figure of merit can be defined using the following equation.

$$ZT = \frac{S^2 T}{\rho k} \tag{2.11}$$

Where, S is the Seebeck coefficient,  $\rho$  is the electrical resistivity and k is the thermal conductivity of the material. Despite being the material of choice, Bi<sub>2</sub>Te<sub>3</sub> has a major problem. It is very difficult to scale bulk Bi<sub>2</sub>Te<sub>3</sub> for large scale energy conversion. Fabricating nanostructured Bi<sub>2</sub>Te<sub>3</sub> is even more difficult and expensive. On the other hand, bulk silicon has thermal conductivity of 150 W m<sup>-1</sup> K<sup>-1</sup> at room temperature [39]. This leads to a rather low ZT ( $\approx 0.01$ ) [40]. Silicon nanowires have Seebeck coefficient and electrical conductivity same as bulk silicon but the thermal conductivity of silicon nanowires are a function of its diameter. For example, a silicon nanowire of diameter about 50 nm can exhibit 100 fold reduction in the value of k and therefore exhibit ZT = 0.6 at room temperature [38]. Unlike Bi<sub>2</sub>Te<sub>3</sub>, silicon is an abandunt material in earth's crust. Also the established infrastructure to support low cost, high yield processing of silicon makes silicon nanowire a promising material for waste heat recouping, solid-state refrigeration and alternative energy production.

#### 2.4.5 Sensors

The operation of silicon nanowire sensors are mostly based on the following two principles. (i) Surface-enhanced Raman scattering (SERS) and (ii) field-effect transistors (FETs). It has been observed that silicon nanowires, coated with metals, are capable of enhancing Raman signals based on SERS effect. Using this phenomenon a detection limit as low as 600 molecules [41] can be achieved. Silicon nanowires, coated with gold, were used to detect dichlorvos (a pesticide) at a concentration of 8ng/L [42]. Nanowires coated with silver are being used for the detection of many biological molecules like rhodamine 6G [43] and calf thymes DNA [44]. These nanowires have also demonstrated excellent surface-enhanced fluorescence of lanthanide ions [45].