#### UNIVERSITÄT DER BUNDESWEHR MÜNCHEN

Fakultät für Elektrotechnik und Informationstechnik

# Low Voltage Hot-Carrier Issues in

# Deep-sub-micron

# Metal-Oxide-Semiconductor

# Field-Effect-Transistors

## Anil Kottantharayil

Vorsitzender des Promotionsausschusses : Prof. Dr.-Ing. H. Baumgärtner

1. Berichterstatter: Prof. Dr. rer. nat. I. Eisele

2. Berichterstatter: Prof. Dr. J. Vasi

Tag der Prüfung 22. November 2001

Mit der Promotion erlangter akademischer Grad :

Doktor-Ingenieur

(Dr.-Ing.)

Neubiberg, den 24. Januar 2002

| Der Druck dieser Arbeit wurde durch Haushaltsmittel der Universität der Bundeswehr München gefödert. |

|------------------------------------------------------------------------------------------------------|

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

|                                                                                                      |

# Abstract

Hot-carrier effects in silicon n-channel MOSFETs were investigated as a function of drain voltage  $(V_D)$  and gate voltage  $(V_G)$ . Impact ionization, gate injection and interface degradation have been observed for  $qV_D$  (ballistic energy limit) below the threshold energies for these processes. Detailed investigations were done for  $qV_D$  near and below the threshold energies in conventional (CON) uniformly doped channel, and laterally asymmetrical channel (LAC) and vertical MOSFETs.

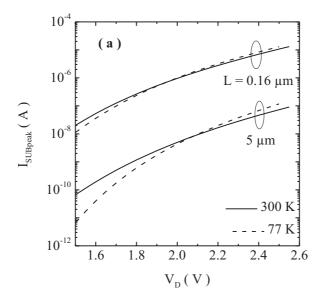

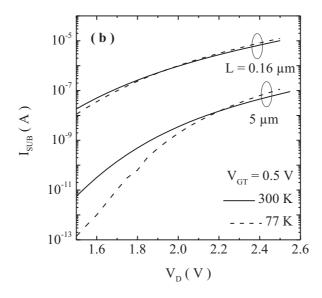

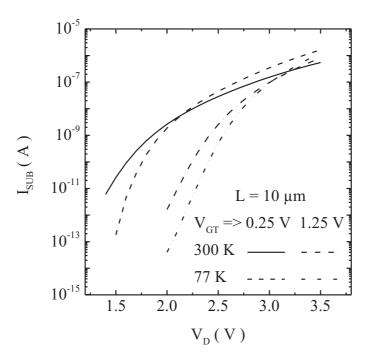

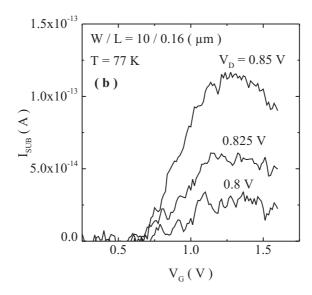

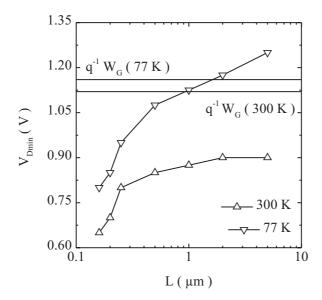

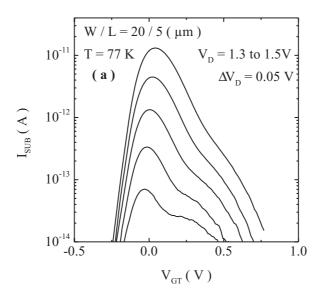

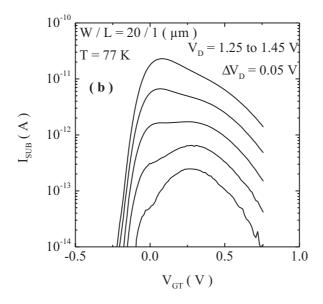

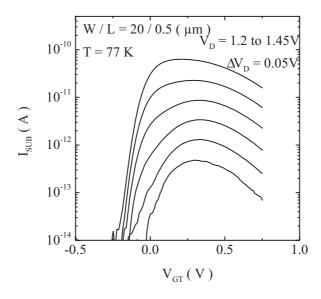

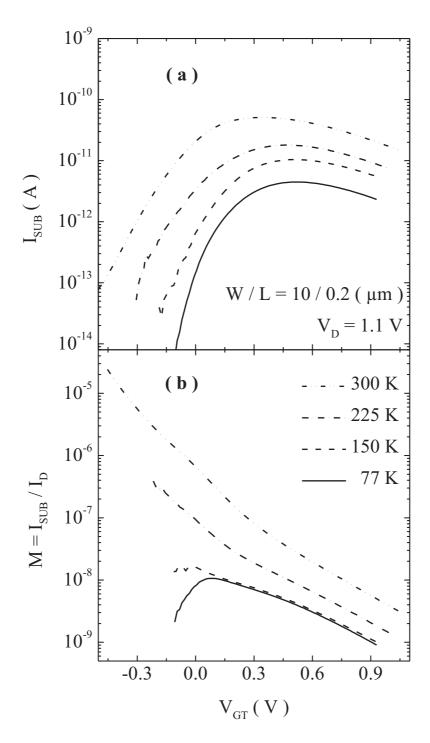

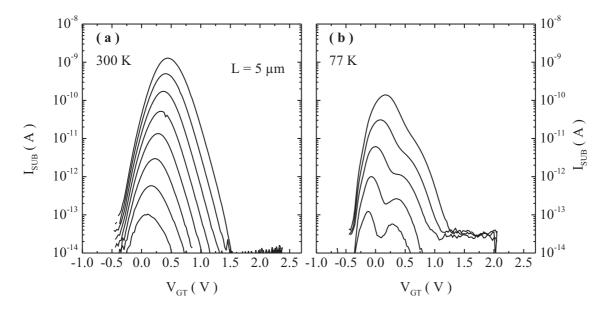

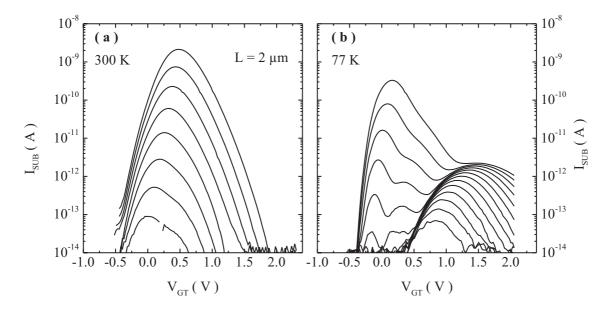

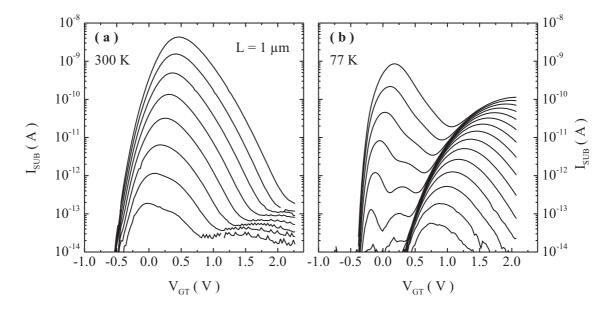

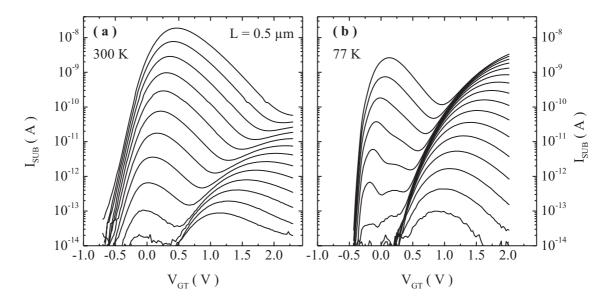

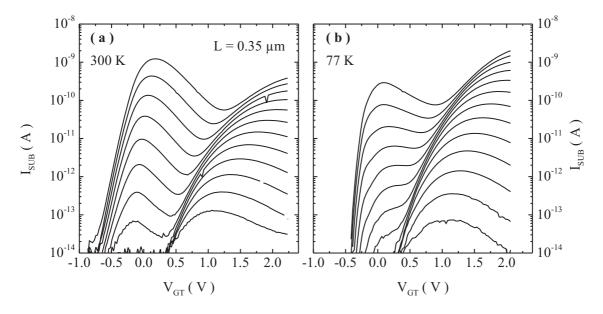

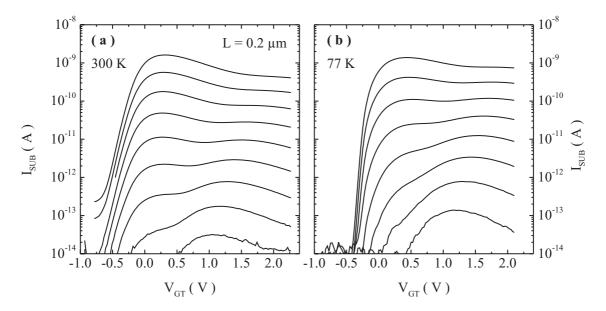

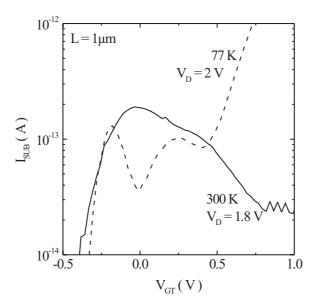

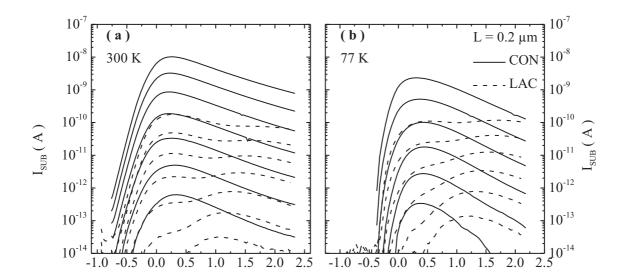

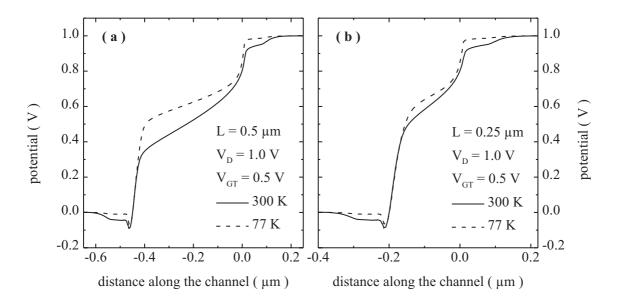

For large  $V_D$ , the substrate current  $(I_{SUB})$  due to impact ionization shows a negative temperature dependence, whereas at low  $V_D$  it shows a positive temperature dependence. A detailed investigation of channel length (L) and gate bias  $(V_G)$  dependence of this effect in CON devices is presented.

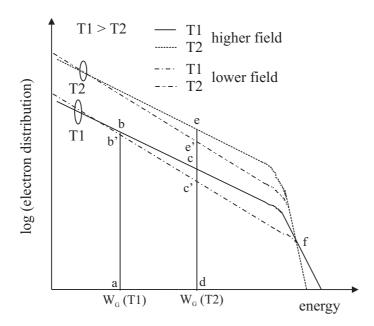

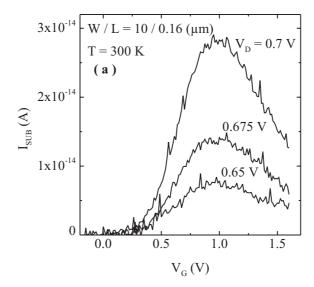

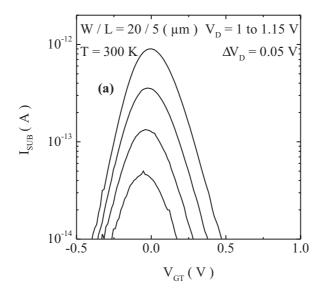

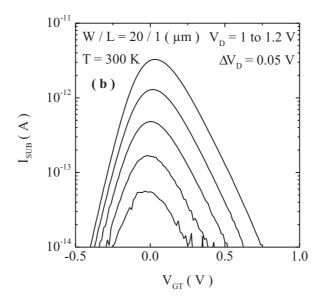

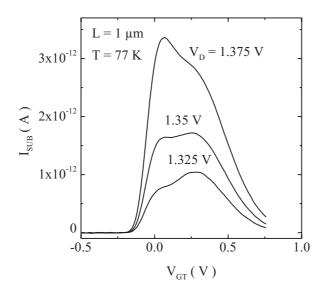

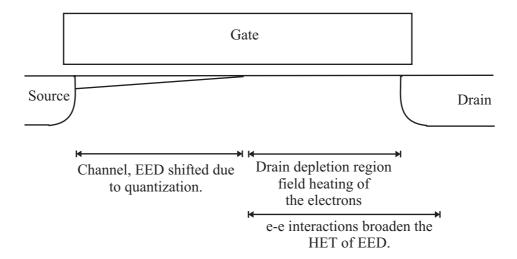

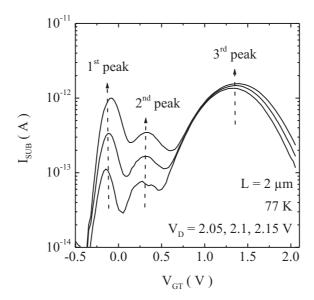

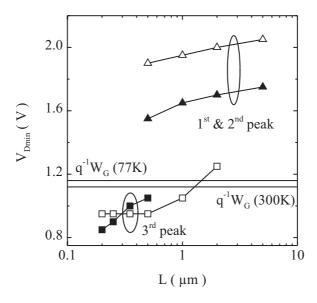

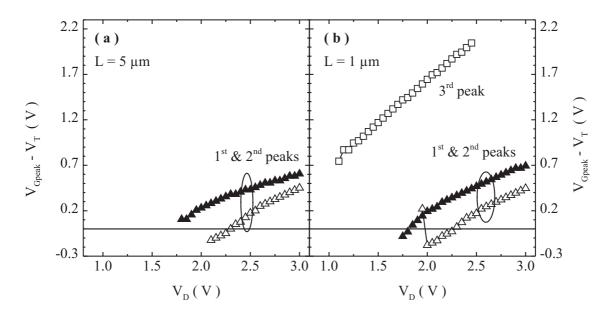

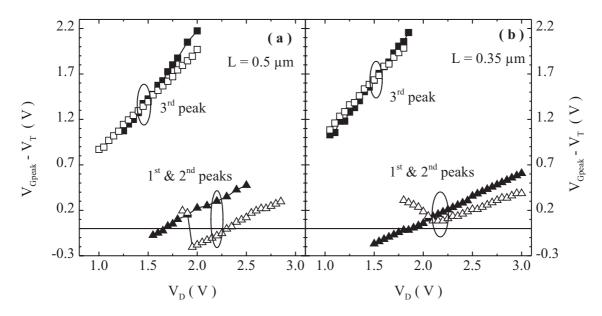

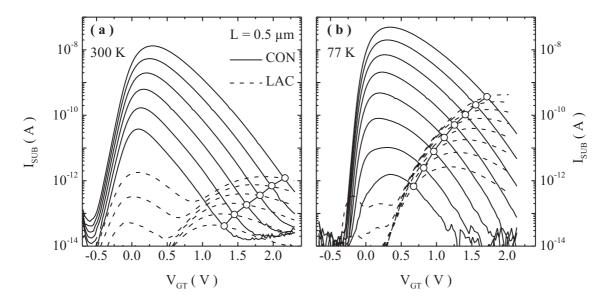

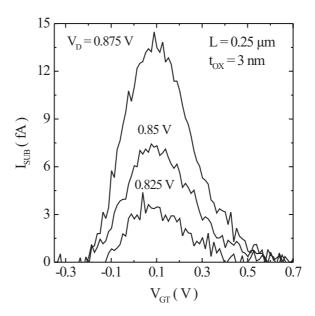

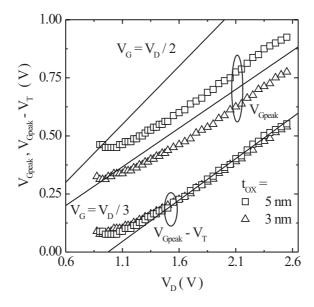

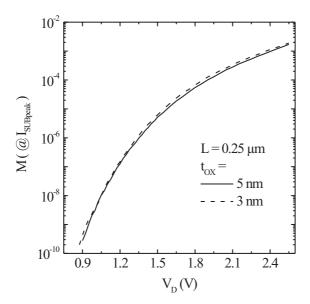

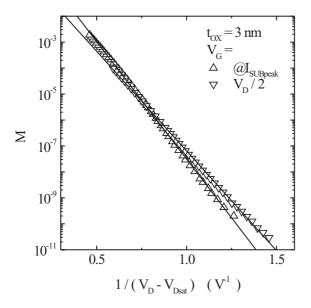

Impact ionization in CON and LAC devices are investigated for  $V_D$  near and below bandgap voltage. Two peaks are observed in  $I_{SUB}$  vs  $V_G$  characteristics at low  $V_D$  in CON devices. In LAC devices operated in the forward mode, three peaks are visible. For reverse mode of LAC, signatures of a second peak are observed. Extensive experimental data on L and temperature dependence of these anomalous observations are presented. In all the cases, the first peak was found to be suppressed as the temperature is reduced from 300 to 77 K. The second peak was more distinctly visible at lower temperature and enhanced upon decrease in L. The third peak in the case of LAC operated in the forward mode, enhanced as L and temperature are reduced. Experimental data are analyzed based on Monte-Carlo (MC) simulation data available in the literature and verify the presence of a lattice temperature dependent tail (LTDT) in electron energy distribution (EED) and its broadening due to short-range electron-electron interactions (SREEI). LTDT supports the presence of an electronphonon interaction (EPI) induced tail to EED. EPI and SREEI can populate the EED beyond the ballistic limit of  $qV_D$ . It is shown that the anomalous second peak in  $I_{SUB}$ vs  $V_G$  is due to SREEI. We find that SREEI is weakened in long channel devices and for large  $V_G$  values. SREEI is essentially a mechanism that redistribute energy gained from electric field and it is weakened due to increase in L and  $V_G$  which reduce the peak electric field.

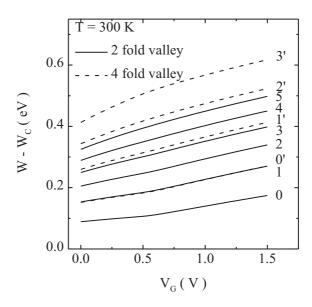

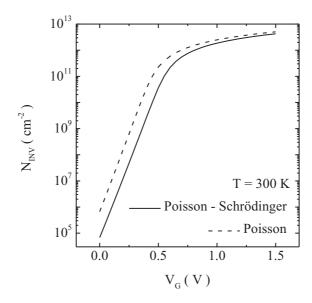

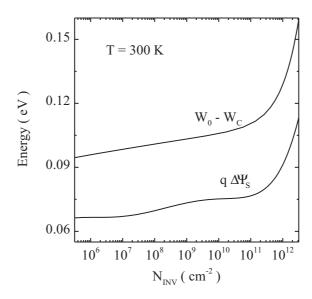

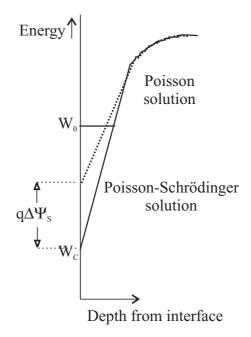

By employing one-dimensional self-consistent Poisson-Schrödinger simulations, we have shown that inversion layer quantization can result in an increase in the lowest energy of the electrons near the source side of the channel. This may lead to an effective energy gain of about 40 meV or more depending on  $V_G$ .

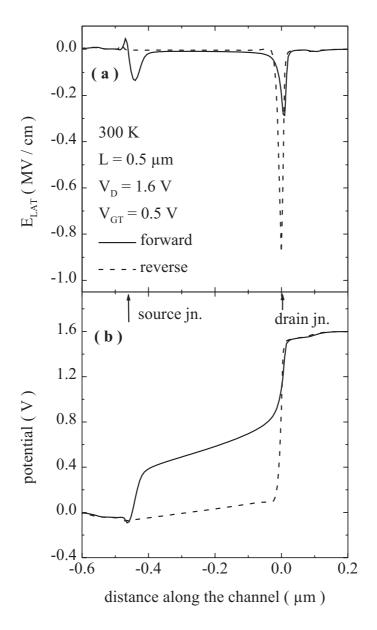

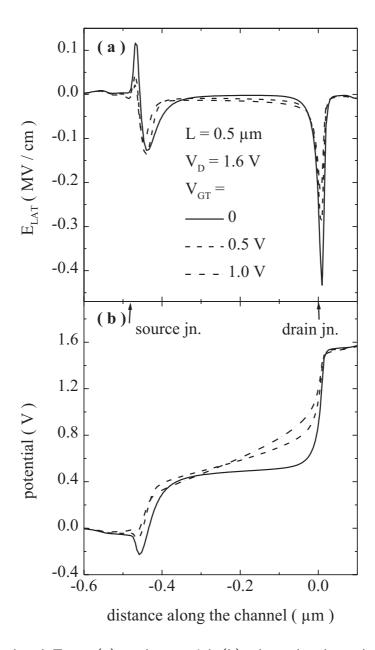

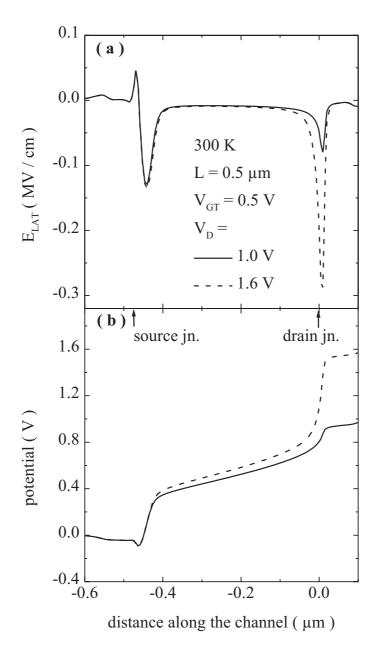

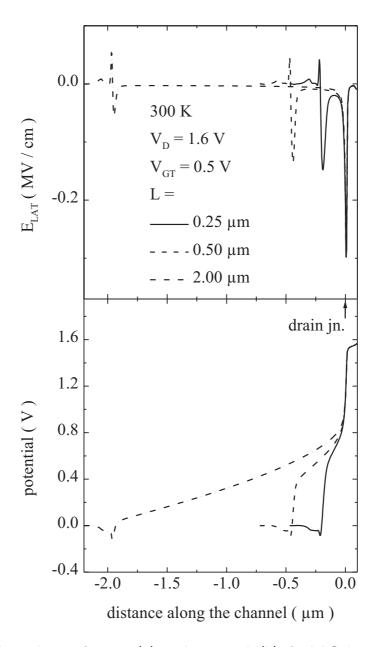

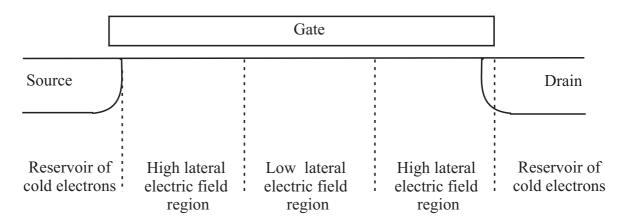

Two-dimensional drift-diffusion analysis has shown that LAC devices operated in the forward mode has a second high field region near the source. The third peak in  $I_{SUB}$  vs  $V_G$  is related to this high field region. In this case, since the source electrons are injected directly into a high field region, it is expected that LAC in this mode can be used to experimentally investigate modifications of source EED due to long-range electron-electron interactions predicted by some MC simulation groups.

We have also demonstrated gate injection and interface degradation for  $V_D$  lower than the  $Si - SiO_2$  barrier height. It was found that the worst case degradation condition depends strongly on gate oxide thickness.

The results presented suggest that hot-carrier effects may continue to be important even when the supply voltages are reduced below the threshold energies for the physical processes responsible for these effects.

# Zusammenfassung

Der Hot-Carrier-Effekt in n-Kanal Silizium-MOSFETs wird als Funktion der Drain-  $(V_D)$  und Gate-spannung  $(V_G)$  untersucht. Stoßionisation, Injektion in den Isolator und Degradation der  $Si-SiO_2$  Grenzfläche lassen sich für  $qV_D$  (ballistische Maximalnergie) unterhalb der Energieschwelle für diese Prozesse beobachten. Detaillierte Untersuchungen werden im konventionellen (CON), einheitlich dotierten Kanal, im lateral asymmetrischen Kanal (LAC) und an vertikalen MOSFETs durchgeführt.

Bei hohem  $V_D$  zeigt der Substratstrom  $(I_{SUB})$ , der durch Stoßionisation erzeugt wird, eine negative Temperaturabhängigkeit. Bei niedrigem  $V_D$  beobachtet man eine positive Temperaturabhängigkeit. Eine detailierte Untersuchung dieser Phenomene wird präsentiert.

Stoßionisation in CON- und LAC-MOSFETs werden für  $V_D$  nahe und unterhalb der Bandgap-Spannung untersucht. In den  $I_{SUB} - V_G$ -Kurven von CON-MOSFETs sind zwei Maxima bei niedrigem  $V_D$  zu beobachten. Bei in Vorwärtsrichtung betriebenen LAC-MOSFETs sind drei Maxima sichtbar. Im Rückwärtsbetrieb sind Anzeichen eines zweiten Maximums zu beobachten. Umfangreiche experimentelle Daten über Kanallängen- und Temperatur-Abhängigkeit dieser anomalen Beobachtungen werden vorgestellt. Senkung der Temperatur von 300 K auf 77 K lässt das erste Maximum schwächer werden. Das zweite Maximum jedoch wird deutlicher sichtbar und erhöht sich mit einer Verkleinerung von L. Das bei Vorwärtsrichtung gepolten LACs auftretende dritte Maximum steigt, wenn L und die Temperatur verringert werden. Die experimentellen Daten werden auf der Grundlage der in der Literatur verfügbaren Monte Carlo Simulationsdaten analysiert. Diese bestätigen die Tatsache, dass der Ausläufer der Energieverteilung der Elektronen (Electron Energy Distribution = EED) und dessen Verbreiterung auf Grund kurzreichweitiger Elektron-Elektron-Wechselwirkungen (Short-Range Electron-Electron Interactions = SREEI) von der Gittertemperatur abhängen (Lattice Temperature Dependent Tail = LTDT). LTDT unterstützt das Erscheinen eines durch die Elektron-Phonon Wechselwirkung (Electron-Phonon Interaction = EPI) induzierten Ausläufers in der EED. EPI und SREEI können dazu führen, dass die Elektronen energetische Zustände jenseits des ballistischen Limits von  $qV_D$  einnehmen können. Es wird gezeigt, dass das anomale zweite Maximum in der  $I_{SUB} - V_G$ -Kurve auf SREEI zurückzuführen ist. Es ist festzustellen, dass SREEI in Langkanal-MOSFETs und bei sehr großen  $V_G$ -Werten schwächer ist. SREEI ist im Wesentlichen eine Wechselwirkung, die die aus dem elektrischen Feld gewonnene Energie neu verteilt. Die Zunahme von L und/oder  $V_G$  reduziert das Maximum des elektrische Feldes und reduziert dadurch den Einfluss von SREEI.

Unter Verwendung eindimensionaler selbstkonsistenter Poisson - Schrödinger Simulationen wird gezeigt, dass Quantisierung in der Inversionsschicht zu einer Zunahme der niedrigsten Energie der Elektronen nahe der Source-Seite des Kanals führen kann. Dies kann zu einem effektiven Energiegewinn in der Größenordnung von 40 meV oder mehr führen, abhängig von  $V_G$ .

Die zweidimensionale Drift-Diffusionsanalyse zeigt, dass in Vorwärtsrichtung betriebene LAC - MOSFETs eine zweite Hochfeldregion nahe Source aufweisen. Das dritte Maximum in den  $I_{SUB}-V_G$ -Kurven steht in Zusammenhang mit dieser Hochfeldregion. Da in diesem Fall die Source-Elektronen direkt in eine Hochfeldregion injiziert werden, können in diese Richtung betriebene LAC MOSFETs genutzt werden, um ex-

perimentell die von einigen MC Simulationsgruppen vorausgesagte Source EED aufgrund von langreichweitigen Elektron-Elektron Wechselwirkungen zu untersuchen.

Injektion ins Gate und Interface-Degradation für Drainspannungen niedriger als die  $Si-SiO_2$  Barrierenhöhe werden ebenfalls gezeigt. Es zeigt sich, dass die "worst case" Degradationsbedingung stark von der Dicke des Gateoxides abhängig ist. Die präsentierten Ergebnisse lassen vermuten, dass Hot-Carrier-Effekte - wegen der ihnen zu Grunde liegenden physikalischen Prozesse - auch künftig von Bedeutung bleiben, wenn die Versorgungsspannung unter die Einsatzenergie gesenkt wird.

**Key words**: electron-electron interactions, electron energy distribution, electron-phonon interactions, hot-carrier, impact ionization, MOSFET, silicon, thermal tail

# Contents

|          | Nor                              | menclature                          |                                                                  |             |  |  |

|----------|----------------------------------|-------------------------------------|------------------------------------------------------------------|-------------|--|--|

| 1        | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | State<br>Scope                      | ion Problem                                                      | 1 2 2 2 2 2 |  |  |

| <b>2</b> | A F                              | Review                              | of Low Voltage Hot-Carrier Issues in nMOSFETs                    | Ę           |  |  |

|          | 2.1                              | _                                   |                                                                  |             |  |  |

|          | 2.2                              |                                     | Models of Carrier Heating                                        |             |  |  |

|          |                                  | 2.2.1                               | Heating by Electric Field                                        | 6           |  |  |

|          |                                  | 2.2.2                               | The Energy Balance Perspective                                   | 7           |  |  |

|          |                                  | 2.2.3                               | The Monte-Carlo Method                                           | 8           |  |  |

|          | 2.3                              | Low V                               | Voltage Hot-Carrier Effects in nMOSFETs                          | Ć           |  |  |

|          |                                  | 2.3.1                               | The Cross-over Effect                                            | į,          |  |  |

|          |                                  | 2.3.2                               | Sub Bandgap Impact Ionization                                    | 10          |  |  |

|          |                                  | 2.3.3                               | Sub-barrier Electron Injection into the Gate Dielectric          | 1.          |  |  |

|          |                                  | 2.3.4                               | Hot-Carrier Reliability at Low Drain Voltages                    | 12          |  |  |

|          | 2.4                              | ers with Energy Greater than $qV_D$ | 13                                                               |             |  |  |

|          |                                  | 2.4.1                               | Electron-Phonon Interactions as an Energy Redistribution Mech-   |             |  |  |

|          |                                  |                                     | anism                                                            | 13          |  |  |

|          |                                  | 2.4.2                               | Electron-Electron Interactions as an Energy Redistribution Mech- |             |  |  |

|          |                                  |                                     | anism                                                            | 14          |  |  |

|          |                                  |                                     | 2.4.2.1 Short-Range Electron-Electron Interactions               | 16          |  |  |

|          |                                  | 0.4.0                               | 2.4.2.2 Long-Range Electron-Electron Interactions                | 16          |  |  |

|          |                                  | 2.4.3 $2.4.4$                       | Electron Energy Distribution in n-channel MOSFETs                | 17          |  |  |

|          | 2.5                              |                                     | Discussion                                                       | 18<br>19    |  |  |

|          | 2.3                              | 5 Summary                           |                                                                  |             |  |  |

| 3        | Ten                              | nperat                              | ure Dependence of Substrate Current in nMOSFETs                  | 2           |  |  |

|          | 3.1                              |                                     |                                                                  |             |  |  |

|          | 3.2                              | 2 Experimental Results              |                                                                  |             |  |  |

|          |                                  | 3.2.1                               | Cross-over in Substrate Current                                  | 23          |  |  |

|          |                                  | 3.2.2                               | Summary of Experimental Results                                  | 27          |  |  |

|          | 3.3                              | Analy                               | sis and Discussion                                               | 2'          |  |  |

|          |                                  | 3.3.1                               | Theory of the Cross-over Effect                                  | 2'          |  |  |

ii Contents

|   |     | 3.3.2       |                                                                                 | 20              |  |  |

|---|-----|-------------|---------------------------------------------------------------------------------|-----------------|--|--|

|   | 3.4 | Concl       | Voltage                                                                         | $\frac{28}{32}$ |  |  |

|   | 5.4 | Conch       | usions                                                                          | 32              |  |  |

| 4 | Nea | r Thre      | eshold Impact Ionization in Conventional nMOSFETs                               | 33              |  |  |

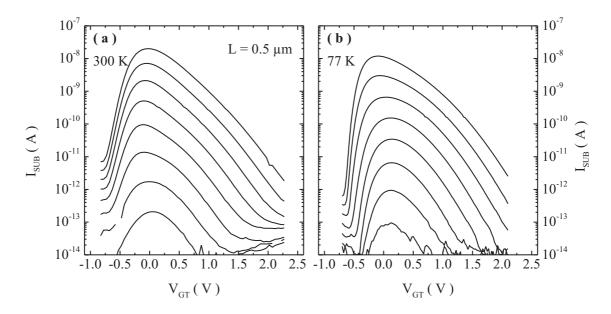

|   | 4.1 | Exper       | imental Results                                                                 | 34              |  |  |

|   |     | 4.1.1       | $I_{SUB}$ vs $V_G$ Characteristics                                              | 34              |  |  |

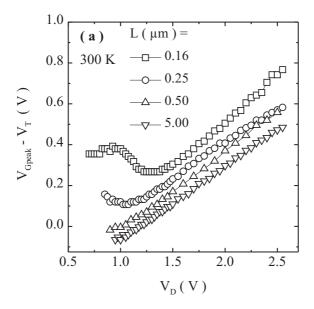

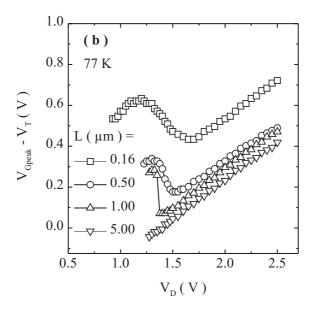

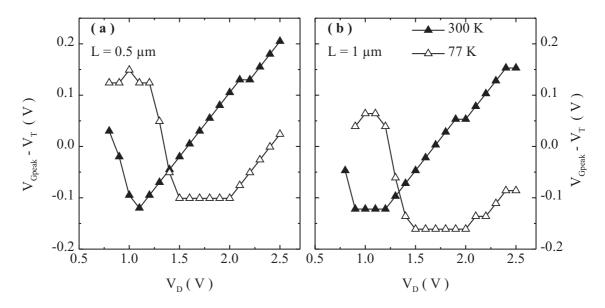

|   |     | 4.1.2       | $V_{Gpeak}$ vs $V_D$ Plots                                                      | 36              |  |  |

|   |     | 4.1.3       | Discussions                                                                     | 41<br>42        |  |  |

|   | 4.2 | Analysis    |                                                                                 |                 |  |  |

|   |     | 4.2.1       | Experimental Verification of the Nature of the Tail of EED                      | 42              |  |  |

|   |     | 4.2.2       | Relative Strength of the Thermal and EEI Broadened Tails                        | 46              |  |  |

|   |     | 4.2.3       | Inversion Layer Quantization as an Energy Gain Mechanism                        | 48              |  |  |

|   |     | 4.2.4       | Location of Action of Various Energy Gain and Redistribution                    |                 |  |  |

|   |     |             | Mechanisms                                                                      | 53              |  |  |

|   |     | 4.2.5       | Explanation of the Peaks in $I_{SUB}$ vs $V_G$                                  | 54              |  |  |

|   |     | 4.2.6       | Correlation between Electron-Electron Interactions and Anom-                    | <b>F</b> 0      |  |  |

|   |     | 407         | alous $V_{Gpeak}$ Behavior                                                      | 56              |  |  |

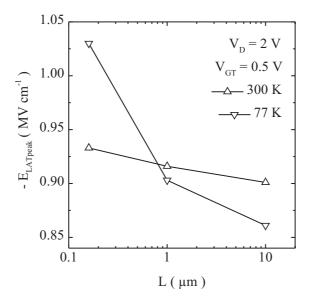

|   |     | 4.2.7       | Channel Length Dependence of $I_{SUB}$ vs $V_G$ Curves                          | 56              |  |  |

|   | 4.9 | 4.2.8       | Gate Voltage Dependence of Electron-Electron Interaction Tail                   | 60              |  |  |

|   | 4.3 | Conch       | usions                                                                          | 61              |  |  |

| 5 | Imp | act Io      | nization in Laterally Asymmetrical n-channel MOSFETs                            | 63              |  |  |

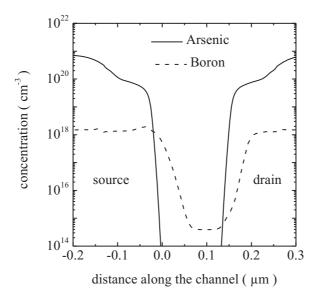

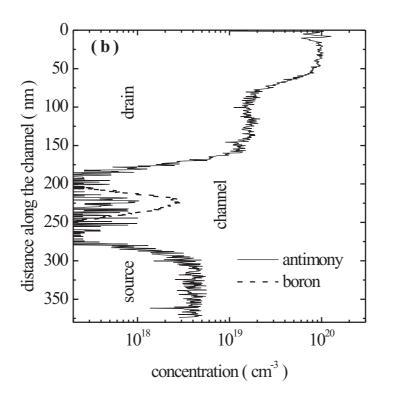

|   | 5.1 | Device      | e Structure                                                                     | 64              |  |  |

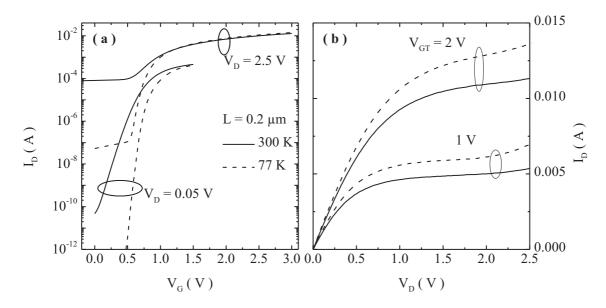

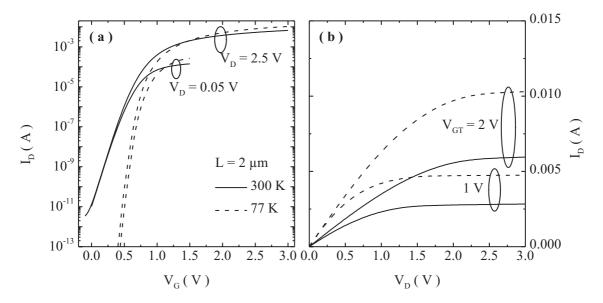

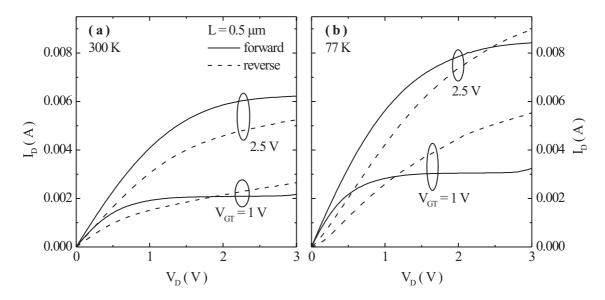

|   | 5.2 | Termi       | nal Characteristics                                                             | 65              |  |  |

|   | 5.3 | $I_{SUB}$ v | vs $V_G$ in the Forward Mode                                                    | 65              |  |  |

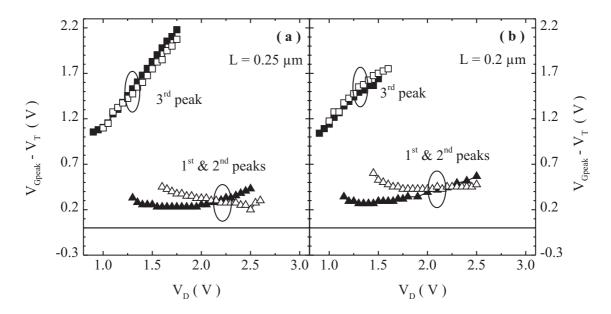

|   |     | 5.3.1       | $V_{Gpeak}$ vs $V_D$ Plots                                                      | 70              |  |  |

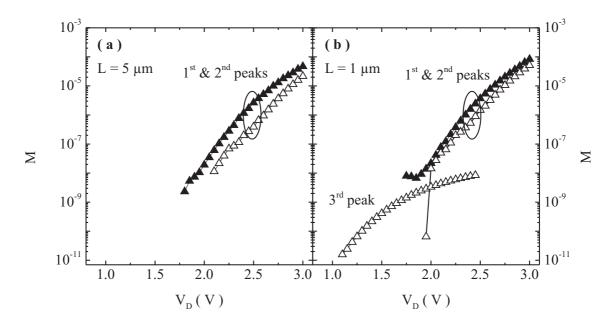

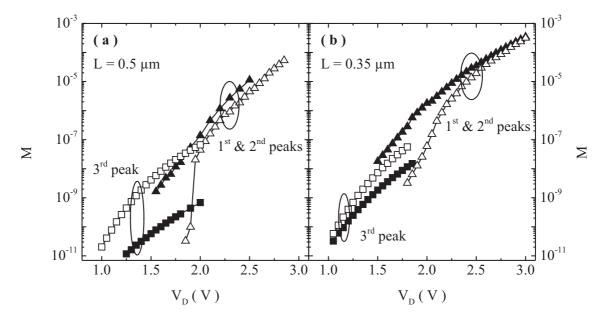

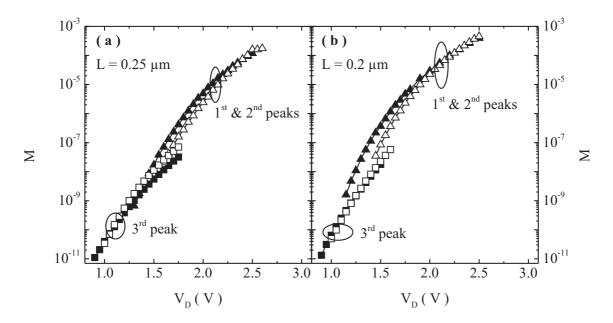

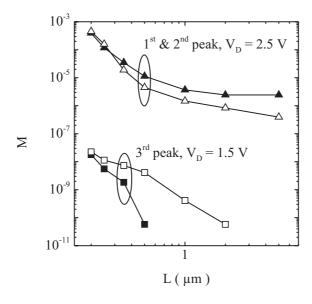

|   |     | 5.3.2       | $I_{SUB}/I_D$ vs $V_D$ Plots                                                    | 76              |  |  |

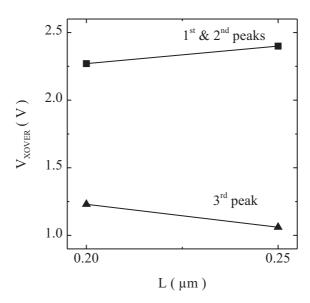

|   |     | 5.3.3       | Cross-over Voltage                                                              | 79              |  |  |

|   | 5.4 |             | vs $V_G$ in the Reverse Mode                                                    | 79              |  |  |

|   | 5.5 |             | ary of Experimental Results                                                     | 80              |  |  |

|   | 5.6 |             | arison with Conventional Devices                                                | 83              |  |  |

|   | 5.7 | Analy       |                                                                                 | 85              |  |  |

|   |     | 5.7.1       | Simulations                                                                     | 85              |  |  |

|   |     | 5.7.2       | Interpretation of $I_{SUB}$ vs $V_G$ Data for the Forward Mode of Op-           | 0.0             |  |  |

|   |     |             | eration                                                                         | 92              |  |  |

|   |     |             | 5.7.2.1 The First and Second Peaks                                              | 92              |  |  |

|   |     |             | 5.7.2.2 The Third Peak                                                          | 93              |  |  |

|   |     |             | 5.7.2.3 Differences between Electron Heating Near the Source and Near the Drain | 95              |  |  |

|   |     | 5.7.3       | Further Support for the Verification of the EED Tail                            | 96              |  |  |

|   | 5.8 |             | usions                                                                          | 97              |  |  |

|   | 0.0 | COHOI       |                                                                                 | 91              |  |  |

| 6 | Low |             | age Hot-Electron Device Reliability                                             | 99              |  |  |

|   | 6.1 |             | farrier Effects in Vertical MOSFETs                                             | 99              |  |  |

|   |     | 6.1.1       | Device Structure                                                                | 99              |  |  |

|   |     | 6.1.2       | Impact Ionization                                                               | 101             |  |  |

Contents

|              |                                                     | 6.1.3    | Gate Current                                      | 104 |

|--------------|-----------------------------------------------------|----------|---------------------------------------------------|-----|

|              |                                                     | 6.1.4    | Summary                                           |     |

|              | 6.2                                                 | Sub-B    | arrier Hot-Carrier Degradation in Lateral nMOSFET | 104 |

|              |                                                     | 6.2.1    | Devices                                           |     |

|              |                                                     | 6.2.2    | $I_{SUB}$ vs $V_G$ Characteristics                |     |

|              |                                                     | 6.2.3    | Hot-Carrier Stress Experiments                    |     |

|              |                                                     | 6.2.4    | Simulations and Discussions                       |     |

|              | 6.3                                                 | Conclu   | sions                                             | 114 |

| 7            | Con                                                 | clusio   | ns and Outlook                                    | 115 |

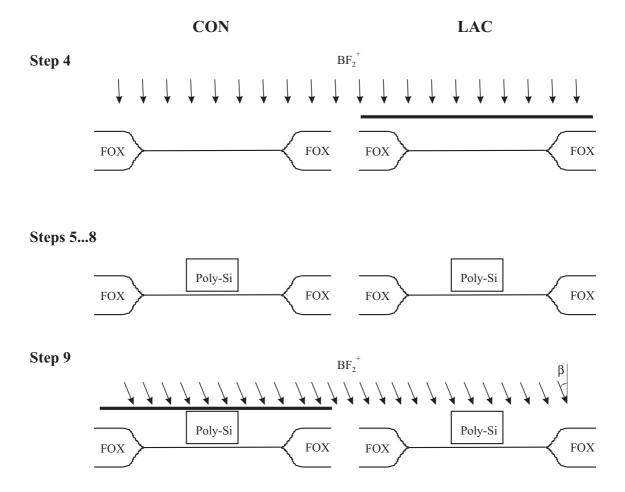

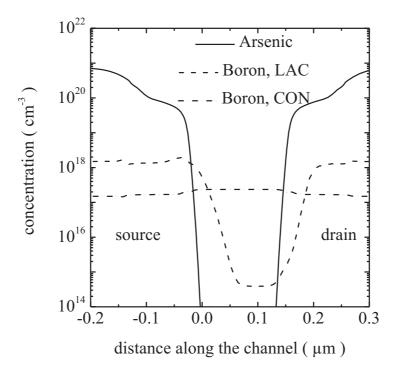

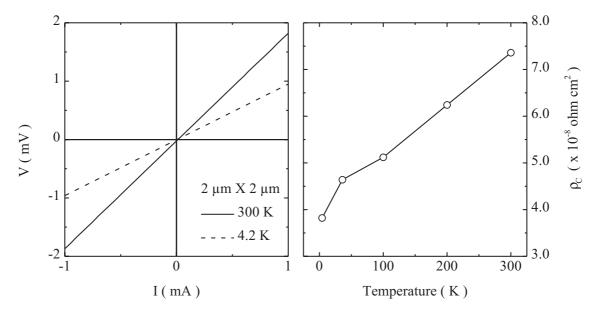

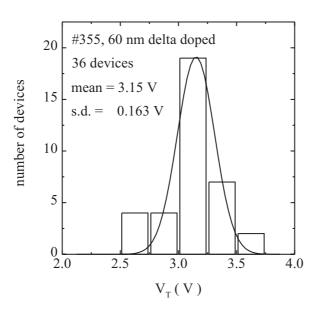

| $\mathbf{A}$ | Process Technology for CONventional and LAC MOSFETs |          |                                                   | 119 |

| В            | Pro                                                 | cess F   | ow and Manufacturability of Vertical MOSFETs      | 123 |

| $\mathbf{C}$ | Sch                                                 | ematic   | s of Electrical Measurement Systems               | 125 |

|              | List                                                | of Tal   | oles                                              | 127 |

|              | List                                                | of Fig   | rures                                             | 129 |

|              | Bib                                                 | liograp  | hy                                                | 133 |

|              | Pub                                                 | olicatio | ns                                                | 143 |

|              | Ack                                                 | nowled   | dgments                                           | 145 |

|              | Cur                                                 | ricului  | n Vitae                                           | 149 |

iv Contents

# Nomenclature

$\alpha$

impact ionization rate, in  $cm^{-1}$

```

\alpha^{\infty}

impact ionization rate at infinite electric field, in cm^{-1}

\beta

ion implant tilt angle

\Delta\Psi

potential barrier between the source and the channel, in Volt

difference in the surface potential between the quantum mechanical and classical

cases for identical inversion layer charge density, in Volt

\delta q_m

\% degradation in transconductance

% increase in charge pumping current due to stress

\% degradation in drain current due to stress

\delta I_D

incremental step in drain voltage, in Volt

\Delta W_C silicon to gate dielectric conduction band discontinuity, in electron Volt

permittivity of free space, 8.854\times 10^{-14}~Farad\:.\:cm^{-1}

\epsilon_o

relative permittivity of silicon, 11.9

\epsilon_{Si}

Current density, in Ampere . cm^{-2}

\vec{J_n}

E_{LATpeak} peak lateral electric field, in Volt . cm^{-1}

E_{LAT} lateral electric field, in Volt \cdot cm^{-1}

critical value of E at which electrons initiate impact ionization, in Volt \cdot cm^{-1}

critical E_{LAT} for velocity saturation of the electrons, in Volt. cm^{-1}

E_{sat}

transconductance, dI_D/dV_G, in Ampere . Volt^{-1}

g_m

G_n^{II}

Impact ionization generation rate for electrons, in cm^{-3}. sec^{-1}

charge pumping current, in Ampere

I_{CP}

I_D

drain current, in Ampere

I_G

gate current, in Ampere

```

vi

$I_{SUBpeak}$   $I_{SUB}$  corresponding to the maxima in  $I_{SUB}$  vs  $V_G$  plots, in Ampere

$I_{SUB}$  substrate current, in Ampere

k Boltzmann constant,  $8.62 \times 10^{-5}$  electron Volt Kelvin<sup>-1</sup>

L drawn channel length, in  $\mu m$

$L_{eff}$  effective channel length determined by electrical methods, in  $\mu m$

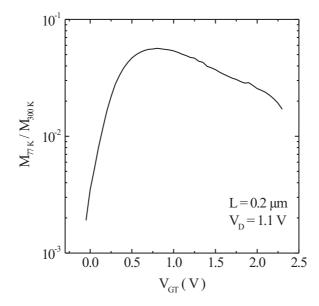

M impact ionization quantum yield given by  $I_{SUB}/I_D$

n volume density of inversion layer electrons, in  $cm^{-3}$

$N_{INV}$  inversion layer electron density, in  $cm^{-2}$

q elementary charge,  $1.60218 \times 10^{-19} Coulomb$

T temperature, in Kelvin or \*\*Centigrade\*

$T_E$  effective temperature, in Kelvin

$T_L$  lattice temperature, in Kelvin

$t_{OX}$  thickness of gate oxide, in nm

$V_{Dmin}$  minimum  $V_D$  for which bell shaped  $I_{SUB}$  vs  $V_G$  plots could be measured, in Volt

$V_{Dsat}$  drain voltage at which the drain current saturates in  $I_D$  vs  $V_D$ , in Volt

$V_D$  drain voltage, in Volt

$V_{Gpeak}$  gate voltage corresponding to  $I_{SUBpeak}$  in  $I_{SUB}$  vs  $V_G$  plots, in Volt

$V_{GT}$  gate over-drive given by  $V_G - V_T$ , in Volt

$V_G$  gate voltage, in Volt

$V_{SUB}$  substrate voltage, in Volt

$V_T$  threshold voltage, in Volt

$V_{XOVER}$  cross-over voltage,  $V_D$  at which  $I_{SUB}$  or M is independent of T, in Volt

W energy, in electron Volt

$W_C$  bottom of the conduction band

$W_G$  bandgap energy, in electron Volt

$W_K$  average kinetic energy of electrons, in electron Volt

BTE Boltzmann Transport Equation

CON CONventional (MOSFET)

Nomenclature vii

DIBL Drain Induced Barrier Lowering

EED Electron Energy Distribution

EEI Electron-Electron Interaction

EPI Electron-Phonon Interaction

HET High Energy Tail

ILQ Inversion Layer Quantization

IV current - voltage characteristics

LAC Laterally Asymmetrical Channel (MOSFET)

LEM Lucky Electron Model

LREEI Long-Range Electron-Electron Interaction

LTDT Lattice Temperature Dependent Tail

MBD Maxwell-Boltzmann Distribution

MBE Molecular Beam Epitaxy

MC Monte-Carlo

MOSFET Metal Oxide Semiconductor Field Effect Transistor

RIE Reactive Ion Etching

SIMS Secondary Ion Mass Spectroscopy

SREEI Short-Range Electron-Electron Interaction

TEM Transition Electron Microscopy

UCB University of California Berkeley

viii Nomenclature

# Chapter 1

# Introduction

#### 1.1 The Problem

Hot-carrier issues have been of serious concern for Complementary-Metal-Oxide-Silicon (CMOS) technologies for the last three decades [1]. Hot-carriers cause impact ionization which leads to substrate current and device breakdown in bulk CMOS devices, and floating body effects like kink and hysteresis in silicon-on-insulator (SOI) technologies. Injection of hot-carriers into gate dielectric causes a gate current and leads to degradation of drain current and transconductance, and changes in threshold voltage of the devices. Hot-carrier injection is also used for programming flash memory devices. Hot-carrier injection at operating voltages (in contrast to programming bias) raise serious concerns about long-term data retention reliability of such devices.

Aggressive scaling of device dimensions have been an enabling factor for CMOS devices to keep the lead in large scale integrated circuits (LSI) [2]. Even in a constant field scaling, the peak electric field in the device is increasing because of an increase in doping density. In generalized scaling (which is more common), the channel length is scaled more aggressively than the supply voltage, and this compound the hot-carrier issues.

To cause impact ionization and to surmount the silicon - silicon dioxide barrier (gate injection) the electrons must have minimum threshold energies which are bandgap energy  $(W_G)$  and 3.1 eV respectively. It was believed that hot-carrier effects will disappear once for ever when the supply voltages are reduced below these thresholds.

However there have been many reports of hot-carrier effects in n-channel silicon Metal-Oxide-Semiconductor Field-Effect-Transistors (nMOSFET) for supply voltages below the thresholds. For sub-100 nm devices, silicon dioxide will be replaced by higher permittivity dielectrics as gate dielectric. All the candidate materials have a significantly lower threshold for electron injection from silicon to dielectric [3]. Hot-carrier injection can be expected to be higher for such systems. In this context it is important to study hot-carrier effects at low supply voltages. A detailed understanding of the underlying physics is required to address the issues concerned. Specifically, (i) the presence of secondary energy gain mechanisms besides field heating (ii) methods to experimentally identify them and assess their strength (iii) impact of device scaling on them (iv) their impact on device performance and reliability, are issues that need attention. Such investigations will lead to better understanding of physics and accurate modeling.

2 Introduction

#### 1.2 State of the Art

Low voltage hot-carrier issues have been extensively investigated in the literature as demonstrated in chapter 2. Experimental data on almost all aspects of hot-carrier effects, namely impact ionization, gate injection and interface damage are reported for supply voltages lower than the threshold voltages for the respective processes. At low voltages, a reversal in the temperature dependence of substrate current (cross-over effect) is also reported.

However, many of the experimental investigations were aimed at checking the lowest supply voltages at which hot-carrier effects can be observed. Some investigations also tried to verify the applicability of empirical high voltage reliability projection techniques at low voltages. However there is still considerable controversy regarding this point. Experimental investigations of hot-carrier effects near respective thresholds are also marred by interfering leakage currents and low sensitive instrumentation employed in many cases. This had lead to reports of inconsistent data. There are very rare experimental attempts to understand the physical mechanisms involved.

Theoretical analysis based on simplifying assumptions have considerably advanced the theory of hot-carriers at low voltages. For example, absorption of optical phonons by electrons has been advanced to explain the possibility of electrons in MOSFETs with energy greater than the applied drain voltage. The resulting thermal tail in electron energy distribution (EED) was thought of as the reason for the cross-over effect. Sophisticated simulation using Monte-Carlo (MC) methods have also supported the idea of a thermal tail to EED. However, MC simulations have shown that the cross-over effect is due to an increase in the threshold energy for impact ionization. MC simulations have also proposed short and long-range electron-electron interactions (EEI) as mechanisms populating the EED beyond the applied drain bias.

Even though the idea of a thermal tail to EED is nearly two decades old, there seems to be no experimental proof for it. The role of short-range EEI is experimentally verified. But its strength is still debated. The role of long-range EEI on EED is still uncertain.

Even though MC simulations combined with experimental data have verified the role of short-range interactions in extending the tail of EED beyond the applied voltage, its inherent noise problems have prevented researchers from identifying experimental signatures of secondary energy gain mechanisms like EEI. Finer, but important, details like channel length and gate bias dependence of EEI broadening are still matters of guess work. Whether EEI will have any serious implications for device reliability is controversial.

## 1.3 Scope of the Present Work

In this work, first we have addressed the issue of cross-over effect in substrate current of conventional n-channel devices. Deficiencies in the understanding of cross-over effect are pointed out. Channel length and gate bias dependencies of cross-over effect in deep-sub-micron devices are experimentally investigated. We provide a graphical interpretation of the present understanding of cross-over effect. Two-dimensional drift-diffusion analysis is combined with the graphical method to interpret the experimental

data. The analysis establish the utility of electric field as an indicator of various regions of the electron energy distribution.

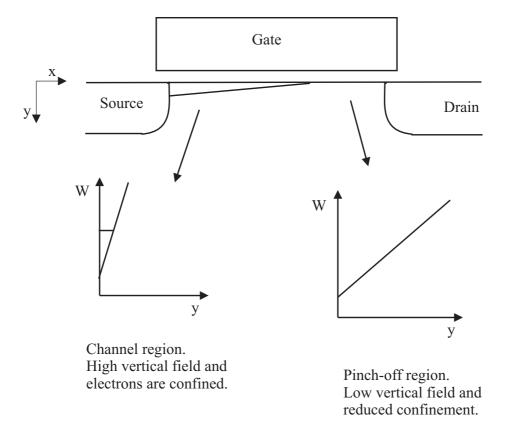

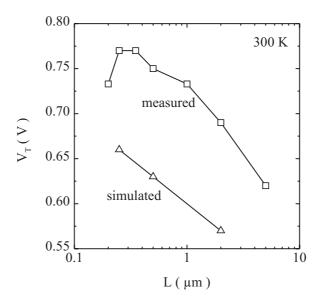

Impact ionization in conventional n-channel MOSFETs for drain voltages near the bandgap voltage ( $\sim 1.1 V$ ) is investigated using substrate current as monitor. The incomplete understanding of carrier heating beyond the applied bias is pointed out. We observe anomalous substrate current versus gate voltage plots with two peaks as the drain bias approaches the bandgap voltage. Channel length dependence of this behavior was studied. The presence of a lattice temperature dependent tail (LTDT) in EED is experimentally verified. Based on the experimental observations and one-dimensional quantum mechanical simulations, we have identified inversion layer quantization as an energy gain mechanism. Temperature sensitivity of the thermal tail has been used to assess the drain voltage below which the tail is important for impact ionization. The presence of the second peak in substrate current versus gate voltage plots is correlated to short-range EEI. Channel length dependence of the second peak is explained based on two-dimensional drift-diffusion simulations. Gate bias dependence of short-range EEI is established, and shows that it does not follow a monotonous positive gate bias dependence as is widely assumed. We show that, impact of short-range EEI increases with down scaling of channel length.

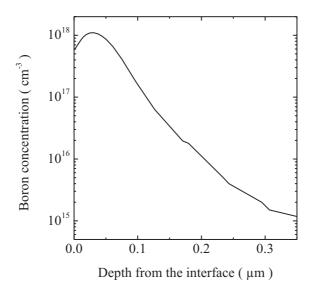

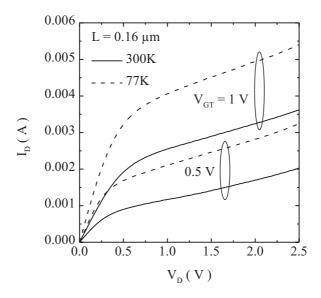

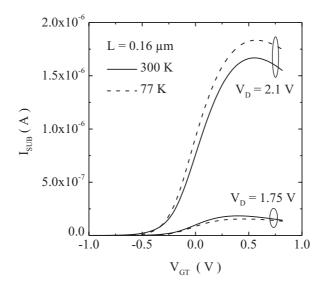

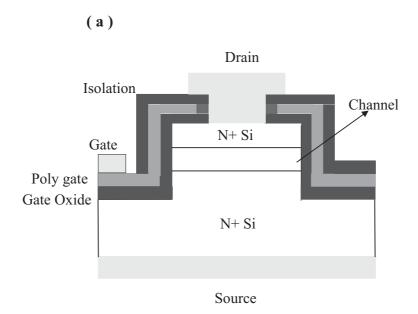

Impact ionization in laterally asymmetric n-channel MOSFETs were also investigated. These devices have a heavy boron doping at one end of the channel. They can be operated in two modes, forward mode in which the highly doped channel region is near the source junction, and reverse mode in which the highly doped channel region is near the drain junction. Anomalous substrate current versus gate voltage curves with three peaks are presented for the forward mode of operation. In the reverse mode, only one peak was observed. However we identify features that suggest a second peak in this case as well. A detailed study of the channel length dependence of these features are presented for both forward and reverse modes of operation. These results were also compared with that obtained for the conventional devices. From two-dimensional drift-diffusion simulations, it was found that, for the forward mode of operation, there are two peaks in the lateral field distribution whereas in the reverse mode, there is only one peak. The first and third peaks in the substrate current versus gate voltage in the forward mode are correlated to field heating in the two high field regions. It is shown that the second peak is due to short-range EEI in the drain side high field region. We have discussed the differences in carrier heating at the source and drain ends of the channel. We propose the forward mode of operation of these devices as a suitable testing tool to investigate the role of long-range EEI on the tail of EED.

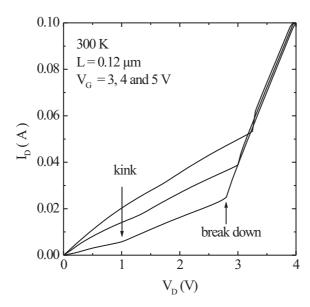

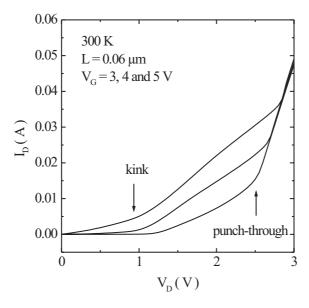

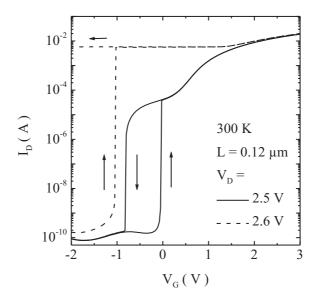

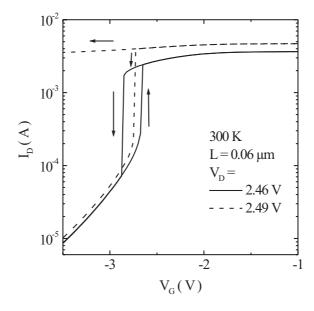

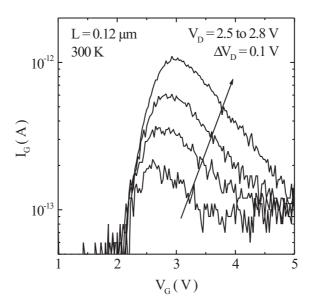

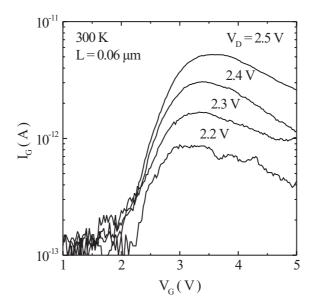

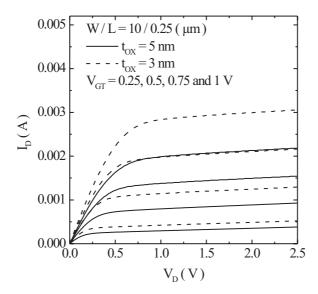

We also present experimental data on the impact of hot-carriers on device operation and reliability. Kink effect is demonstrated in vertical floating body devices for drain voltages less than 1.1 V. We also demonstrate gate injection for drain bias as low as 2.2 V. Hot-carrier degradation was observed in lateral conventional channel devices for drain voltages nominally below the silicon-silicon dioxide conduction band discontinuity. Even though signature of short-range EEI could be seen in the substrate current data at low drain voltages, the degradation does not increase monotonously with increasing gate bias as reported in the literature.

4 Introduction

## 1.4 Organization of the Thesis

In chapter 2, we present a literature review of low supply voltage hot-carrier issues in n-channel MOSFETs. A detailed channel length and gate bias dependence study of crossover phenomenon in conventional n-channel MOSFETs is presented in chapter 3. Chapter 4 treats impact ionization in conventional n-channel devices at drain voltages close to and below bandgap voltage. A detailed investigation of impact ionization at low voltages in laterally asymmetric n-channel MOSFETs is presented in chapter 5. In chapter 6, operational and degradation issues related to hot-carrier effects in vertical and lateral devices are presented.

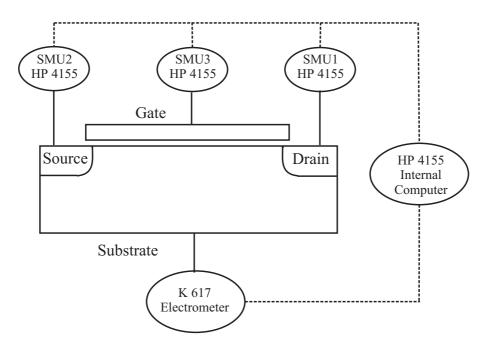

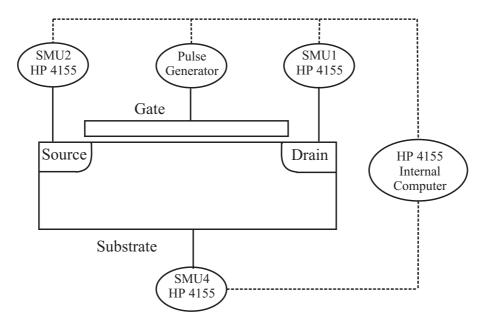

An overview of the process flow for the devices used in chapters 3, 4 and 5 is given in appendix A, along with a comparison of simulated doping profiles, terminal characteristics and properties of source and drain contacts. Appendix B provide the process flow and manufacturability of vertical MOSFETs discussed in chapter 6. Appendix C provide information about the measurement techniques employed.

# Chapter 2

# A Review of Low Voltage Hot-Carrier Issues in nMOSFETs

In this chapter a literature review is presented to highlight hot-carrier effects at low voltages in n-channel MOSFETs. We point out the deficiencies in the understanding of the physics of low voltage hot-carriers and thereby set the back ground for the work presented in this thesis. We concentrate on n-channel devices and hence on hot-electron issues. This is justified because hot-carrier issues are less severe in p-channel MOSFETs. The holes are much heavier than the electrons and hence the energy gained by them during transport is smaller than that by electrons. For injection into  $SiO_2$ , holes face nearly  $1\,eV$  higher barrier than electrons.

### 2.1 Hot-Carrier Effects in n-channel MOSFETs

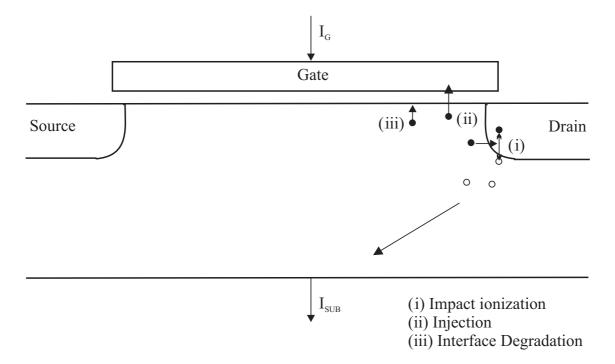

Hot-Carrier effects in silicon n-channel MOSFETs are schematically shown in figure 2.1 [4]. Hot-electrons can produce electron-hole pairs by impact ionization. In the extreme case this leads to device break down. The generated holes flow towards the substrate and can be measured as a substrate current  $(I_{SUB})$ .  $I_{SUB}$  is extensively used for the investigation of hot-carrier effects.

Those electrons which have energy higher than the silicon-dielectric conduction band discontinuity ( $\Delta W_C$ ) may get injected into the gate causing a gate current ( $I_G$ ) to flow. This is an important process for flash memory programming and retention reliability.

Hot-electrons can cause interface damage which effect the device performance parameters like drain current  $(I_D)$ , transconductance  $(g_m)$  and threshold voltage  $(V_T)$ . To ensure proper device operation, these parameters have to remain within given limits during the specified lifetime of the device.

Hot-carrier effects are threshold processes and it was considered that they will not pose significant problems when the device operating voltages are scaled down below the thresholds. However these expectations do not seem to be well founded.

For sub-100 nm devices with high relative permittivity gate dielectrics,  $\Delta W_C$  is much smaller than that of the  $Si-SiO_2$  system [3] and hence hot-carrier injection and interface degradation may be a more serious problem for these futuristic devices.

Figure 2.1: Schematic illustrating hot-carrier effects in n-channel MOSFETs. Filled circles represent electrons and open circles represent holes.

## 2.2 Models of Carrier Heating

In this section various modeling approaches to carrier heating in semiconductors is briefly reviewed.

## 2.2.1 Heating by Electric Field

Early attempts to understand hot-carrier effects, especially impact ionization, in semi-conductor devices were based on an electric field perspective [5, 6, 7]. This approach is still the most widely used one for modeling of hot-carrier effects. One reason for the popularity of this approach is because, consistent solutions of drift-diffusion approximation of the Boltzmann Transport Equation (BTE) and Poisson equation provide electric field distributions in addition to carrier concentration distributions [8]. Numerical solutions of drift-diffusion equations have good and fast convergence and hence are less time consuming than physically more accurate methods like Monte-Carlo simulations.

From an electric field perspective, impact ionization is characterized by an impact ionization rate,  $\alpha$ , which is defined as the number of electron-hole pairs generated by a hot-carrier in unit length. The relevant impact ionization generation rate equations for hot-electrons can be written as

$$G_n^{II} = \alpha_n \frac{|\vec{J_n}|}{q} \tag{2.1}$$

where,  $G_n^{II}$  is the generation rate,  $\vec{J_n}$  is the current density and q the elementary charge and

$$\alpha_n = \alpha_n^{\infty} \exp\left(-\left(\frac{E_n^{crit}}{E}\right)^{\beta_n}\right) \tag{2.2}$$

where, the prefactor is the impact ionization rate for infinite electric field, E the electric field in the direction of current flow,  $E_n^{crit}$  is the critical electric field for electrons to cause impact ionization, and the exponent  $\beta_n$  varies between 1 and 2 [5, 6, 7]. Values of  $E_n^{crit}$  found in the literature varies from  $10^6$  to  $5.87 \times 10^6 \ Vcm^{-1}$  and  $\alpha_n^{\infty}$  from  $6.2 \times 10^5$  to  $3.8 \times 10^6 cm^{-1}$  (for a compilation of literature values, refer to Selberherr [8].

Shockley [7] related  $G_n^{II}$  to the probability that an electron travels enough length through silicon without phonon scattering to gain the threshold energy for impact ionization. Shockley's model was termed the "lucky electron model" (LEM) for this reason. The electric field based models discussed so far were termed by Shockley as empirical because "a theoretical model should take into account the energy-band structure for energies greater than 1 eV (for silicon) from the band edges and should make use of the appropriate effective masses for hot-carrier effects."

When E is varying rapidly and also for low E values, the models based on local values of E overestimate impact ionization [9]. Impact ionization at any space coordinate will depend not only on the value of E at that particular location but also on its spacial distribution.

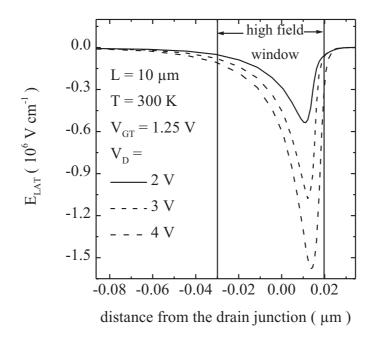

Hu et al. [4] applied LEM to the hot-carrier problems in nMOSFETs. Impact generated  $I_{SUB}$ , hot-electron emission current into the gate dielectric ( $I_G$ ) and interface damage were correlated to the peak lateral electric field ( $E_{LATpeak}$ ) through LEM.  $E_{LATpeak}$  was related to bias voltages and device parameters. Hot-carrier life time prediction algorithms based on this model are widely used [10].

The models discussed so far have the consequence that the maximum energy gained by any electron in a MOSFET is limited by the applied drain voltage  $(V_D)$ . This is because the current is flowing along the direction of the lateral field. The maximum energy gained by any single electron is given by,

$$W = -q \int_0^L \vec{E} \cdot d\vec{l} \tag{2.3}$$

$$= -q.(V_D + \Delta \Psi) \tag{2.4}$$

where L is the channel length and  $\Delta\Psi$  is the small electrostatic barrier between the source and the channel [11, 12, 13]. If we neglect  $\Delta\Psi$ , there should not be any impact ionization in silicon devices for  $qV_D$  less than the impact ionization threshold energy, which is equal to the bandgap energy  $(W_G)$  [7, 14], and no gate currents for  $qV_D$  less than  $\Delta W_C$ .

## 2.2.2 The Energy Balance Perspective

In short channel nMOSFETs, the lateral electric field  $(E_{LAT})$  is very high and the thermal equilibrium condition assumed in drift-diffusion formulations need not be valid over a significant portion of the channel. The electrons will have an effective temperature  $(T_E)$  that is much higher than the lattice temperature  $(T_L)$ . Carrier temperature gradient leads to thermal diffusion currents [15]. This can be accommodated by consistently

solving the energy balance equations along with the drift-diffusion equations and the Poisson equation. Energy balance equations include energy lost through phonon emission. The impact ionization generated  $I_{SUB}$ , and  $I_G$  can be modeled as functions of carrier temperature [15, 16, 17]. Energy conservation equations accommodate nonlocal nature of carrier heating. However, the details of the band structure are not taken into consideration. Further, this model assumes that the electron energy distribution (EED) can be represented by a Maxwell-Boltzmann distribution (MBD) with a single effective temperature.

Since the EED is represented by a MBD with a single  $T_E$ , it will extend much beyond the applied  $V_D$ . This is considered an inherent short coming of the energy balance formulations [17].

#### 2.2.3 The Monte-Carlo Method

State-of-the-art approach to carrier transport in semiconductor devices is to solve BTE using Monte-Carlo (MC) techniques [18, 19, 20]. In MC, trajectories of one or more carriers is traced at the microscopic level in a given device structure subject to the action of electric fields, device geometry and various scattering mechanisms. Carrier flight and scattering are stochastically treated in accordance with probabilities describing the physical processes. Consistent MC solutions also solve the Poisson equation. The outputs of MC are carrier energy distributions. Since the carriers are treated as particles, and BTE is a classical formulation, MC is essentially a classical approach to simulation.

The material physics can be correctly modeled by including full-band structure [21]. However, the band structure models used by various MC groups are different. For example, Fischetti et al. [22] and Bude et al. [12] employ full-band structure obtained using pseudopotential method, whereas Ghetti et al. [23] use an analytical band structure. The probabilities describing scattering mechanisms are determined empirically to fit experimental observations. For example, Cartier et al. determined impact ionization rate as a function of carrier energy by fitting empirical models to soft x-ray photoemission spectroscopy data [24]. Bude et al. [25] used impact ionization rates evaluated theoretically. Ghetti et al. [23] used the impact ionization rates from Bude et al. Since the band structures used by both the groups are different, Ghetti et al. have fine tuned deformation potentials to match experimental quantum yield data.

Since MC is a stochastic approach, the number of carriers to be simulated must be sufficiently high to obtain reliable statistics. Various statistical enhancement schemes and iteration schemes employed in MC simulations also result in varying degrees of simulation noise. Specifically C. Jungemann and B. Meinerzhagen [26, 27] warn that "without proper analysis of the stochastic error it is not possible to assess the accuracy or efficiency of MC device simulations and misleading results might be obtained". This problem is prohibitively serious in MOSFETs operating in the subthreshold regime, due to the low number of inversion layer carriers, and no reliable results can be obtained for this regime [28].

Despite the inconsistency in the models used by various groups and the inherent noise problems, MC method is fairly established and applied to investigate inversion layer transport at the limits of MOSFET scaling [29]. The technique has also been applied to identify novel flash memory programming mechanisms [12], and to investigate

hot-carrier reliability issues [23, 30]. The technique is highly suited to study processes with energy thresholds since the outcome of the simulations is EED. In the following sections, we will review results published by MC groups on MOSFET operation to understand the physics of low voltage hot-carrier effects.

## 2.3 Low Voltage Hot-Carrier Effects in nMOSFETs

In this section, a review of the reports of hot-carrier effects found in the literature is given. Cross-over effect in impact generated  $I_{SUB}$ , impact ionization and interface degradation for voltages below threshold voltages for the respective processes are discussed

At high  $V_D$ , inversion layer electrons in an nMOSFET can gain sufficiently high energy and cause impact ionization. The generated secondary electrons flow towards the drain and the holes flow towards the substrate contact [31]. The hole current measured at the substrate ( $I_{SUB}$ ) can be used to study impact ionization in nMOSFETs.  $I_{SUB}$  vs gate voltage ( $V_G$ ) curves have a characteristic bell shape [32, 33].

#### 2.3.1 The Cross-over Effect

$I_{SUB}$  in MOSFETs for large  $V_D$  shows a negative temperature dependence (increases as the temperature is decreased and vice versa). This is because of the less frequent energy losing electron-phonon scattering events and hence higher average energy of the electrons [10].

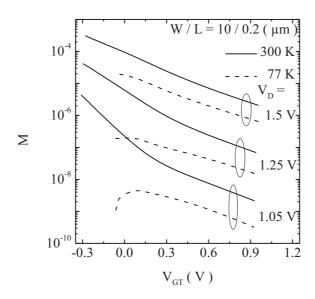

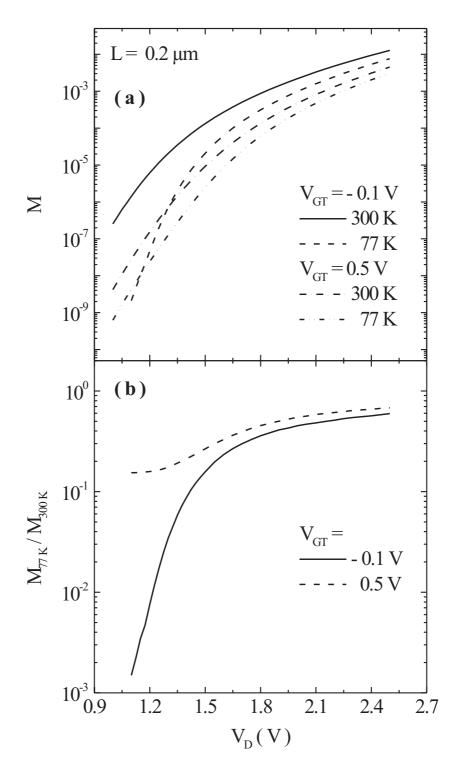

Eitan et al. [11] studied impact ionization in n-channel MOSFETs of channel length  $2.7 \,\mu m$  with gate oxide thickness of  $32.5 \,nm$  for  $V_D$  down to 1.05 V and reported a positive temperature dependence of  $I_{SUB}$  for  $V_D < 1.7 \,V$ . This was contrary to the observations till then. The phenomenon has since been studied by many researchers [23, 34, 35, 36, 37, 38, 39] and has lead to a better understanding of hot-carrier transport at low  $V_D$ .

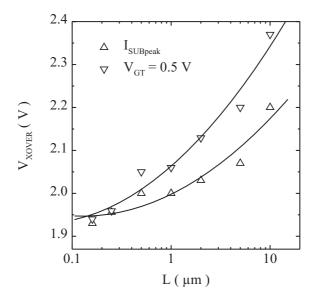

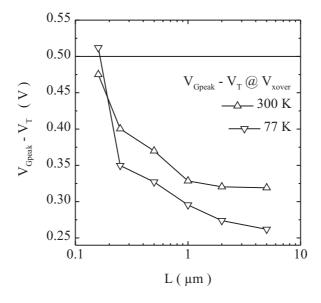

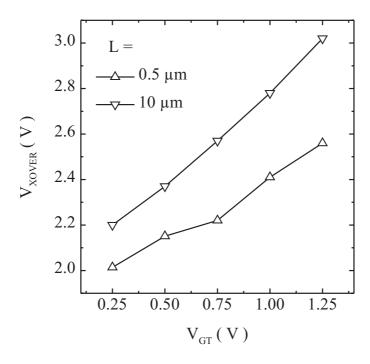

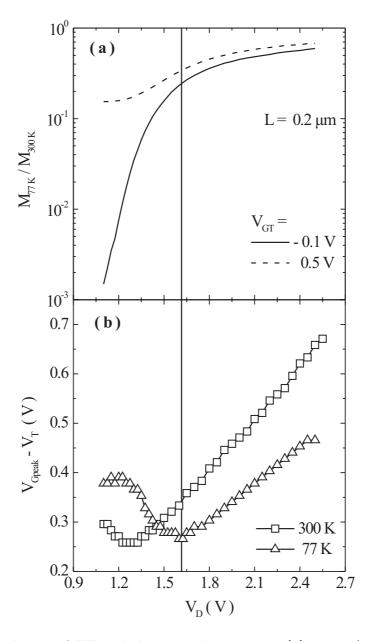

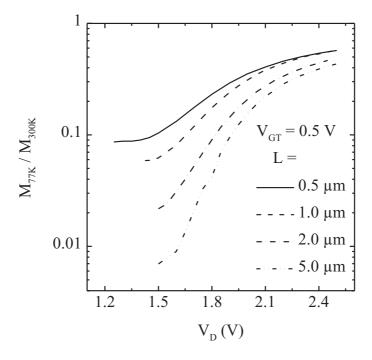

Henning et al. [34] christened the phenomenon as "cross-over" effect and termed the  $V_D$  at which  $I_{SUB}$  is independent of temperature as the "cross-over voltage"  $(V_{XOVER})$ . For  $V_D < V_{XOVER}$ ,  $I_{SUB}$  increases with increase in temperature and for  $V_D > V_{XOVER}$ , it decreases with increase in temperature. The value of  $V_{XOVER}$  reported in the literature varies from 1.75 to 2.6 V [11, 23, 35, 36, 37]. Henning et al. [34] reported that  $V_{XOVER}$  increases with channel length. Essani et al. [36] found that  $V_{XOVER}$  decreases with increasing  $V_G$ .

The experimental data reported in the literature on cross-over effect are summarized in table 2.1. Research groups other than cited in the table have also reported a reduced  $I_{SUB}$  at low  $V_D$  for low temperatures, for example [40]. The data given in table 2.1 is selected on the basis that,  $V_{XOVER}$  values are reported.

For quite some time it was speculated that the cross-over effect is due to the presence of a thermal tail in EED [11, 34]. Thermal tail means that the EED has an extension beyond  $qV_D$ , with a slope inversely proportional to the lattice temperature. Since impact ionization is caused by electrons having energy greater than  $W_G$ , the tail also contribute significantly to the process as  $qV_D$  approaches  $W_G$ . The thermal tail is greatly suppressed as the temperature is reduced, and hence  $I_{SUB}$  has to decrease with

| Ref. | $L_{eff} (\mu m)$ | $t_{OX} (nm)$ | $V_{XOVER} (V)$    |

|------|-------------------|---------------|--------------------|

| [11] | 2.7               | 25            | 1.75               |

| [34] | 33  to  0.95      | 38.5          | 2.6 to 1.8         |

| [35] | 5  to  0.09       | 4.8           | $2.3^{*}$          |

| [36] | 0.4  to  0.2      | 12            | $V_{GT}$ dependent |

| [23] | 0.22              | 12            | 2                  |

Table 2.1: Summary of representative data on cross-over effect reported in the literature.

temperature at low  $V_D$ .

Essani et al. [36, 37] employed  $I_G$  measurements on floating gate structures along with  $I_{SUB}$  measurements for  $V_D$  down to 1.4 V, which is well below  $V_{XOVER}$ . Even though  $I_{SUB}$  showed a cross-over,  $I_G$  did not show any cross-over. Since for this range of  $V_D$ ,  $I_G$  is caused by injection of the electrons occupying the tail of the EED into  $SiO_2$  from the channel, it should also show a cross-over if the thermal tail was behind the cross-over in  $I_{SUB}$ . Sano et al. [39] employing MC simulations argued that the widely reported  $V_{XOVER}$  of 2 V can not be explained by a thermal tail. The contribution of the field heated part of the EED, from  $W_G \sim 1.1 \ eV$ , to  $qV_D = 2 \ eV$ , to  $I_{SUB}$  would be much higher than that from the thermal tail for the temperature range usually investigated (77 to 300 K). This is because the effective temperature of the field heated part is much higher than  $I_L$ . Thermal tail alone could explain cross-over effect if  $qV_{XOVER}$  is close to  $W_G$ .

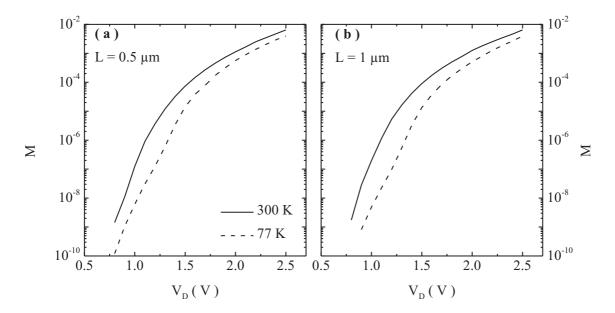

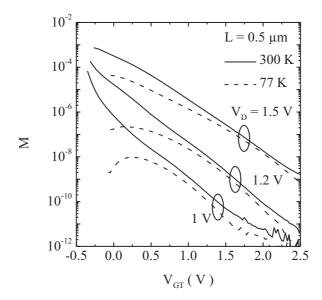

Fischetti and Laux, employing MC simulations, proposed that the cross-over effect is due to the increase in  $W_G$  of silicon as the temperature is reduced [38].  $W_G$  increases by about 40 meV when the temperature is reduced from 300 to 77 K [41, 42, 43]. MC simulations of Sano et al. [39] and Ghetti et al. [23] have since supported such a model. Ghetti et al. [23] could also reproduce the experimental  $I_{SUB}/I_D$ , referred to as quantum yield (M) hereafter, using their simulation model for n-channel MOSFETs of effective channel length 0.22  $\mu m$  and having gate oxide of thickness 10 nm. However, Sano et al. used a 65 meV increase in  $W_G$  in their simulations, which is much higher than the widely accepted value of  $40 \ meV$ .

A careful look at table 2.1 reveals that: (i)  $V_{XOVER}$  varies from 1.75 to 2.6 V for various technologies. (ii) the bias conditions used for the determination of  $V_{XOVER}$  are different. As is evident in the data in [36],  $V_{XOVER}$  may depend on bias conditions. (iii) For ultra-short channel devices,  $I_{SUB}$  is consistently low at low temperature upto large  $V_D$  values.

The channel length and gate voltage dependencies of  $V_{XOVER}$  remain unexplained. Also there is insufficient data in the literature on devices with ultra thin oxides.

## 2.3.2 Sub Bandgap Impact Ionization

From first order theory one would expect no impact generated  $I_{SUB}$  for  $qV_D < W_G$ . This is because, the net movement of inversion layer electrons are along the channel

<sup>\*</sup> for  $L_{eff} \leq 0.14~\mu m~I_{SUB}$  is reported to be consistently lower at 77 K than at 300 K for  $V_D$  upto 3V.

direction and the total potential drop experienced by them is  $qV_D$ .

Eitan et al. [11] reported bell shaped  $I_{SUB}$  vs  $V_G$  plots for  $V_D$  down to 1.05 V, for  $L=2.7 \,\mu m$  at 300 K. Tam et al. [44] reported  $I_{SUB}$  for  $V_D$  down to 0.85 V at 300 K. Chung et al. [45] reported  $I_{SUB}$  for  $V_D$  down to 0.7 V at 300 K. The last two papers have reported  $I_{SUB}$  vs  $V_D$  curves.  $I_{SUB}$  consists of impact generated hole current and drain junction leakage current. At very low  $V_D$ , the former component may be comparable or lower than the later and hence it can not be unambiguously said that the data are indications of sub-bandgap impact ionization.

Manchanda et al. [46] reported bell shaped  $I_{SUB}$  vs  $V_G$  plots for  $V_D$  down to 0.6 V at 170 K and 0.8 V at 300 K. There is an inconsistency with the reported cross-over effects in this case. Since at such low  $V_D$ ,  $I_{SUB}$  is reported to decrease with temperature, for a given measurement resolution, we would expect bell shaped  $I_{SUB}$  vs  $V_G$  for lower  $V_D$  at 300 K than at 170 K. According to the authors, "we observed simultaneous reductions in the threshold voltage for impact ionization and the impact ionization current at low temperatures". One of the reasons for this obvious discrepancy may be the dominance of the component of drain junction leakage in  $I_{SUB}$ , which is the thermal generation current of the reverse biased drain-substrate junction and hence decreases with temperature. They also reported an increase in the minimum  $V_D$  at which impact ionization could be measured ( $V_{Dmin}$ ), as the channel length was increased.

Koyanagi et al. [40] reported bell shaped  $I_{SUB}$  vs  $V_G$  for  $V_D$  down to 1 V at 300 K. They also reported a decrease in  $I_{SUB}$  as the temperature was reduced to 77 K. Balestra et al. [47] reported bell shaped  $I_{SUB}$  vs  $V_G$  data for  $V_D$  down to 1 V at 300 K and 1.2 V at 77 K. At 77 K they also observed an anomalous increase in the  $V_G$  at which  $I_{SUB}$  peaks ( $V_{Gpeak}$ ) as the  $V_D$  was reduced. However this behavior was not explained.

A. Hori et al. [48] investigated low voltage impact ionization in devices with gate oxides of thickness 4 and 8 nm. They could measure bell shaped  $I_{SUB}$  vs  $V_G$  for  $V_D$  down to 0.9 V for the thinner oxide device and down to 0.8 V for the thicker oxide device. An increase in  $V_{Gpeak}$  at low  $V_D$  can be discerned in their data even though they have not noted this in the paper.

Odanaka and Hiroki [49] compared the reliability performance of conventional and laterally asymmetric channel devices of channel lengths  $0.15 \,\mu m$ . They could measure bell shaped  $I_{SUB}$  vs  $V_G$  for  $V_D$  down to 1V. Anomalous increase in  $V_{Gpeak}$  is discernible in their data as well, even though they have not noted it in their paper.

Saraya et al. [50] reported observation of kink in the output characteristics of SOI devices for  $V_D$  down to 0.75 V.

Except for Eitan at al. [11], none of the above reports have considered why and how there can be hot-carriers with energy higher than the applied drain bias. Emphasis in most of these studies was whether impact ionization can be observed for  $qV_D < W_G$ , not on the physical mechanisms responsible. Eitan et al. suggested that the EED has a thermal tail because the EED keep a "memory" of its initial equilibrium distribution. This point will be considered in detail later.

### 2.3.3 Sub-barrier Electron Injection into the Gate Dielectric

When direct tunneling is negligible and oxide field is low so that Fowler-Nordheim tunneling can be ignored, only those electrons having energy higher than  $\Delta W_C$  get injected into the dielectric. From first order considerations we would expect no  $I_G$  for

$qV_D < \Delta W_C$ . For the  $Si-SiO_2$  system, we would expect no injection for  $V_D < 3.1~V$ . Ricco et al. [51] measured significant charging of the floating gate of floating gate nMOSFETs for  $V_D$  down to 1.4 and 1.8 V at 77 and 300 K respectively. They attributed it to hot-electron injection. Similar measurements were also reported by Sangiorgi et

al. [52] and Essani et al. [36]. Gate oxide thicknesses in all these case were more than 10 nm. Chung et al. [45] reported gate currents for  $V_D$  down to 1.8 V using sensitive direct current measurement techniques.

$\Delta W_C$  can be smaller than the theoretical values due to the presence of charges at the interface [43]. However the lowest value for  $Si - SiO_2$  is about 2.5 eV [53]. This means that  $I_G$  reported at such low voltages as in the previous paragraph are caused by electrons having energy much higher than the applied  $V_D$ .

Electron injection at such low  $V_D$  has serious consequence for long-term retention reliability of flash memory cells.  $V_D$  values discussed in the previous paragraphs lie in the operating voltage range of such devices. Long term operation of the devices at such voltages can change a stored "one" (no charge on the floating gate) to "zero" by cumulative low voltage electron injection [23].

#### 2.3.4 Hot-Carrier Reliability at Low Drain Voltages

There have been many microscopic models of hot-carrier degradation proposed in the past. A review of them is interesting from the perspective of threshold energy for degradation.

Hot-electron model suggested that energetic electrons break Si-H bond to produce trivalent silicon (interface traps) and interstitial hydrogen atom. Threshold energy associated with the process is equal to bond energy plus the barrier energy, about 3.7 eV [4].

According to trapped hole recombination model, hot holes are injected into the dielectric and get trapped. Subsequently they capture an electron and recombine. The energy released in this process breaks Si-H bonds [54]. This process is limited by hot hole injection and with a valance band discontinuity of about 4.1 eV for the  $Si-SiO_2$  system [43] has a higher threshold than the hot-electron injection model.

Bude et al. [30] investigated threshold energy for hot electron induced interface state generation using MC simulations. MC simulations were used to obtain EED. An empirical interface state generation model which has a tunable threshold energy was used to correlate the simulated EED to measured degradation data. Best fit of model to experiment was found for a threshold of 3.5 eV for interface state generation. Recently, Mu et al. [55] applying an extension of LEM to degradation data, found a value of 3.2 eV for the threshold energy.

K. Hess et al. [53] suggested that the breaking of Si-H bonds is through vibrational excitations. The bonds can also be broken by multiple vibrational excitations. This model was prompted by the improvement of hot carrier robustness of interfaces annealed in deuterium compared to those annealed in hydrogen [56, 57]. Since the bonding energy of Si-H and Si-D are the same, a chemical picture should give identical interface qualities for both the isotopes. Multiple vibrational excitations, if the real reason for the improved robustness of deuterium annealed interfaces, can make the process a soft threshold one.

Takeda et al. [58] reported degradation of  $Si-SiO_2$  interface for  $V_D$  down to 2.5 V.

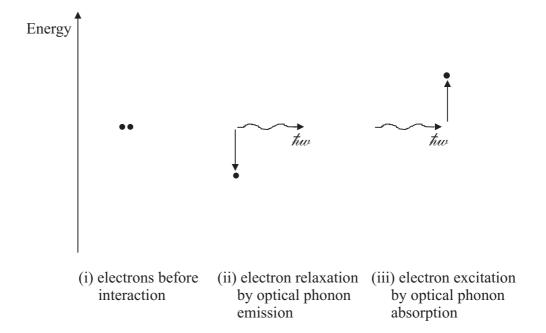

Figure 2.2: Schematic illustrating EPI as a process that can extent the EED tail beyond the applied bias [62]. (i) monoenergetic electrons having energy equal to the applied bias, assumed for ease of understanding, before interactions. (ii) one of the electrons relax by emitting an optical phonon. (iii) Another electron absorb the emitted phonon extending the EED beyond the applied bias.

Rauch et al. [59] reported measurable degradation for  $V_D$  down to 2 V. Mahapatra et al. [60] deported degradation down to 1.9 V.

Even though threshold energy for the degradation process is controversial, high energy electrons are bound to cause greater damage. From this perspective it is important to know carrier heating beyond applied biases for deep-sub micron devices.

## 2.4 Carriers with Energy Greater than $qV_D$

In this section, possible mechanisms that populate the EED beyond the applied  $V_D$  are reviewed. Most of the discussion center around simulation results published by MC groups.

# 2.4.1 Electron-Phonon Interactions as an Energy Redistribution Mechanism

Eitan et al. [11], assuming impact ionization as the only scattering in the pinch-off region of MOSFETs, derived an expression for  $I_{SUB}$  that depends exponentially on  $T_L$ . They argued that EED keeps "memory" of its source side equilibrium condition. However, no physical explanation was given.

Mahan [61] analytically solved BTE in silicon in one dimension, accounting for ionized impurity scattering and electron-phonon interactions. Electrons with MBD launched into a uniform field emerges with a distribution that has two parts. For

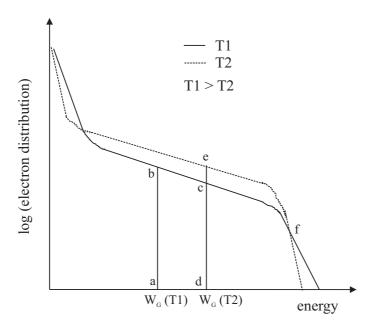

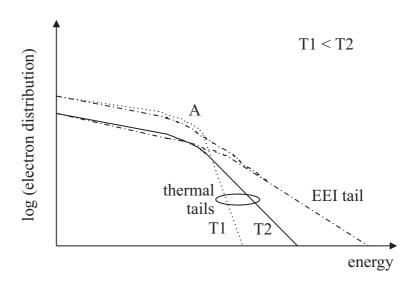

W < qV, the distribution was described by MBD with  $T = T_E$ , where  $T_E$  is the effective temperature. For W > qV, the distribution was described by an MBD with  $T = T_L$ , where  $T_L$  is the lattice temperature. Since the maximum energy that can be gained by the electrons from the field is qV, that part of the EED beyond qV is called the tail. When the tail has an effective temperature equal to the lattice temperature it is called a thermal tail.

Analytical treatments of Lacaita [63] also predicted a thermal tail. The explanation for the presence of the thermal tail according to Lacaita, as understood by the present author, is as follows. An electron ensemble which is in thermal equilibrium with the lattice follows a distribution which has a tail that is well described by MBD with  $T = T_L$ . The energy gained by the electron ensemble from the lattice by phonon absorption is balanced by the energy lost to it by phonon emission. When a high electric field is applied, the rate at which the electrons gain energy from the field exceeds the electron-optical phonon scattering rate multiplied by phonon energy. The electron ensemble is no more in equilibrium with the lattice. The maximum energy that any electron in the ensemble can gain from the field is qV. Now we consider those electrons which have energy equal to qV, as in figure 2.2(i). One of the electrons losses part of its energy by emitting an optical phonon, figure 2.2(ii). Of the various possibilities available to the emitted phonon, we consider the case of it being absorbed by another electron as shown in figure 2.2(iii). The result of the sequence of the processes depicted is an extension of the distribution beyond qV. Step (iii) in the process can at best have the same rate as the step (ii), because the inverse condition would imply cooling of the lattice. The electrons in an interaction involving a phonon can either emit or absorb a phonon. We assume that the events have equal probabilities. For the electrons beyond qV edge, this would mean a quasi-equilibrium with the lattice in the sense that the phonon absorption and emission are balanced. Consequently the distribution beyond qV has an effective temperature equal to the lattice temperature.

MC simulations have supported the presence of a thermal tail in the EED [23, 38, 39, 64, 65, 66, 67, 68, 69].

The energy exchanged in EPI are limited to the energy of optical phonons. In silicon, the highest optical phonon energy is 63 meV [43].

A minor comment about the nomenclature is in order. MC simulation groups refer to EPI as an energy gain mechanism. The phonon absorbed by any electron in the interaction was emitted by some other electron which in turn gained this energy from field heating. Describing the mechanism as an energy redistribution mechanism is more appropriate and closer to the physical process involved and hence the title of the subsection. Electron energy is redistributed with the phonons acting as intermediary.

# 2.4.2 Electron-Electron Interactions as an Energy Redistribution Mechanism

Ensemble MC simulations have also predicted EEI as a major energy gain mechanism that would extend the distribution much beyond the qV limit [23, 38, 67, 68, 69]. Two kinds of EEI are identified, namely a short-range component and a long-range component. Except in the work of Fischetti and Laux [38, 70, 71], the long-range component is not explicitly included in any of the MC codes reported in the literature.

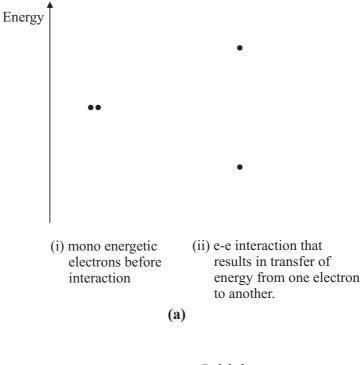

Figure 2.3: Schematic illustrating the short-range electron-electron Coulomb interactions as an EED broadening mechanism [62]. (a) (i) two monoenergetic electrons before interaction (ii) after interaction. One of the electrons have relaxed by transferring part of its energy to the other electron. (b) an initially narrow EED broadened by EEI.

#### 2.4.2.1 Short-Range Electron-Electron Interactions

One-to-one interaction of electrons are termed short-range interactions (SREEI). How SREEI influence the distribution is schematically illustrated in figure 2.3. Let us consider monoenergetic electrons as depicted in figure 2.3a(i). The interaction between these two electrons can result in one of the electron relaxing by giving a part of its excess energy to the other electron, figure 2.3a(ii). If we consider an ensemble of electrons with a narrow initial energy distribution as depicted by the solid line in figure 2.3b and also considering the fact that the interacting electrons need not have equal initial energies, the consequence of the interactions would be a broadening of the distribution as depicted by the dotted line in the same figure.

Higher the energy of the interacting electrons, greater the extent of population beyond the qV limit. Consequently, SREEI are important in the high field region of the MOSFET. In contrast to EPI, where the energy exchanged is limited by the optical phonon energy, SREEI are more effective since the energy exchanged can be the excess energy of the higher energy electrons, which can be significantly higher than that of an optical phonon.

For a given field distribution, SREEI increases with increasing electron density [65, 68]. This is because, with increasing electron density electron-electron interactions become more frequent.

In the case of SREEI also, the energy gained by the electrons from the field is redistributed within the ensemble due to the interactions. MC groups have termed the mechanism as an energy gain mechanism. As mentioned in [72] "energy redistribution mechanism" is probably a more self describing phrase.

#### 2.4.2.2 Long-Range Electron-Electron Interactions

Long-range electron interactions (LREEI) arise due to the fact that the Coulomb interaction extent beyond one Debye length [73]. LREEI is usually treated as plasma excitations induced by a high energy electron in an electron bath in equilibrium. A typical example is the interaction of high energy channel electrons with the cold electrons in the drain region of an n-channel MOSFET. MC simulations by Fischetti and Laux have shown that LREEI component can have a significant impact on the tail of the distribution function [38]. For example, the high energy channel electron entering the drain in a sequence of interactions with the cold electrons involving absorption of the energies of the cold electrons can gain a significantly high energy. Since average energy of the cold electrons in the drain is  $1.5kT_L$ , the efficiency of this mechanism compared to SREEI may not be significant.

The LREEI can also indirectly effect the distributions [74, 75]. The long-range nature implies that the Coulomb force of the drain electrons can be felt even in the pinch-off region of the MOSFET. This repulsive force can randomize the trajectories of the channel electrons reducing their effective mobility. The slowed down electrons have more time for interactions. In short, the long-range interaction can enhance SREEI and EPI.

MC simulations by Fischetti and Laux [74] have also predicted that LREEI in heavily doped silicon can increase the average energy of the electrons. The simulations were done for zero electric field condition. The increase in average kinetic energy was given by

Figure 2.4: Schematic of electron energy distribution near the drain junction of an n-channel MOSFET, based on the results published by MC simulation groups [23, 38, 39]. The distribution can be divided into three regions which are marked as I, II and III. Region I represent electrons that are in thermal equilibrium with the lattice. Region II represent electrons that can be described by an "effective temperature". Region III corresponds to electrons which have energy greater than  $qV_D$ , where  $V_D$  is the applied drain bias.

$$\delta W_K = 1.451 \kappa n^{1/3} \tag{2.5}$$

where

$$\kappa = \frac{q^2}{4\pi\epsilon_{Si}\epsilon_0} \tag{2.6}$$

where n is the density of the electron gas, q the elementary charge,  $\epsilon_{Si}$  the static relative permittivity of silicon and  $\epsilon_0$  the absolute permittivity of free space.

From equation 2.5, the increase in the average kinetic energy for doping of  $10^{18}$  and  $10^{21}cm^{-3}$  are 17.5 and 175 meV respectively.

Fischetti and Laux further predicted that LREEI can result in high energy tails in EED of a stationary electron gas. Such tails have effective temperatures much higher than the lattice temperature. They found effective temperature values of 390 and 1205 K for donor doping levels of  $10^{19}$  and  $10^{20} cm^{-3}$  respectively.

## 2.4.3 Electron Energy Distribution in n-channel MOSFETs

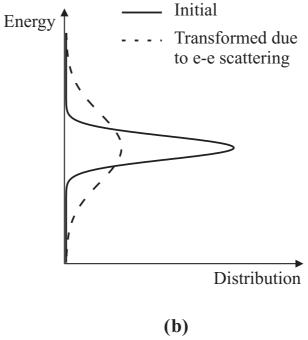

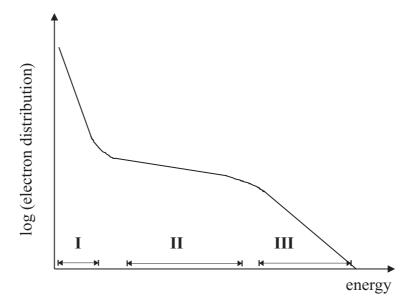

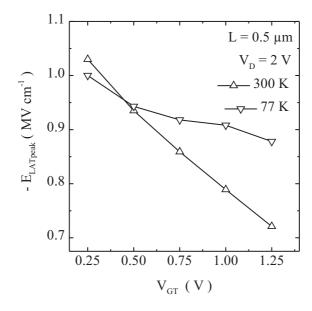

Schematic of EED near the drain junction of conventional n-channel MOSFETs published by MC simulation groups is shown in figure 2.4. It is based on the data published in [23, 38, 39]. EED is divided into three regions to facilitate understanding.

Region I is occupied by electrons which are in thermal equilibrium with the lattice and the line has a slope of  $-1/kT_L$ , where  $T_L$  is the lattice temperature. Region II

correspond to the field driven high energy electrons. The slope of the segment is  $-1/kT_E$ , where  $T_E$  is the effective temperature of the electrons. Region II extends till energy approximately equal to  $qV_D$  for deep sub-micron structures. The vicinity of  $qV_D$  correspond to the electrons ballistically transported from the source to drain. Region III is beyond  $qV_D$  and is called the high energy tail of the distribution. As was discussed, the tail can be a thermal tail with slope of  $-1/kT_L$  or EEI induced.

#### 2.4.4 Discussion

Any numerical analysis of problems in physics is at best predictive. They either follow an experimental observation or predict physical phenomenon based on state-of-the-art understanding of physics. In the later case it is imperative to verify the predictions experimentally to confirm them. In the following we would review the literature to assess if there are sufficient experimental support to EPI, SREEI and LREEI as energy redistribution mechanisms.

The EED can be experimentally investigated using hot-carrier luminescence measurements [76, 77]. But this technique is not suited to investigate the tail of the EED beyond qV due to inadequate sensitivity.

Experimental support to SREEI broadening of EED tail has come from the observation that M is underestimated in comparison to measured data when SREEI is turned off in MC simulation [12, 23]. Interestingly, Bude and Mastrapasqua [25] could reproduce measured  $I_{SUB}/I_D$  down to a  $V_D$  of 1.2 V without including SREEI whereas in the work of Ghetti et al., M was underestimated for  $V_D$  below 1.6 V when SREEI were turned off in the simulations. Bude et al. [12] found that  $I_G/I_D$  was underestimated for  $V_D$  below 3.1 V when SREEI was not included. It should be noted that  $I_{SUB}$  is caused by the part of EED above 1.1 eV whereas  $I_G$  is caused by the part above 3.1 eV.  $I_G$  estimates have the additional complexity of accounting for the tunneling probability of electrons through the oxide [78]. Both the groups have modeled only SREEI in their code.

Bude et al. [30] found it necessary to include SREEI to correctly model threshold energy for interface degradation. Rauch et al. [59] reported that hot-carrier degradation in devices of  $0.085 \,\mu m$  effective channel length showed increasing trend as  $V_G$  was increased. This is in contrast to the widely held view that the degradation is maximum for stress at maximum  $I_{SUB}$  condition or for  $V_G = V_D/2$  bias [4, 55, 60, 79, 80]. Investigations of Mahapatra et al. [60] were also on devices with drawn channel length of  $0.1 \,\mu m$  (effective channel length  $\sim 0.08 \,\mu m$ ). Rauch et al. explained their results as due to SREEI. Hess et al. [53] have expressed apprehensions whether SREEI can be so strong to produce observable degradation.

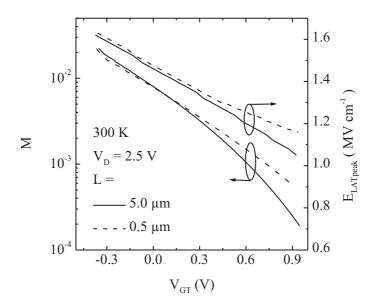

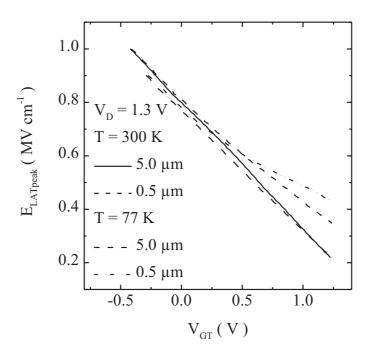

The assumption of Rauch et al. [59] that SREEI enhances as  $V_G$  is increased is justified for an unchanging electric field distribution. However, in the case of a MOS-FET, even though the inversion layer charge density increases with  $V_G$ , field heating decreases with increasing  $V_G$  due to the reduction of  $E_{LATpeak}$ . Impact of  $V_G$  variations on SREEI is not clear.

There is yet to be any experimental proof for the thermal tail. SREEIs are important when the channel electron concentration is very high. Abramo et al. [65] and Ghetti et al. [23] have used a threshold of  $10^{17}cm^{-3}$  for the electron concentration for SREEI to be significant. Based on this, MC simulations can provide a proof of the

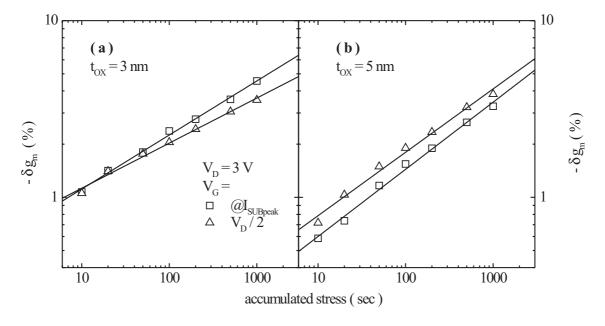

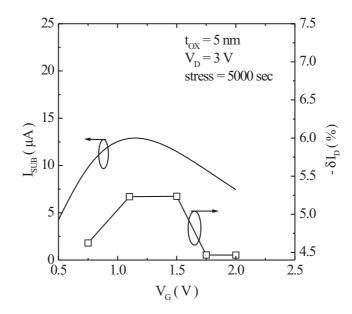

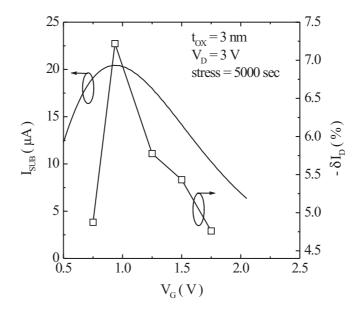

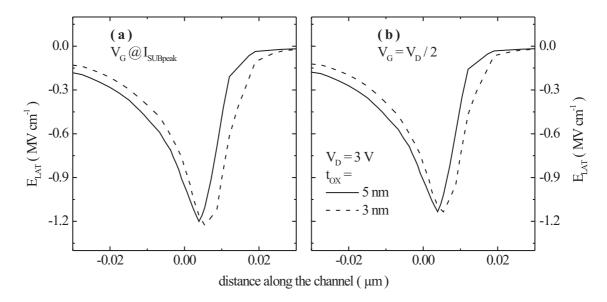

2.5. Summary 19