# Fault Simulation - II

# Virendra Singh

#### Associate Professor

Computer Architecture and Dependable Systems Lab

Dept. of Electrical Engineering Indian Institute of Technology Bombay viren@ee.iitb.ac.in

EE 709: Testing & Verification of VLSI Circuits Lecture – 9 (Jan 23, 2012)

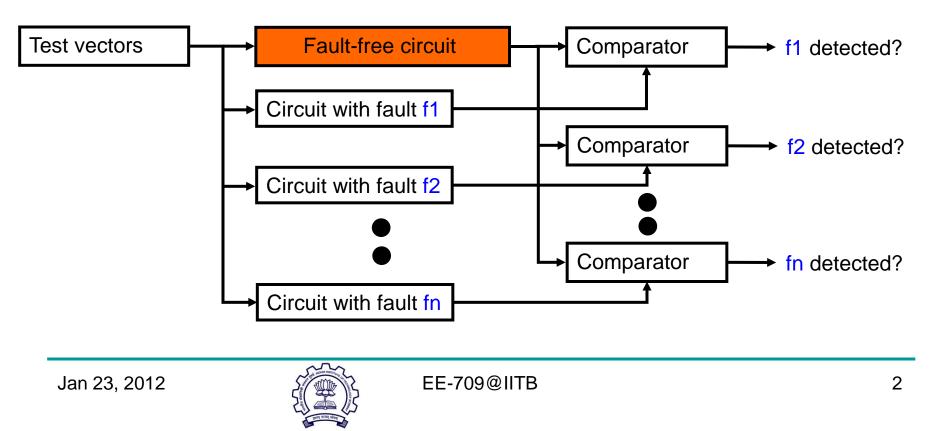

# **Serial Algorithm**

Disadvantage: Much repeated computation; CPU time prohibitive for VLSI circuits

> Alternative: Simulate many faults together

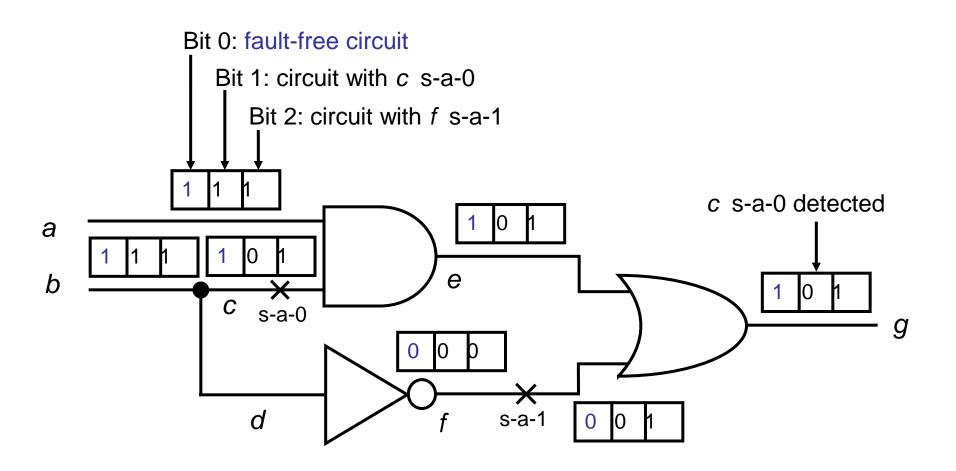

# **Parallel Fault Simulation**

- Compiled-code method; best with two-states (0,1)

- Exploits inherent bit-parallelism of logic operations on computer words

- Storage: one word per line for two-state simulation

- Multi-pass simulation: Each pass simulates w-1 new faults, where w is the machine word length

- Speed up over serial method ~ w-1

- Not suitable for circuits with timing-critical and non-Boolean logic

### **Parallel Fault Simulation**

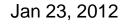

#### **Deductive Fault Simulation**

- One-pass simulation

- Each line k contains a list L<sub>k</sub> of faults detectable on k

- Following true-value simulation of each vector, fault lists of all gate output lines are updated using set-theoretic rules, signal values, and gate input fault lists

- PO fault lists provide detection data

- Limitations:

- Set-theoretic rules difficult to derive for non-Boolean gates

- Gate delays are difficult to use

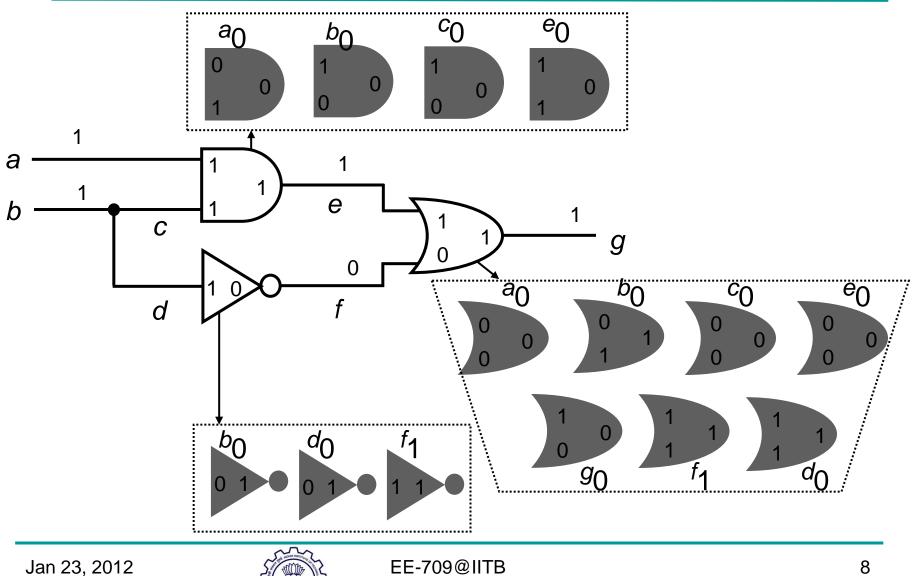

#### **Deductive Fault Simulation**

Notation:  $L_k$  is fault list for line k  $k_n$  is s-a-n fault on line k

#### **Concurrent Fault Simulation**

- Event-driven simulation of fault-free circuit and only those parts of the faulty circuit that differ in signal states from the fault-free circuit.

- A list per gate containing copies of the gate from all faulty circuits in which this gate differs. List element contains fault ID, gate input and output values and internal states, if any.

- All events of fault-free and all faulty circuits are implicitly simulated.

- Faults can be simulated in any modeling style or detail supported in true-value simulation (offers most flexibility.)

- Faster than other methods, but uses most memory.

### **Conc. Fault Simulation**

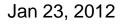

# Fault Sampling

- A randomly selected subset (sample) of faults is simulated.

- Measured coverage in the sample is used to estimate fault coverage in the entire circuit.

- Advantage: Saving in computing resources (CPU time and memory.)

- Disadvantage: Limited data on undetected faults.

# **Motivation for Sampling**

- Complexity of fault simulation depends on:

- Number of gates

- Number of faults

- Number of vectors

- Complexity of fault simulation with fault sampling depends on:

- Number of gates

- Number of vectors

# **Random Sampling Model**

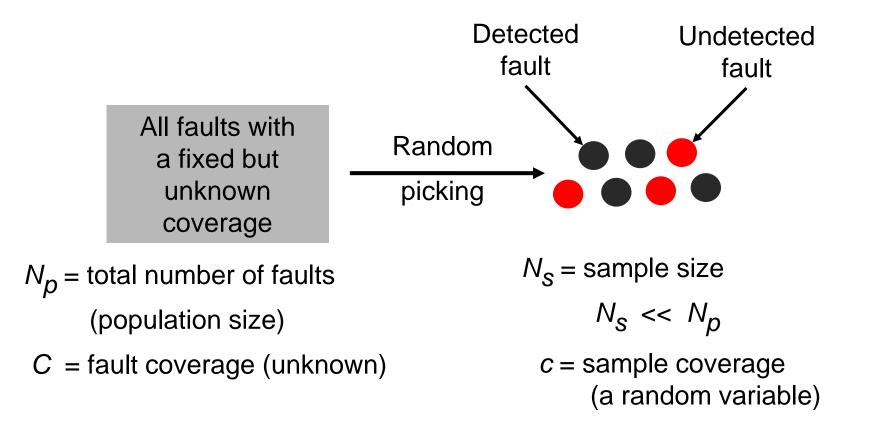

# Probability Density of Sample Coverage, c

# Thank You

EE-709@IITB