# RISC Architecture: Pipelining

## Virendra Singh

**Associate Professor**

Computer Architecture and Dependable Systems Lab

Department of Electrical Engineering

Indian Institute of Technology Bombay

http://www.ee.iitb.ac.in/~viren/

E-mail: viren@ee.iitb.ac.in

# Computer Organization & Architecture

Lecture 17 (30 April 2013)

**CADSL**

#### Pipeline Hazards

- Definition: Hazard in a pipeline is a situation in which the next instruction cannot complete execution one clock cycle after completion of the present instruction.

- Three types of hazards:

- Structural hazard (resource conflict)

- Data hazard

- Control hazard

# Possible Remedies for Structural Hazards

- Provide duplicate hardware resources in datapath.

- Control unit or compiler can insert delays (noop cycles) between instructions. This is known as pipeline stall or bubble.

#### Stall (Bubble) for Structural Hazard

May 2013

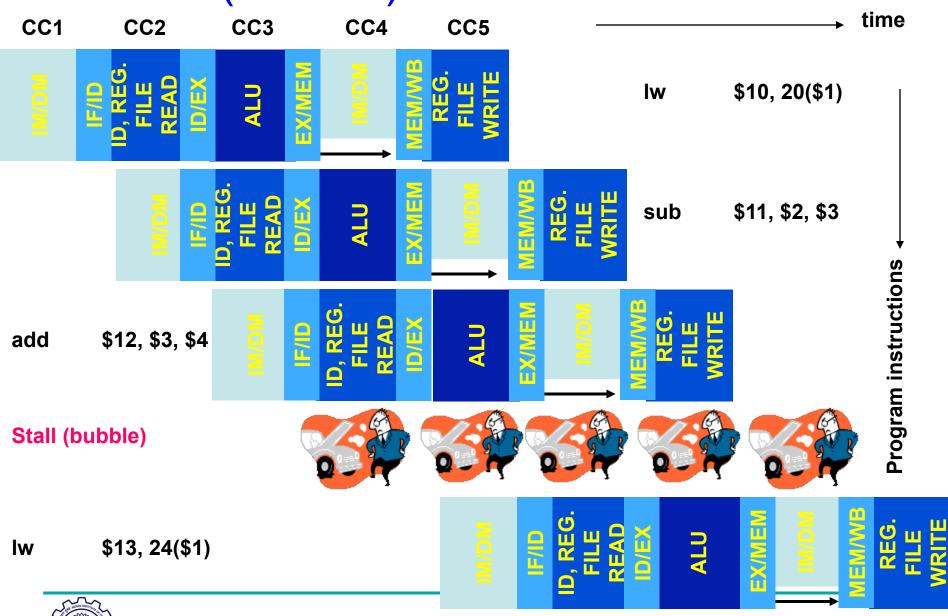

#### **Data Hazard**

- Data hazard means that an instruction cannot be completed because the needed data, to be generated by another instruction in the pipeline, is not available.

- Example: consider two instructions:

# Forwarding or Bypassing

- Output of a resource used by an instruction is forwarded to the input of some resource being used by another instruction.

- Forwarding can eliminate some, but not all, data hazards.

## Resolving Hazards

- ➤ Hazards are resolved by Hazard detection and forwarding units.

- Compiler's understanding of how these units work can improve performance.

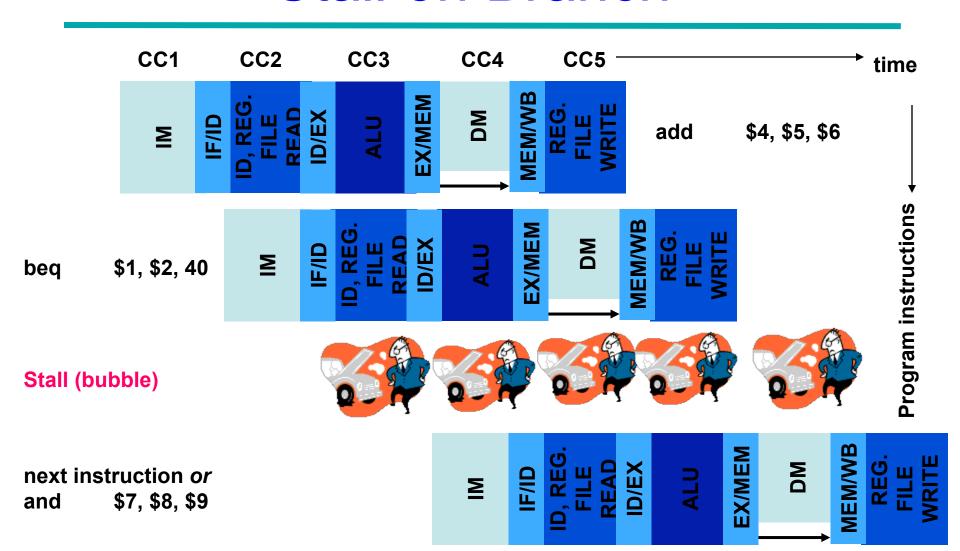

#### Control Hazard

- Instruction to be fetched is not known!

- Example: Instruction being executed is branch-type, which will determine the next instruction:

```

add $4, $5, $6

beq $1, $2, 40

```

next instruction

40and \$7, \$8, \$9

#### Stall on Branch

## Why Only One Stall?

- Extra hardware in ID phase:

- Additional ALU to compute branch address

- Comparator to generate zero signal

- Hazard detection unit writes the branch address in PC

## Ways to Handle Branch

- Stall or bubble

- Branch prediction:

- Heuristics

- Next instruction

- Prediction based on statistics (dynamic)

- Hardware decision (dynamic)

- Prediction error: pipeline flush

- Delayed branch

#### Delayed Branch Example

Stall on branch

add \$4, \$5, \$6

beq \$1, \$2, skip

next instruction

skip or \$7, \$8, \$9

Delayed branch

beq \$1, \$2, skip

add \$4, \$5, \$6

next instruction

...

skip or \$7, \$8, \$9

Instruction executed irrespective of branch decision

# Thank You