# RISC Architecture: Pipeline Hazard

#### Virendra Singh

**Associate Professor**

Computer Architecture and Dependable Systems Lab

Department of Electrical Engineering

Indian Institute of Technology Bombay

http://www.ee.iitb.ac.in/~viren/

E-mail: viren@ee.iitb.ac.in

# Computer Organization & Architecture

Lecture 19 (06 May 2013)

**CADSL**

#### Pipeline Hazards

- Definition: Hazard in a pipeline is a situation in which the next instruction cannot complete execution one clock cycle after completion of the present instruction.

- Three types of hazards:

- Structural hazard (resource conflict)

- Data hazard

- Control hazard

# Ways to Handle Branch

- Stall or bubble

- Delayed branch

- Branch prediction:

- Heuristics

- Next instruction

- Prediction based on statistics (dynamic)

- Hardware decision (dynamic)

- Prediction error: pipeline flush

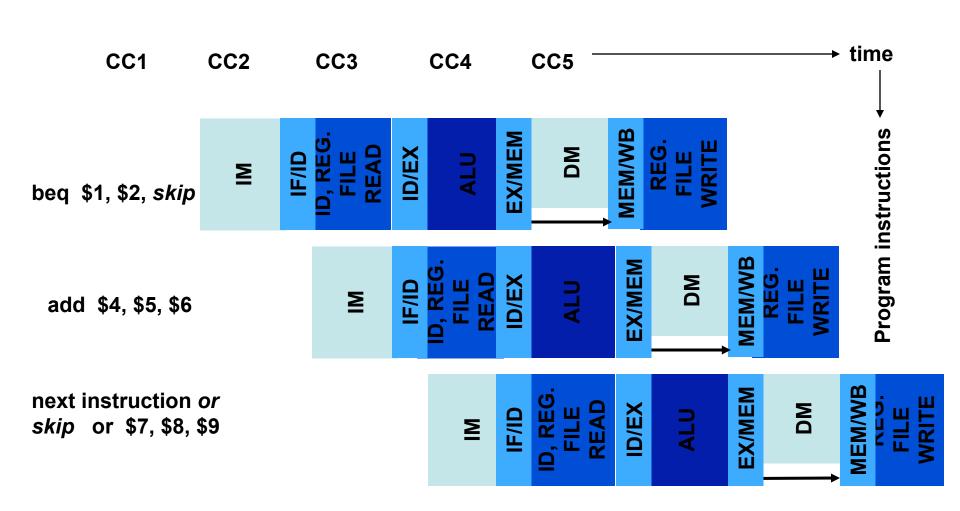

### Delayed Branch Example

Stall on branch

add \$4, \$5, \$6

beq \$1, \$2, skip

next instruction

skip or \$7, \$8, \$9

Delayed branch

beq \$1, \$2, skip

add \$4, \$5, \$6

next instruction

...

skip or \$7, \$8, \$9

Instruction executed irrespective of branch decision

# **Delayed Branch**

#### **Branch Hazard**

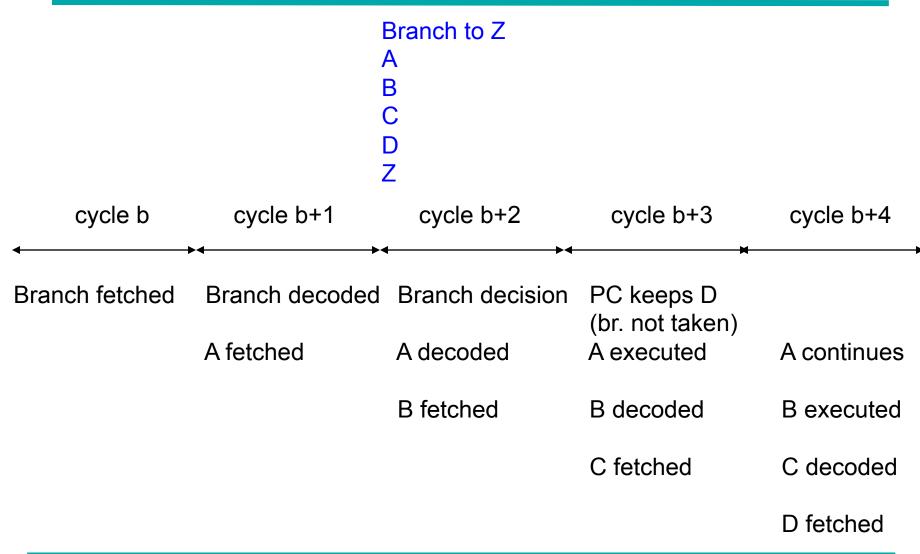

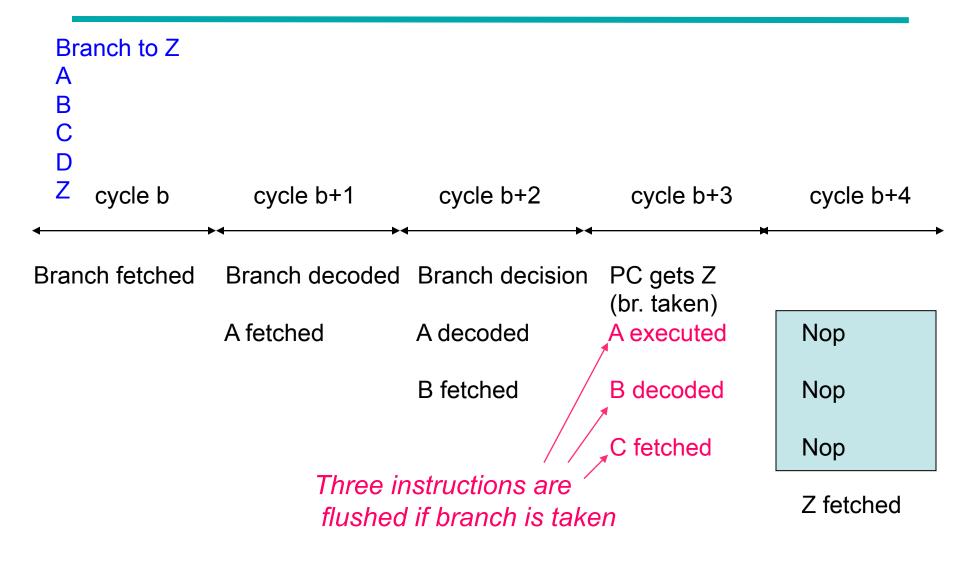

- Consider heuristic branch not taken.

- Continue fetching instructions in sequence following the branch instructions.

- If branch is taken (indicated by zero output of ALU):

- Control generates branch signal in ID cycle.

- branch activates PCSource signal in the MEM cycle to load PC with new branch address.

- Three instructions in the pipeline must be flushed if branch is taken – can this penalty be reduced?

#### **Branch Not Taken**

#### **Branch Taken**

# Thank You