# RISC Design: Multi-Cycle Implementation

#### Virendra Singh

**Associate Professor**

Computer Architecture and Dependable Systems Lab

Department of Electrical Engineering

Indian Institute of Technology Bombay

http://www.ee.iitb.ac.in/~viren/

E-mail: viren@ee.iitb.ac.in

### CP-226: Computer Architecture

Lecture 9 (19 Feb 2013)

**CADSL**

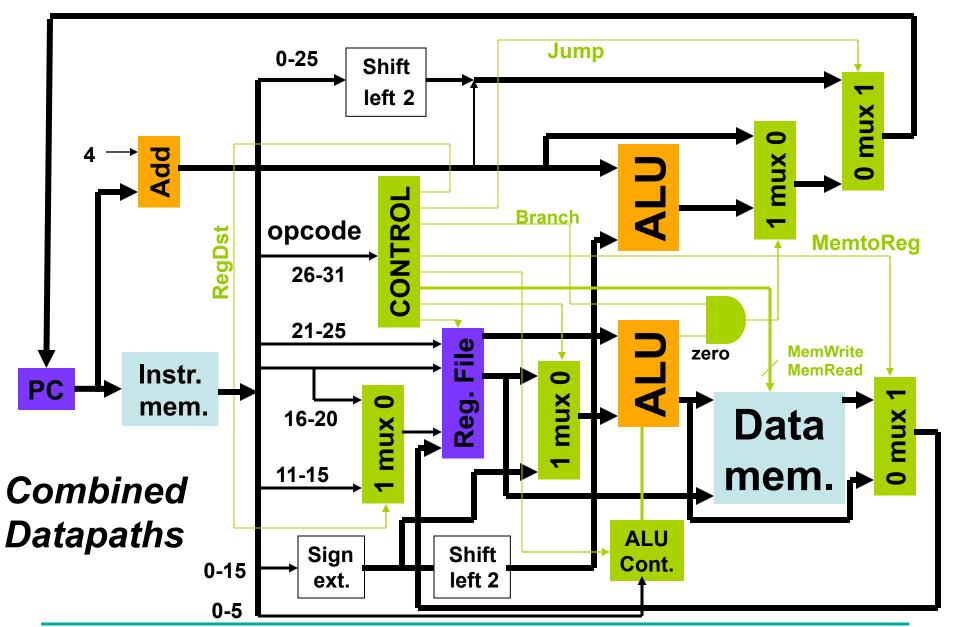

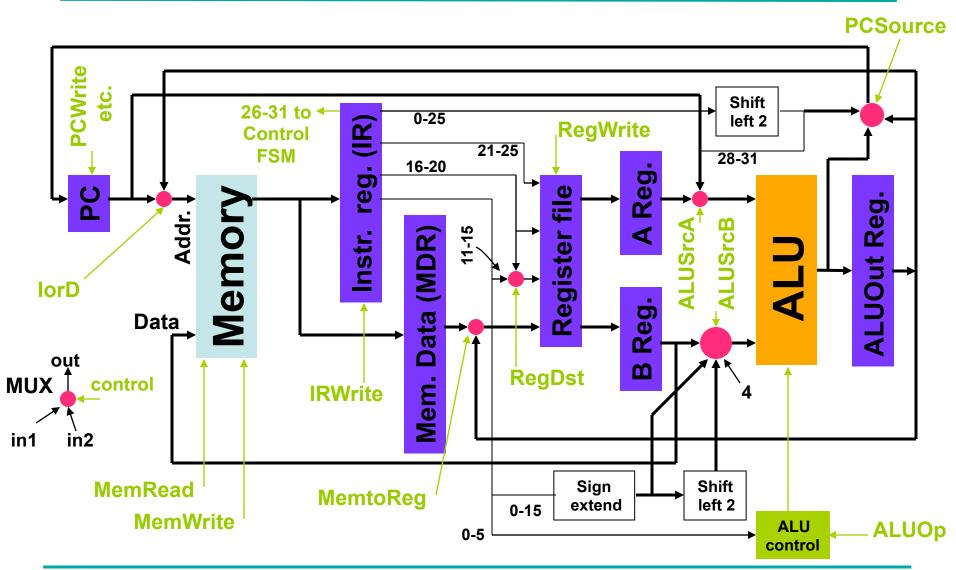

#### Multicycle Datapath

#### 3 to 5 Cycles for an Instruction

| Step                                             | R-type<br>(4 cycles)                                                              | Mem. Ref.<br>(4 or 5 cycles)            | Branch type (3 cycles)          | e J-type<br>(3 cycles)                  |

|--------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|---------------------------------|-----------------------------------------|

| Instruction fetch                                | IR ← Memory[PC]; PC ← PC+4                                                        |                                         |                                 |                                         |

| Instr. decode/<br>Reg. fetch                     | A ← Reg(IR[21-25]); B ← Reg(IR[16-20])  ALUOut ← PC + (sign extend IR[0-15]) << 2 |                                         |                                 |                                         |

| Execution, addr. Comp., branch & jump completion | ALUOut ←<br>A op B                                                                | ALUOut ←<br>A+sign extend<br>(IR[0-15]) | If (A= =B)<br>then<br>PC←ALUOut | PC←PC[28-3<br>1]<br>  <br>(IR[0-25]<<2) |

| Mem. Access or R-type completion                 | Reg(IR[11-1<br>5]) ←<br>ALUOut                                                    | MDR←M[ALUout]<br>or M[ALUOut]←B         |                                 |                                         |

| Memory read completion                           |                                                                                   | Reg(IR[16-20]) ←<br>MDR                 |                                 |                                         |

#### ILP: Instruction Level Parallelism

- Single-cycle and multi-cycle datapaths execute one instruction at a time.

- How can we get better performance?

- Answer: Execute multiple instruction at a time:

- Pipelining Enhance a multi-cycle datapath to fetch one instruction every cycle.

- Parallelism Fetch multiple instructions every cycle.

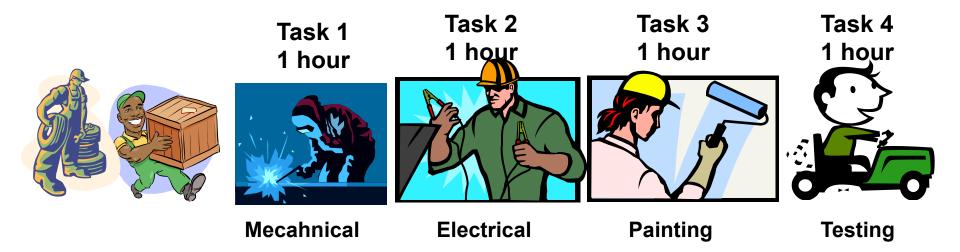

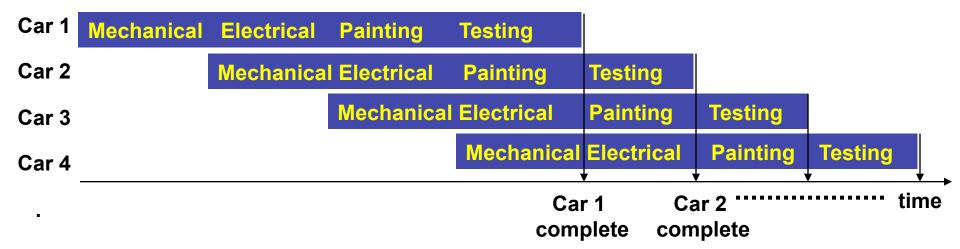

#### **Automobile Team Assembly**

1 car assembled every four hours6 cars per day180 cars per month2,040 cars per year

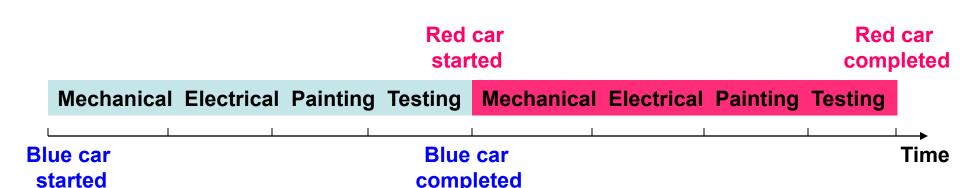

#### **Automobile Assembly Line**

First car assembled in 4 hours (pipeline latency) thereafter 1 car per hour 21 cars on first day, thereafter 24 cars per day 717 cars per month 8,637 cars per year

#### Throughput: Team Assembly

Time of assembling one car = n hours

where *n* is the number of nearly equal subtasks, each requiring 1 unit of time

Throughput = 1/n cars per unit time

#### Throughput: Assembly Line

Time to complete first car = n time units (latency)

Cars completed in time T = T - n + 1

Throughput = 1-(n-1)/T car per unit time

Throughput (assembly line) =

$$\frac{1 - (n-1)/T}{T} = \frac{n(n-1)}{T} \rightarrow n$$

Throughput (team assembly) =  $\frac{1}{1/n} = \frac{n(n-1)}{T} \rightarrow n$

#### Some Features of Assembly Line

Task 1 1 hour

Task 2 1 hour

Task 4 1 hour

Mechanical

**Electrical**

**Painting**

**Testing**

Stall assembly line to fix the cause of defect

3 cars in the assembly line are suspects, to be removed (flush pipeline)

**Defect** found

#### Pipelining in a Computer

- ➤ Divide datapath into nearly equal tasks, to be performed serially and requiring non-overlapping resources.

- Insert registers at task boundaries in the datapath; registers pass the output data from one task as input data to the next task.

- > Synchronize tasks with a clock having a cycle time that just exceeds the time required by the longest task.

- Break each instruction down into a fixed number of tasks so that instructions can be executed in a staggered fashion.

## Thank You