# Computer Architecture An Introduction

## Virendra Singh

**Associate Professor**

Computer Architecture and Dependable Systems Lab

Department of Electrical Engineering

Indian Institute of Technology Bombay

http://www.ee.iitb.ac.in/~viren/

E-mail: viren@ee.iitb.ac.in

CS-683: Advanced Computer Architecture

Lecture 4 (07 Aug 2013)

#### Overview of MIPS

- ❖ Simple instructions, all 32 bits wide

- Very structured, no unnecessary baggage

- Only three instruction formats

| R | ор | rs1 | rs2            | rd                  | shmt | funct |  |

|---|----|-----|----------------|---------------------|------|-------|--|

| 1 | ор | rs1 | rd             | 16 bit address/Data |      |       |  |

| J | ор |     | 26 bit address |                     |      |       |  |

Rely on compiler to achieve performance

**CADSL**

## Example processor MIPS subset

#### MIPS Instruction – Subset

- Arithmetic and Logical Instructions

- > add, sub, or, and, slt

- Memory reference Instructions

- > lw, sw

- Branch

- beq, j

#### **Processor Architecture**

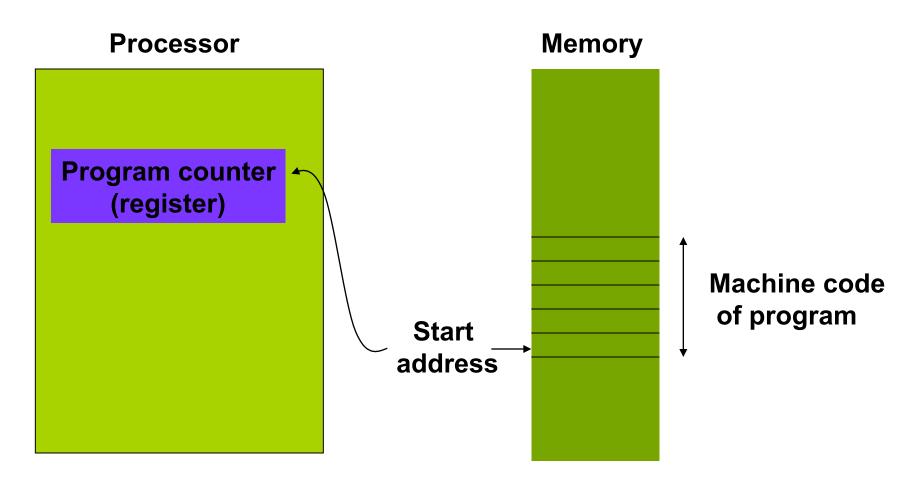

## Where Does It All Begin?

- In a register called program counter (PC).

- PC contains the memory address of the next instruction to be executed.

- In the beginning, PC contains the address of the memory location where the program begins.

## Where is the Program?

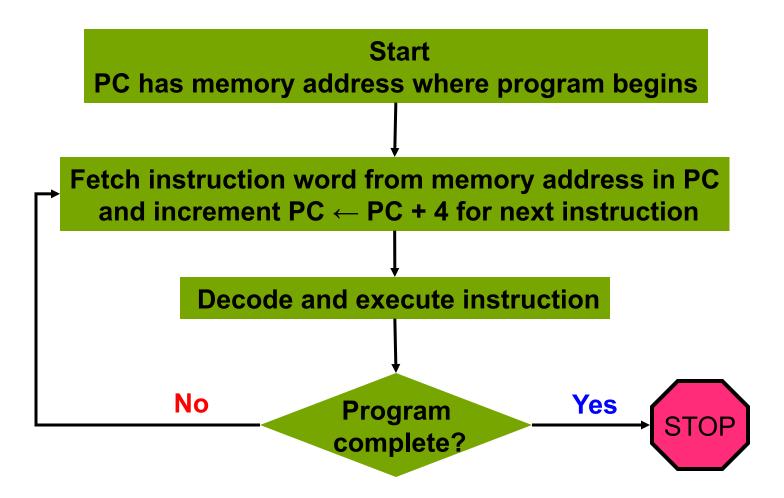

#### How Does It Run?

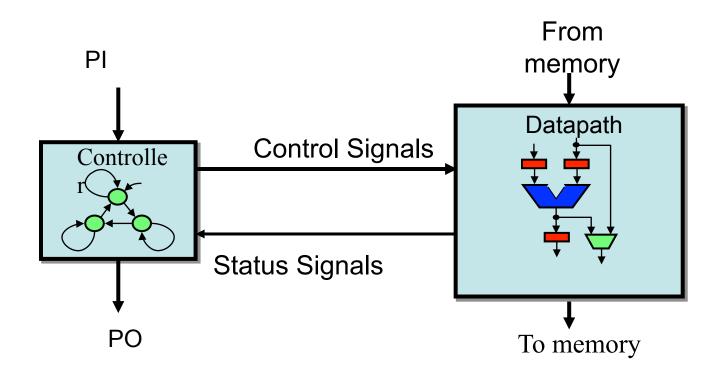

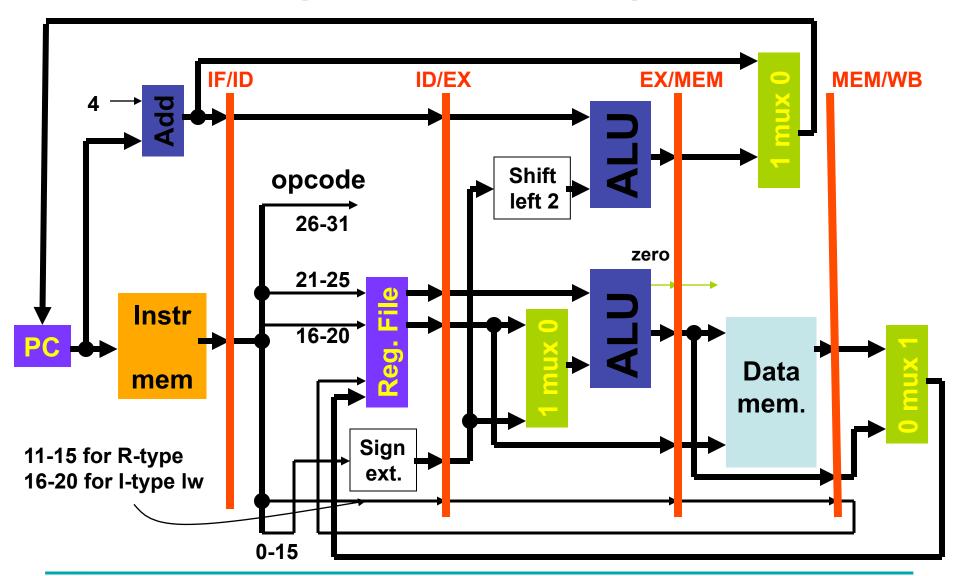

## **Datapath and Control**

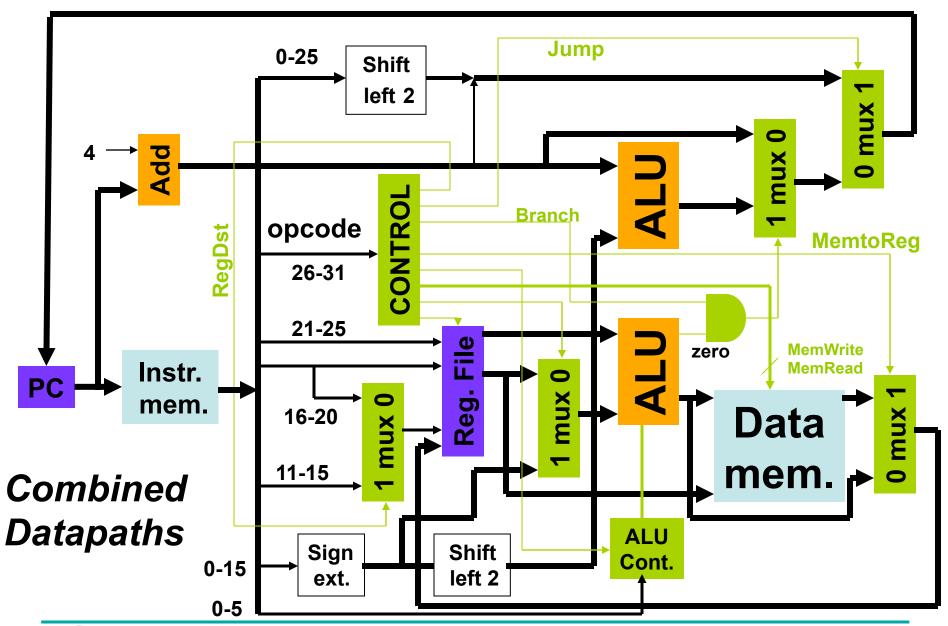

- ➤ Datapath: Memory, registers, adders, ALU, and communication buses. Each step (fetch, decode, execute) requires communication (data transfer) paths between memory, registers and ALU.

- Control: Datapath for each step is set up by control signals that set up dataflow directions on communication buses and select ALU and memory functions. Control signals are generated by a control unit consisting of one or more finite-state machines.

## How Long Does It Take?

- Assume control logic is fast and does not affect the critical timing. Major time delay components are ALU, memory read/write, and register read/write.

- Arithmetic-type (R-type)

Fetch (memory read)2ns

Register read1ns

ALU operation2ns

Register write1ns

• Total 6ns

10

## Time for Iw and sw (I-Types)

• ALU (R-type) 6ns

Load word (I-type)

Fetch (memory read)2ns

Register read1ns

ALU operation2ns

Get data (mem. Read)2ns

Register write1ns

Total8ns

Store word (no register write) 7ns

## Time for beq (I-Type)

ALU (R-type)6ns

Load word (I-type)8ns

Store word (I-type)7ns

Branch on equal (I-type)

Fetch (memory read)2ns

Register read1ns

ALU operation2ns

Total

## Time for Jump (J-Type)

• ALU (R-type) 6ns

Load word (I-type)8ns

Store word (I-type)7ns

Branch on equal (I-type)

Jump (J-type)

Fetch (memory read)2ns

Total

13

#### How Fast Can the Clock Be?

- If every instruction is executed in one clock cycle, then:

- Clock period must be at least 8ns to perform the longest instruction, i.e., lw.

- This is a single cycle machine.

- It is slower because many instructions take less than 8ns but are still allowed that much time.

- Method of speeding up: Use multicycle datapath.

## Multicycle Instruction Execution

| Step                                             | R-type<br>(4 cycles)                                                              | Mem. Ref.<br>(4 or 5 cycles)      | Branch type<br>(3 cycles)       | e J-type<br>(3 cycles)                  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------|---------------------------------|-----------------------------------------|--|--|

| Instruction fetch                                | IR ← Memory[PC]; PC ← PC+4                                                        |                                   |                                 |                                         |  |  |

| Instr. decode/<br>Reg. fetch                     | A ← Reg(IR[21-25]); B ← Reg(IR[16-20])  ALUOut ← PC + (sign extend IR[0-15]) << 2 |                                   |                                 |                                         |  |  |

| Execution, addr. Comp., branch & jump completion | ALUOut ←<br>A op B                                                                | ALUOut ← A+sign extend (IR[0-15]) | If (A= =B)<br>then<br>PC←ALUOut | PC←PC[28-3<br>1]<br>  <br>(IR[0-25]<<2) |  |  |

| Mem. Access or R-type completion                 | Reg(IR[11-1<br>5]) ←<br>ALUOut                                                    | MDR←M[ALUout]<br>or M[ALUOut]←B   |                                 |                                         |  |  |

| Memory read completion                           |                                                                                   | Reg(IR[16-20]) ← MDR              |                                 |                                         |  |  |

## CPI of a Computer

$$\frac{\sum_{k} (Instructions \ of \ type \ k) \times CPI_{k}}{\sum_{k} (instructions \ of \ type \ k)}$$

where

$CPI_k$  = Cycles for instruction of type k

Note: CPI is dependent on the instruction mix of the program being run. Standard benchmark programs are used for specifying the performance of CPUs.

16

## Example

Consider a program containing:

• loads 25%

• stores 10%

• branches 11%

• jumps 2%

• Arithmetic 52%

• CPI =  $0.25 \times 5 + 0.10 \times 4 + 0.11 \times 3 + 0.02 \times 3 + 0.52 \times 4$

= 4.12 for multicycle datapath

CPI = 1.00 for single-cycle datapath

## Multicycle vs. Single-Cycle

Performance ratio = Single cycle time / Multicycle time

$$= \frac{(CPI \times cycle time) \text{ for single-cycle}}{(CPI \times cycle time) \text{ for multicycle}}$$

$$= \frac{1.00 \times 8ns}{4.12 \times 2ns} = 0.97$$

Single cycle is faster in this case, but remember, performance ratio depends on the instruction mix.

### **Traffic Flow**

## Single Lane Traffic

20

#### ILP: Instruction Level Parallelism

- Single-cycle and multi-cycle datapaths execute one instruction at a time.

- How can we get better performance?

- Answer: Execute multiple instruction at a time:

- Pipelining Enhance a multi-cycle datapath to fetch one instruction every cycle.

- Parallelism Fetch multiple instructions every cycle.

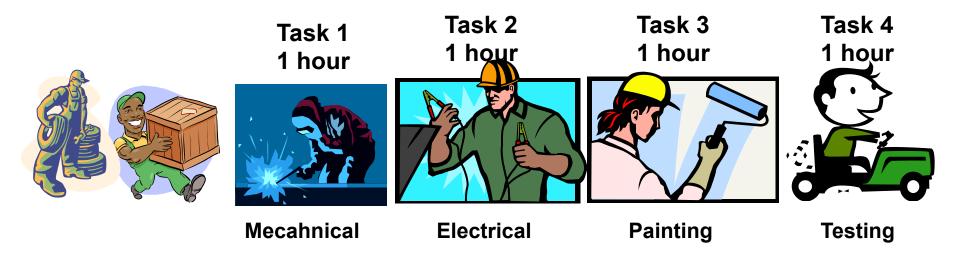

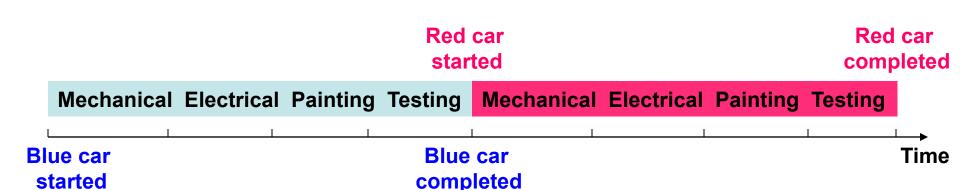

## **Automobile Team Assembly**

1 car assembled every four hours6 cars per day180 cars per month2,040 cars per year

22

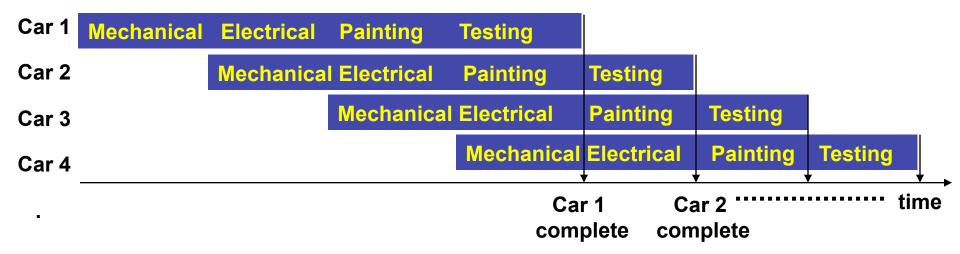

## **Automobile Assembly Line**

First car assembled in 4 hours (pipeline latency) thereafter 1 car per hour 21 cars on first day, thereafter 24 cars per day 717 cars per month 8,637 cars per year

## Throughput: Team Assembly

Time of assembling one car = n hours

where *n* is the number of nearly equal subtasks, each requiring 1 unit of time

Throughput = 1/n cars per unit time

## Throughput: Assembly Line

Time to complete first car = n time units (latency)

Cars completed in time T = T - n + 1

Throughput = 1-(n-1)/T car per unit time

Throughput (assembly line) =

$$\frac{1 - (n-1)/T}{T} = \frac{n(n-1)}{T} \rightarrow \frac{n}{T}$$

as  $T \rightarrow \infty$

## Some Features of Assembly Line

Task 1 1 hour

Task 2 1 hour

Task 4 1 hour

Mechanical

**Electrical**

**Painting**

**Testing**

Stall assembly line to fix the cause of defect

3 cars in the assembly line are suspects, to be removed (flush pipeline)

**Defect** found

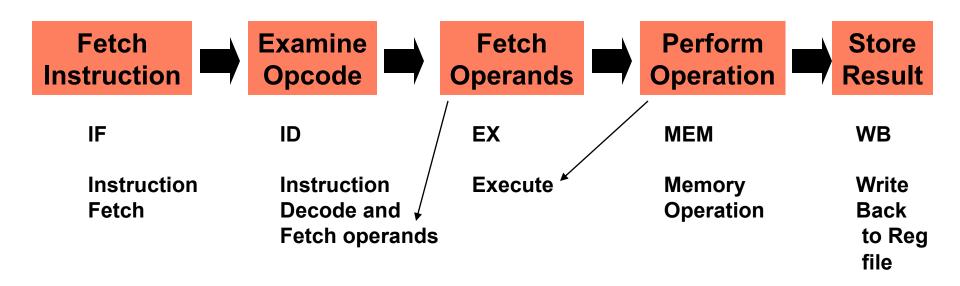

## Pipelining in a Computer

- ➤ Divide datapath into nearly equal tasks, to be performed serially and requiring non-overlapping resources.

- Insert registers at task boundaries in the datapath; registers pass the output data from one task as input data to the next task.

- > Synchronize tasks with a clock having a cycle time that just exceeds the time required by the longest task.

- ➤ Break each instruction down into a fixed number of tasks so that instructions can be executed in a staggered fashion.

## Single-Cycle Datapath

| Instruction class               | Instr.<br>fetch<br>(IF) | Instr. Decode (also reg. file read) (ID) | Execution<br>(ALU<br>Operation)<br>(EX) | Data access (MEM) | Write Back (Reg. file write) (WB) | Total time |

|---------------------------------|-------------------------|------------------------------------------|-----------------------------------------|-------------------|-----------------------------------|------------|

| lw                              | 2ns                     | 1ns                                      | 2ns                                     | 2ns               | 1ns                               | 8ns        |

| SW                              | 2ns                     | 1ns                                      | 2ns                                     | 2ns               |                                   | 8ns        |

| R-format add, sub, and, or, slt | 2ns                     | 1ns                                      | 2ns                                     |                   | 1ns                               | 8ns        |

| B-format, beq                   | 2ns                     | 1ns                                      | 2ns                                     |                   |                                   | 8ns        |

No operation on data; idle time equalizes instruction length to a fixed clock period.

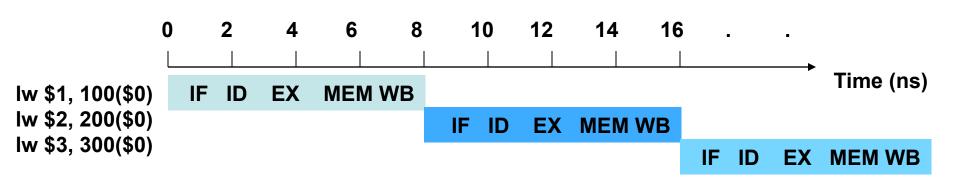

## **Execution Time: Single-Cycle**

Clock cycle time = 8 ns

Total time for executing three lw instructions = 24 ns

## Pipelined Datapath

| Instruction class                   | Instr.<br>fetch<br>(IF) | Instr. Decode (also reg. file read) (ID) | Execution (ALU Operation) (EX) | Data access (MEM) | Write<br>Back<br>(Reg.<br>file<br>write)<br>(WB) | Total<br>time |

|-------------------------------------|-------------------------|------------------------------------------|--------------------------------|-------------------|--------------------------------------------------|---------------|

| lw                                  | 2ns                     | 1ris<br>2ns                              | 2ns                            | 2ns               | 1ris<br>2ns                                      | 10ns          |

| SW                                  | 2ns                     | 1ris<br>2ns                              | 2ns                            | 2ns               | 1ris<br>2ns                                      | 10ns          |

| R-format: add,<br>sub, and, or, slt | 2ns                     | 1ns<br>2ns                               | 2ns                            | 2ns               | 1ns<br>2ns                                       | 10ns          |

| B-format:<br>beq                    | 2ns                     | 1ns<br>2ns                               | 2ns                            | 2ns               | 1ns<br>2ns                                       | 10ns          |

No operation on data; idle time inserted to equalize instruction lengths.

CADSL

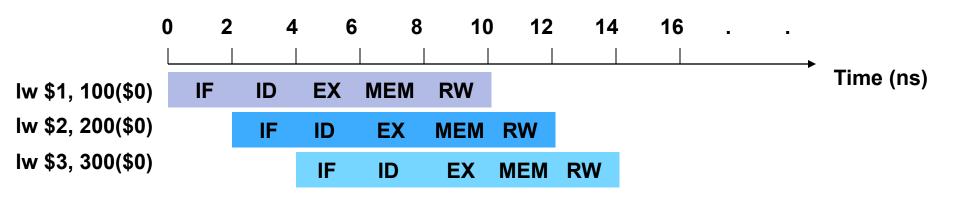

## **Execution Time: Pipeline**

Clock cycle time = 2 ns, four times faster than single-cycle clock

Total time for executing three lw instructions = 14 ns

Performance ratio =

$$\frac{\text{Single-cycle time}}{\text{Pipeline time}}$$

=  $\frac{24}{-----}$  = 1.7

## Pipeline Performance

Clock cycle time = 2 ns

1,003 lw instructions:

Single-cycle time 8,024

Performance ratio =

$$\frac{\text{Single-cycle time}}{\text{Pipeline time}}$$

=  $\frac{\text{Single-cycle time}}{\text{Single-cycle time}}$  =  $\frac{\text$

10,003 lw instructions:

Performance ratio =  $80,024 / 20,014 = 3.998 \rightarrow Clock cycle ratio (4)$

Pipeline performance approaches clock-cycle ratio for long programs.

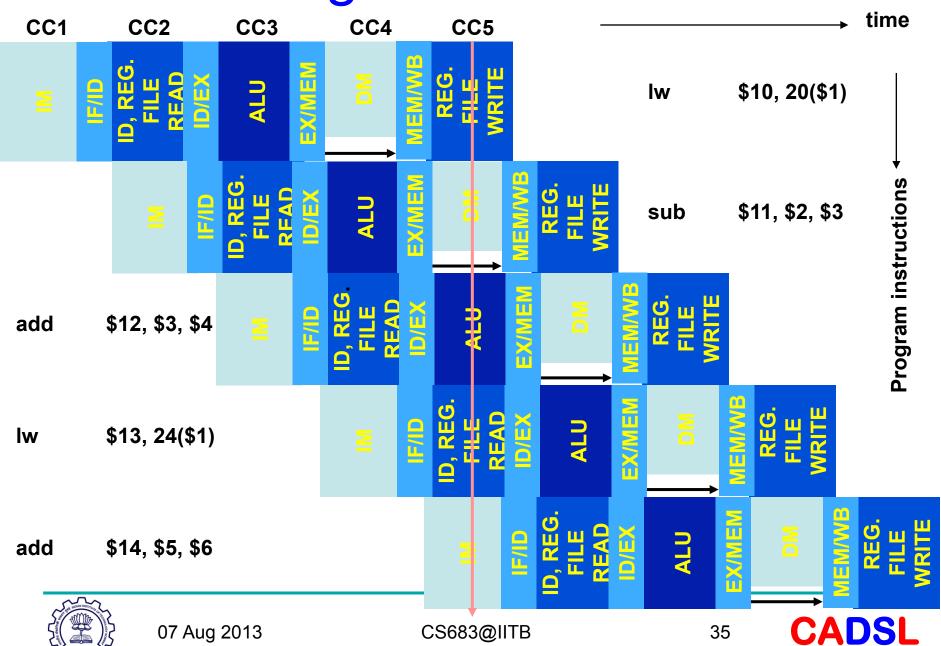

## Pipelining of RISC Instructions

Although an instruction takes five clock cycles, one instruction is completed every cycle.

## Pipelined Datapath

## **Program Execution**

## Advantages of Pipeline

- After the fifth cycle (CC5), one instruction is completed each cycle; CPI ≈ 1, neglecting the initial pipeline latency of 5 cycles.

- Pipeline latency is defined as the number of stages in the pipeline, or

- The number of clock cycles after which the first instruction is completed.

- The clock cycle time is about four times shorter than that of single-cycle datapath and about the same as that of multicycle datapath.

- For multicycle datapath, CPI = 3. ....

- So, pipelined execution is faster, but . . .

Science is always wrong. It never solves a problem without creating ten more.

**George Bernard Shaw**

07 Aug 2013

#### Pipeline Hazards

- Definition: Hazard in a pipeline is a situation in which the next instruction cannot complete execution one clock cycle after completion of the present instruction.

- Three types of hazards:

- Structural hazard (resource conflict)

- Data hazard

- Control hazard

## Thank You

07 Aug 2013

39