EE-389 Electronic Design Lab-II Project Report, EE Dept, IIT Bombay, submitted on 02-12-2005.

# SOUND ACTIVATED SWITCH

Group No. D15 Mamidipally Chandrasekhar (96D07008) <chandrasekhar@iitb.ac.in>

Supervisor: Prof. P.C. Pandey Course Instructors: Prof. P.C. Pandey & Prof. L.R. Subramanian

**Abstract**—Sound activated switch is designed to provide a mechanism by which one can turn on/off an electrical appliance remotely by sound (preferably a clap). Clapping twice would toggle between on and off. Audio signal received via microphone is amplified and compared with a specified threshold voltage to detect occurrence of sound event. The designed circuit presently compares the voltage level received from microphone; hence any spurious sound which exceeds the threshold will be able to turn on/off the switch. Future work will include time domain characteristics i.e., time duration of audio signal due to clap received as well.

## 1. Introduction

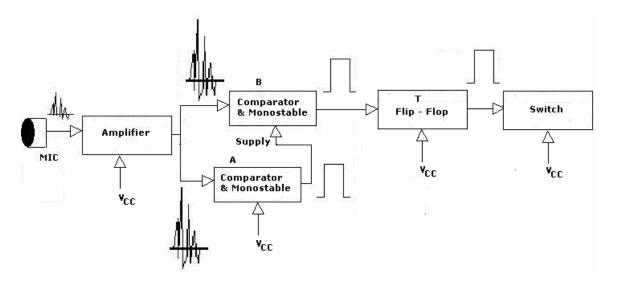

Clapping generates sound waves. A transducer which converts these sound waves into electrical signal is desired to detect the occurrence of sound event. Hence a microphone is used to sense audio signal whose output voltage level typically is of the order of few millivolts depending upon the loudness of sound and distance of source from the microphone. The block diagram of the circuit designed for the project is shown in Figure 1.

Figure 1. Block diagram

It consists of a transistor amplifier, a transistor switch and two types of digital circuits: a monostable and a flip-flop. Since the output voltage range is order of millivolts suitable amplification is needed to compare against a threshold voltage of monostable. Briefly the block diagram can be realized as follows:

### Condenser microphone

Transducer converts the sound waves to electrical signal.

### **Transistor Amplifier**

Amplifies the electrical signal obtained from microphone. Transistor is configured as common emitter amplifier.

### Monostable A

Monostable multivibrator once triggered will switch its output logic level. Output of amplifier stage is fed to monostable held at a threshold voltage. Due to first clap, when the negative swing of output of amplifier stage goes below the threshold voltage of monostable, acts like a trigger, will switch its output logic level to high. A pulse of pre-determined duration time is generated across the output of monostable which acts as supply voltage for monostable B.

#### Monostable B

Difference here being is the output of monostable A acts as supply voltage. Hence due to second clap, when the negative swing of output of amplifier stage goes below the threshold voltage of monostable, acts like a trigger, will switch its output logic level. A pulse of pre-determined duration time is generated across its output.

### Flip-Flop

A flip-flop or a bi-stable multivibrator is a circuit whose output logic level changes when a pulse is applied to the input. The pulse generated by monostable B is fed as input to the flip-flop. For each pulse input its output state changes high or low. This output of flip-flop is connected to a transistor configured as switch.

#### Switch

A transistor is configured as switch here. When the input is high turns on and when input low turns off.

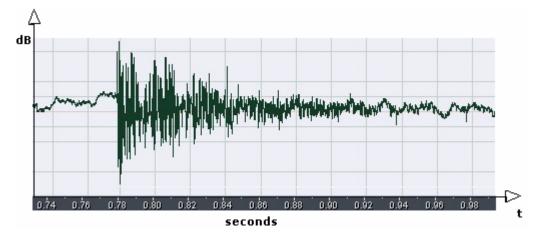

Clap waveform, the time duration of various claps observed is found to be about 0.1 seconds to 0.2 seconds as shown in Figure 2. A microphone was connected to soundcard of computer and waveform was recorded.

Figure 2. Clap waveform

Further the report is organized as follows: section 2 describes bias conditions, amplifier gain and operation of circuit, distance range and sound level is discussed in section 3, conclusions and future work are mentioned in section 4. Monostable multivibrator configuration is illustrated in Appendix A.

## 2. Operation of Circuit

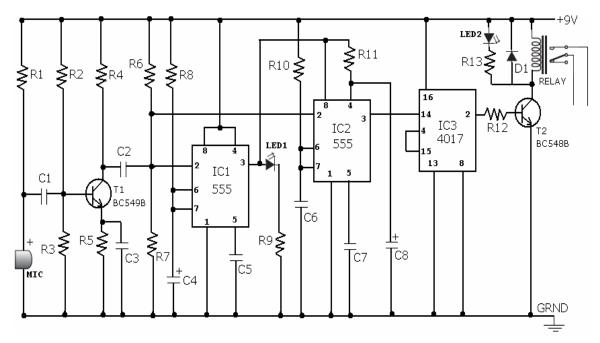

A waveform is generated upon clap; MIC senses this waveform and couples it to the base of the transistor amplifier T1 by capacitor C1 as shown in Figure 3. T1 is configured as common emitter amplifier (CE), by-pass capacitor C3 provides AC-ground. Capacitor C2 couples the amplified waveform to the input of IC1 and IC2 respectively.

Figure 3. Schematic diagram

| Resistors   | Value (ohms)         | Semiconductors Value       |                |  |

|-------------|----------------------|----------------------------|----------------|--|

| R9, R13, R5 | 1 k                  | T1 (Transistor) BC 549B    |                |  |

| R11, R12    | 10 k                 | T2 (Transistor)            | BC 548B        |  |

| R1, R4      | 22 k                 | IC1, IC2                   | NE555P         |  |

| R6, R7, R10 | 100 k                | IC3                        | 4017           |  |

| R8, R3      | 270 k                | D1 (Diode)                 | 1N4148         |  |

| R2          | 2.2 M                | LED1, LED2                 | LED RED, GREEN |  |

| Capacitors  | Value (farads)       | Miscellaneous              |                |  |

| C1, C2, C3  | 0.1 u (Discap)       | MIC (condenser microphone) |                |  |

| C5, C7      | 0.01 u (Discap)      | RELAY 9V, 150 ohm          |                |  |

| C8          | 2.2 u (Electrolytic) | Battery 9V                 |                |  |

| C4, C6      | 10 u (Electrolytic)  |                            |                |  |

#### Amplifier Stage

Experiments were conducted using two bias arrangements: (a) CE amplifier with feedback emitter resistance  $R_E$ , (b) CE amplifier with  $R_B$  feedback resistance.

### CE Amplifier with R<sub>E</sub> feedback resistance

#### **Biasing and operating point**

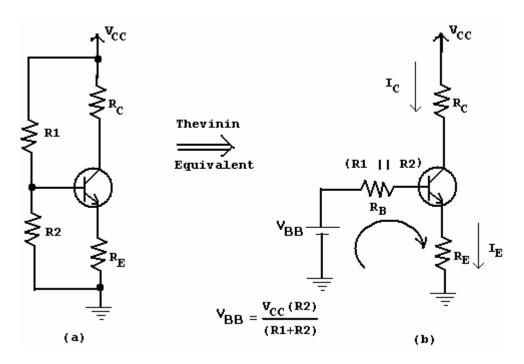

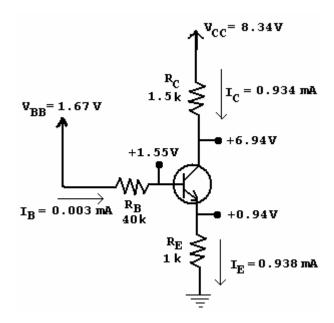

The Bias arrangement of transistor amplifier T1 used for designing the CE amplifier is shown in Figure 4.

Amplifier A.  $V_{BB}$  about 1/5  $V_{CC}$ ,  $V_{CB}$  about 3/5  $V_{CC}$  and  $I_CR_C$  about 1/5  $V_{CC}$  was chosen based on similar kind of bias conditions mentioned in book by Sedra & Smith [1].  $V_{CB}$  kept large to allow reasonable negative swing.

Figure 4. Bias arrangement

The KVL equations for bias arrangement mentioned in Figure 4 are described as follows:

| $V_{CC}$ = 9 V, $V_{BE}$ = 0.7 V           |     |

|--------------------------------------------|-----|

| $V_{BB} = V_{CC} x (R2) / (R1+R2)$         | (1) |

| $V_{BB} - V_{BE} = I_E R_E + I_B R_B$      | (2) |

| Hence, $1/5V_{CC} = 0.7 + I_BR_B + I_ER_E$ |     |

To make  $I_{E}$  insensitive to temperature and  $\beta$  variation (i.e., a should vary less for  $I_{C}$   $\approx$   $I_{E}$ ) following constraints were considered:

$$V_{BB} \gg V_{BE}$$

(3)

$R_{E} \gg R_{B} / (\beta + 1)$  (4)

The BC549 datasheet [2] specifies minimum gain of 200. Hence R1, R2 as 200 k, 50 k respectively provide a voltage divider of 1/5  $V_{CC}$  and as well (R1||R2) <  $\beta$  that meets the equations 3 and 4. For the design bias current  $I_C = 1$  mA was chosen. Circuit parameters can be calculated as follows:

$$\begin{split} I_B &= I_C / ~(\beta + 1) = 4.975 ~\text{uA} \\ R_E &= (1/5 ~V_{CC} - 0.7 - I_B R_B) ~/~ I_E = 0.9 ~\text{k} \\ R_E &\approx 1 ~\text{k} \\ I_C R_C &= 1/5 ~V_{CC}, ~\text{gives} ~R_C = 1.8 ~\text{k} \\ R_C &\approx 1.5 ~\text{k} \end{split}$$

Hence putting  $R_E = 1$  k,  $R_C = 1.5$  k, R1 = 200 k, R2 = 50 k following node voltages and current results:

$V_{BB} = 1.8 V$ ,  $V_{E} = 1.1 V$ ,  $V_{CB} = 5.7 V$ ,  $V_{CE} = 6.4 V$ .

$I_E = 1 \text{ mA}, I_B = 4.975 \text{ uA}, I_C = 0.995 \text{ mA}.$

Actual values measured using multi-meter for the bias arrangement using 8.34 V supply voltage (battery) is shown in Figure 5.

Figure 5. Node voltages and currents

$I_B = 3 \text{ uA}, I_C = 0.934 \text{ mA}, I_E = 0.938 \text{ mA}, V_{BE} = 0.60 \text{ V}$

Operating bias point  $I_{CO}$  = 0.93 mA  $\approx$  1 mA,  $V_{CO}$  = 6.94 V  $\approx$  7 V.

Amplifier B. Similar calculations like earlier were tried for BC550B with  $I_c = 300 \text{ uA}$ ,  $V_{BB} = 1/10 V_{CC}$ ,  $V_{CC} = 9 \text{ V}$ ,  $V_{BE} = 0.7 \text{ V}$ ,  $V_E = 0.3 \text{ V}$ , R1 = 2.2 M, R2 = 270 k as initial conditions resulted in  $R_c = 22 \text{ k}$  and  $R_E = 1 \text{ k}$ . The circuit node voltages and currents for  $V_{CC} = 9 \text{ V}$  are as follows:

$$V_{B} = 0.826 \text{ V}, V_{E} = 0.262 \text{ V}, V_{BE} = 0.564 \text{ V}, V_{C} = 3.302 \text{ V}$$

$$I_{C} = 0.259 \text{ mA}.$$

Operating bias point,  $I_{CQ} = 0.26$  mA and  $V_{CQ} = 3.3$  V. For changing  $R_C$ , bias current was almost the same and for 10 mV AC signal, gain was found approximately equal to ratio of  $R_C/R_E$  as shown in Table B.  $V_{CC} = 9$  V,  $R_E = 1$  k, R1 = 2.2 M, R2 = 270 k.

| <b>R</b> <sub>c</sub> (k) | V <sub>B</sub> (V) | V <sub>E</sub> (V) | V <sub>c</sub> (V) | I <sub>c</sub> (mA) | Gain |

|---------------------------|--------------------|--------------------|--------------------|---------------------|------|

| 1                         | 0.829              | 0.268              | 8.783              | 0.240               | 1    |

| 2.2                       | 0.828              | 0.268              | 8.464              | 0.243               | 2    |

| 3.3                       | 0.828              | 0.268              | 8.179              | 0.248               | 3    |

| 4.7                       | 0.828              | 0.268              | 7.807              | 0.253               | 4    |

| 10                        | 0.826              | 0.266              | 6.440              | 0.256               | 9    |

| 22                        | 0.826              | 0.262              | 3.302              | 0.259               | 20   |

Table B. Bias operating point with changing  $R_C$

#### AC gain

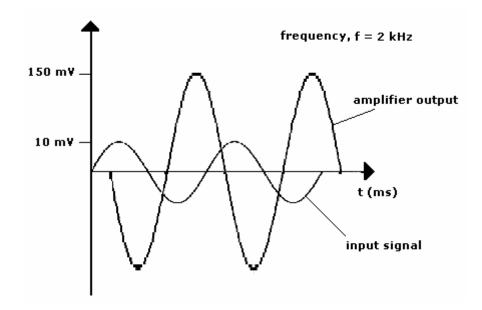

For the AC gain, microphone was replaced by a function generator. A sinusoid signal of 10 mV to 100 mV of frequency 2 kHz was fed with increments of 10 mV across base of amplifier B is shown in Table C.

When no clap was made microphone output voltage level was approximately 5-8 mV. This is a brand new microphone, was found to be very sensitive.

AC output for amplifier B. The gain mentioned is in presence of load i.e., the R6 (100 k) and R7 (100 k) connected between output of amplifier and pin2 of IC2, IC3 respectively. The voltage across R7 was found to be 4.58 V.

| Input<br>mV(p–p) | Output<br>mV(p-p) |

|------------------|-------------------|

| 20               | 350               |

| 40               | 690               |

| 60               | 1040              |

| 80               | 1360              |

| 120              | 2080              |

| 140              | 2380              |

| 160              | 2720              |

| 180              | 3060              |

Table C. Input and Output voltages of amplifier B

At 90 mV LED1 and LED2 glowed since divider was at approximately 4.58 V, and threshold voltage of IC2, IC3 can be calculated as  $1/3^{rd}$  V<sub>CC</sub> that is 3 V. Gain is approximately -17 V/V or 25 dB.

Theoretical gain can be calculated as,  $A_V = -g_m \times (R_4 \parallel R6 \parallel R7)$  since  $C_3$  connected across  $R_5$  acts as by-pass capacitor (assuming capacitors act as short circuit).  $g_m = I_C / V_T = 1.8 \text{ mA/V}$ .  $A_V = -27.5 \text{ V/V}$  or 28.7 dB.

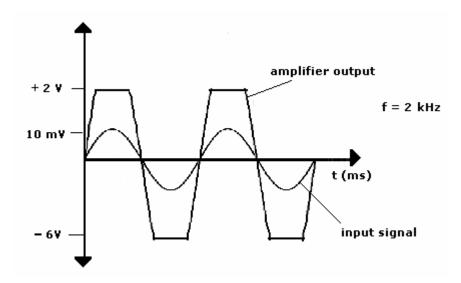

Amplifier output seen with oscilloscope is shown in Figure 6.

Figure 6. Input and Output waveform of amplifier B

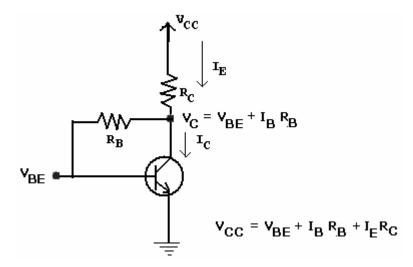

CE amplifier with R<sub>B</sub> as feedback

Figure 7. Bias arrangement

#### **Biasing and Operating point**

Amplifier C. Initial conditions for biasing were chosen as  $I_E = 300 \text{ uA}$ ,  $V_C = 3 \text{ V}$ ,  $R_B = 2.2 \text{ M}$ ,  $V_{BE} = 0.7 \text{ V}$  for  $V_{CC} = 9 \text{ V}$ . Solving the KVL equation shown in Figure 7 gives  $R_C = 20.3 \text{ K}$ . Approximately  $R_C = 22 \text{ K}$  was used and correspondingly  $I_E = 250 \text{ uA}$ ,  $V_C = 3.4 \text{ V}$ ,  $V_{BE} = 0.59 \text{ V}$  was observed. Transistor BC 548B was used here.

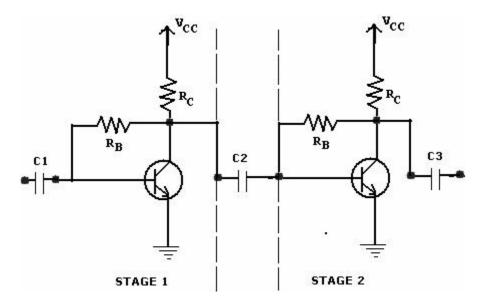

Using this bias arrangement CE – CE cascade was made to form 2-stage amplifier as shown in Figure 8. The node voltages for 1<sup>st</sup> stage were found to be  $V_C = 3.20$  V,  $V_{BE} = 0.58$  V and for 2<sup>nd</sup> stage  $V_C = 3.74$  V,  $V_{BE} = 0.55$  V with  $R_C = 22$  K and  $R_B = 2.2$  M for 9 V supply.

Figure 8. Sectional view of 2-stage amplifier C

## AC gain

Microphone issued from lab had output voltage level, when no clap, to be of 2-3 mV peak.

With R6 (100 K) and R7 (220K), pin2 of IC1, and IC2 were held at voltage level 6.1 V. A sinusoid signal of 1 mV - 10 mV at 2 kHz was fed at base of  $1^{st}$  stage, LED1 glowed at approximately 3 mV. Approximate gain was found to be 1100. Output waveform of amplifier C is shown in Figure 9.

Figure 9. Input and Output waveform of amplifier C

#### Monostable

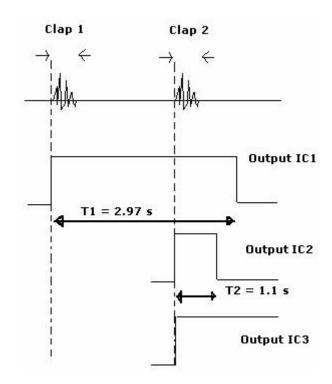

Monostable multi-vibrator or one-shot configuration of 555 timer (IC1) was chosen to identify the voltage drop across transistor amplifier. For complete details on operation and configuration of 555 timer as monostable multivibrator refer to Appendix A. Initially pin 2 of IC2 is kept high at  $1/2 V_{CC}$  and  $V_{TL}$  being  $1/3 V_{CC}$ , so that the amplified output due to clap if exceeds  $1/2 V_{CC} - 1/3 V_{CC}$  shall switch the output pin 3 logic to high. Thus the LED1 connected via series resistance R9 to pin 3 glows. The time interval T1 during which LED1 glows is pre-determined by external resistor and capacitor R8, C4. The time period  $T1 = 1.1 \times R8 \times C4 = 2.97$  seconds. Hence the output high of IC1 makes IC2 ready to receive the triggering signal due to second clap since output of IC1 is acting as  $V_{CC}$  for IC2.

IC2 is configured as mono-stable multi-vibrator similar to IC1, but the V<sub>CC</sub> supply for IC2 is the output (pin 3) of IC1. This is to observe second clap that has to occur within 2.97 s from the instant the first clap was made. Resistor R11 and capacitor C8 connected to pin 4 of IC2 prevent false triggering when IC1 provides the supply voltage to IC2 at first clap. But the R11 and C8 time constant fails depending upon the loudness of clap i.e., more than one amplified peak crosses the threshold level. The time interval T2 of IC2 for which its output remains high can be calculated as  $T2 = 1.1 \times R10 \times C6 = 1.1$  seconds. This acts like a pulse input to stage 4, IC3 (4017). The switching interval when two claps are made is shown in Figure 10.

Figure 10: Switching times for 2 claps

### Flip-Flop

The output pulse of IC2 acts as clock input for IC3 (4017) since output of IC2 is connected to pin 14 of IC3. Initially output pin 2 of IC3 is low, upon receiving the pulse from IC2 the state of pin 2 of IC3 switches to high. Since pin 4 is connected to pin 15, and pin 13 is enable input connected to ground. Each pulse at pin 14 changes

the state of pin 2 as mentioned in datasheet of 4017 [3]. Thus IC3 is configured as bi-stable whose output pin 2 remains high or low indefinitely with respect to each pulse input at pin 14 of IC3. For 8.34 V as supply voltage the output high voltage at pin 2 of IC3 was found to be 8.05 V.

### Switch

Transistor T2 as switch, when transistor is biased with large base current [1] with small  $R_B$  connected to base the collector to emitter voltage  $V_{CE}$  goes to almost 0 V. When no base current transistor is will be in off i.e. cut-off. The resistor R13 (10 K) sets the current at base of T2 to be 0.73 mA and  $V_{CE}$  observed to be 0.03 V that is almost 0 V when output of IC3 goes high. Diode D1 is connected to prevent any damage due to occurrence of spike when relay de-energizes. As transistor T2 switches on, turning on the relay, the LED2 glows due to second clap. Further clapping twice would make output pin2 of IC3 go low, thus transistor goes into cut-off turning off LED2 and relay.

## 3. Performance

Amplifier design using transistor is subjective to biasing conditions. As mentioned earlier in section 2, the biasing conditions have changed. Mainly performance of circuit can be classified into level of sound, and distance from which clap has to be made.

## Sound

Any sound after amplification has a voltage level of approximately 1.5 V can cause the trigger for the case of amplifier A & B (both 1-stage amplifiers), 4.4 V for amplifier C (2-stage amplifier) and 6V for cascaded B (2-stage amplifier). One can increase the reference voltage at which the pin 2 of IC1, IC2 are held, but still its any sound not *specific sound clap*. Hence to make effective time domain characteristics are now considered in further work. Time duration of clap is approximately 0.1 seconds to 0.2 seconds. Microcontroller has on-chip comparator, timers & counters, thus IC1, IC2 and IC3 can be replaced with microcontroller.

## Sensitivity

The voltage divider resistors  $R_6$  and  $R_7$  values can be adjusted to increase or decrease the voltage level at which pin2 of monostable is held initially. For the cascaded two-stage using amplifier B, a 10 k resistor was used instead of R6 & R7 to keep pin2 of monostable at almost  $V_{CC}$ .

### Distance

Circuit was tested in approximately 5m x 7m room. The environmental sound level for each microphone used in circuits is shown Table D. Environment sound level is the voltage level observed when no clap was made.

| Microphone | Amplifier | Gain | Environment<br>sound level<br>(mV) | Distance from<br>microphone<br>approx. |         |

|------------|-----------|------|------------------------------------|----------------------------------------|---------|

|            |           |      |                                    | Minimum                                | Maximum |

| New        | A         | 6    | 5 - 8                              | < 1m                                   | < 1m    |

| New        | В         | 17   | 5 - 8                              | < 1m                                   | < 1m    |

Table D: Environment sound level and distance.

| New | 2-stage B | 120  | 5 - 8 | 1 m | 5 m |

|-----|-----------|------|-------|-----|-----|

| Old | С         | 1100 | 2     | 2 m | 7 m |

## 4. Conclusions and Future Work

In designing the circuit, the gain has been improved from Amplifier A (gain 6 times) to Amplifier B (gain 17 times). Amplifier C (gain of 1100) and a two-stage cascaded amplifier using amplifier B (gain of 120) were designed to be used with microcontroller. Atmel 89C2051 microcontroller will be used to apply the time domain characteristics of waveform.

## 5. References

- [1] Adel S. Sedra and Kenneth C. Smith, *Microelectronic Circuits*, 5<sup>th</sup> Edition, Oxford University Press, New York, 2004.

- [2] Philips semiconductors: BC549, BC550 NPN general purpose transistors, 2004 Oct 11.

- [3] Philips semiconductors: HEF4017B MSI 5-stage Johnson counter, January 1995.

## **APPENDIX A**

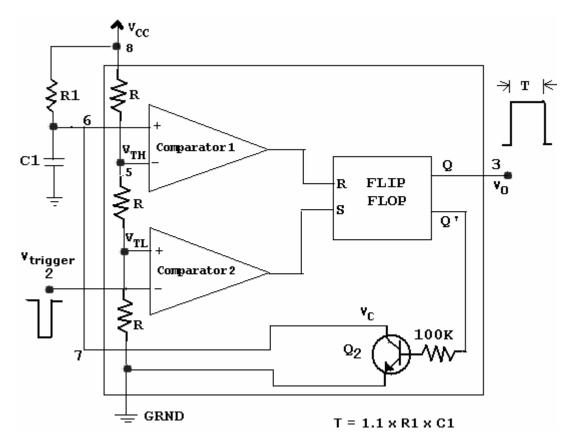

Monostable multivibrator using IC 555 timer with external resistor R1 and C1 is shown in Figure 11.

Figure 11: Monostable mode 555 timer

In the stable state the flip-flop will be in the reset state, and thus its Q' output will be high, turning on the transistor Q1. Transistor Q1 will be saturated, and thus V<sub>C</sub> will be close to 0 V, resulting in a low level at the output of comparator 1. The voltage at the trigger input terminal, labeled V<sub>trigger</sub>, is kept high (greater than V<sub>TL</sub>=1/3V<sub>CC</sub>), thus the output of comparator 2 also will be low. To trigger the monostable multivibrator, a negative pulse is applied to the trigger input terminal. As V<sub>trigger</sub> goes below V<sub>TL</sub>, the output of comparator 2 goes to the high level, thus setting the flip-flop. Output Q of the flip-flop goes high, and thus V<sub>0</sub> goes high, and output Q' goes low, turning off transistor Q1.

Capacitor C1 now begins to charge up through resistor R<sub>1</sub>, and its voltage exponentially rises towards V<sub>CC</sub>. The monostable multivibrator is in quasi-stable state. This state prevails until V<sub>o</sub> reaches and begins to exceed, the threshold of comparator 1, V<sub>TH</sub>, at which time the output of comparator 1 goes high, making Q' high and Q low. Transistor Q1 turns on and acts as short-circuit across capacitor. Hence capacitor discharges. When the flip-flop is reset its Q output goes low, and thus V<sub>o</sub> goes back to 0 V. V<sub>c</sub> can be expressed as, V<sub>c</sub> = V<sub>CC</sub> (1 - e<sup>-t / RC</sup>) i.e., setting V<sub>c</sub> = V<sub>TH</sub> = 2/3 V<sub>CC</sub> gives during which output is high and is found to be T = 1.1 x R1 x C1.