# Elements of System Design **Classification and Organization**

Authored by : Hrishikesh Sharma Date : August 20, 2004

Subramanian P S

Reviewed by : Subramanian P S Date : August 24, 2004

Reviewed by : \_\_\_\_\_ Date : \_\_\_\_

# **Elements of System Design**

© 2004 TATA Consultancy Services

#### **Printing the document**

To print this document optimally, take colour print outs of pages 12, 13, 19, 23, 25, 28, 30, 34, 35 and 42. All other pages can be printed in black and white.

#### Viewing the document

Pages 42 is best read on screen with a magnification of 125% or higher. Other pages can be read at normal zoom.

## Scope

The document reviews the ontological aspects of majority of terms used in systems' design community. It proposes a semantic framework that encapsulates the fundamentals of heterogeneous system design. The document then goes on to describe the elements of system design process from the purview of this framework.

# **Contents**

| DOCUMENT ORGANIZATION9 |                                                            |    |  |  |

|------------------------|------------------------------------------------------------|----|--|--|

| 1                      | INTRODUCTION                                               | 10 |  |  |

| 2                      | SYSTEMS CLASSIFICATION                                     | 12 |  |  |

|                        | 2.1 Transformational Systems                               |    |  |  |

|                        | 2.2 REACTIVE SYSTEMS.                                      |    |  |  |

|                        | 2.3 Interactive Systems                                    |    |  |  |

| 3                      | SYSTEMS MODELLING                                          |    |  |  |

|                        |                                                            |    |  |  |

|                        | 3.1 MOTIVATION FOR MODEL OF COMPUTATION                    |    |  |  |

|                        |                                                            |    |  |  |

|                        | 3.2.1 Power of Computational Models                        |    |  |  |

|                        | 3.3 RELATION TO SYSTEM MODELS                              |    |  |  |

|                        | 3.3.2 Modelling Reactive Systems                           |    |  |  |

|                        | 3.3.3 Modelling Interactive Systems                        |    |  |  |

|                        | 3.4 USING MODEL OF COMPUTATION                             |    |  |  |

|                        | 3.4.1 Enumeration of Behaviour.                            |    |  |  |

|                        | 3.4.2 Providing Specification.                             |    |  |  |

|                        | 3.4.3 Providing Structure                                  |    |  |  |

|                        | 3.4.4 An Example                                           |    |  |  |

|                        | 3.5 LANGUAGES AND MODELS OF COMPUTATION                    |    |  |  |

|                        | 3.5.1 Domain-specific Languages                            |    |  |  |

|                        | 3.6 ORDERING USING EXPRESSIVENESS OF MODELS OF COMPUTATION |    |  |  |

|                        | 3.7 OPERATIONAL SEMANTICS AND MODEL OF COMPUTATION         |    |  |  |

| 4                      | DESIGN USING FORMAL MODELS                                 | 23 |  |  |

| •                      |                                                            |    |  |  |

|                        | 4.1 SIMPLE DESIGN                                          |    |  |  |

|                        | 4.1.1 Cost Functions                                       |    |  |  |

|                        | 4.1.2 Sources of Cost                                      |    |  |  |

|                        | 4.1.3 Choices during Design                                | 2/ |  |  |

|                        |                                                            |    |  |  |

|                        | 4.3 TACKLING HETEROGENEITY                                 |    |  |  |

|                        | 4.3.2 Cost Distribution                                    |    |  |  |

|                        | 4.3.3 Refinements                                          |    |  |  |

|                        | 4.3.4 Category Theoretic Formulation of Problem.           |    |  |  |

|                        | 4.3.5 Terms and Details                                    |    |  |  |

|                        | 4.3.5.1 Design Task                                        |    |  |  |

|                        | 4.3.5.2 Design Methodology                                 |    |  |  |

|                        | 4.3.5.3 Design Process                                     |    |  |  |

|                        | 4.4 ELEMENTS OF METHODOLOGIES                              | 35 |  |  |

|                        | 4.4.1 Models and Specifications                            | 35 |  |  |

|                        | 4.4.2 Design Flow                                          | 36 |  |  |

|                        | 4.4.2.1 Top-down Approach                                  |    |  |  |

|                        | 4.4.2.2 Bottom-up Approach                                 |    |  |  |

|                        | 4.4.2.3 Mix Approach                                       |    |  |  |

|                        | 4.4.3 Architecture Exploration                             |    |  |  |

|                        | 4.4.3.1 Relation to Design Flow                            | 38 |  |  |

#### Elements of System Design

| 4.4     | 4.3.2 Exploration in Top-down Flow     | 39 |

|---------|----------------------------------------|----|

| 4.4     | 4.3.3 Exploration in Bottom-up Flow    | 39 |

| 4.4     | 4.3.4 Exploration in Mix Flow          |    |

| 4.4.4   | •                                      | 40 |

| 4.4.5   | Synthesis                              | 40 |

| 4.4.6   |                                        | 40 |

|         | 1.6.1 Behavioural Refinement           |    |

| 4.4     | 4.6.2 Structural Refinement            |    |

| 4.5 VI  | ERIFICATION OF DESIGN.                 |    |

|         | OMPUTATION MODELS AND INTERCONNECTIONS |    |

|         | RENDS IN EVOLUTION OF METHODOLOGIES    |    |

|         | ARDWARE-SOFTWARE CO-DESIGN             |    |

| 4.8.1   | Evolution                              |    |

| 4.8.2   | Business Aspect                        |    |

| 4.8.3   |                                        |    |

| 4.8.4   | Modelling                              |    |

| 4.8.5   | Partitioning                           | 47 |

| 4.8.6   | Performance Measurement                | 4/ |

|         |                                        |    |

| 4.8.7   | 7 777777778                            |    |

| 4.9 Iss | SUES IN RECONFIGURABLE SYSTEMS' DESIGN | 48 |

| 5 REF   | ERENCES                                | 49 |

|         |                                        |    |

# **List of Figures**

| FIGURE 1: TRANSFORMATIONAL SYSTEMS                          | 12 |

|-------------------------------------------------------------|----|

| FIGURE 2: REACTIVE SYSTEMS                                  |    |

| FIGURE 3: USING MODEL OF COMPUTATION                        |    |

| FIGURE 4: USING MODEL OF COMPUTATION FOR FSA                | 20 |

| FIGURE 5: MAPPINGS WITHIN MODEL OF COMPUTATION              | 23 |

| FIGURE 6: MORE MEANINGFUL STRUCTURE OF MODEL OF COMPUTATION |    |

| FIGURE 7: INFO-ACTIONS AND COMPANIES BUILT UPON THEM        | 26 |

| FIGURE 8: COMPLETE STRUCTURE OF MODEL OF COMPUTATION        | 28 |

| FIGURE 9: AN EXAMPLE REFINEMENT                             | 30 |

| FIGURE 10: GENERAL METHODOLOGY                              |    |

| FIGURE 11: METHODOLOGY FOR REASON V                         | 34 |

| FIGURE 12: METHODOLOGY FOR REASON I AND III                 | 35 |

| FIGURE 13: DIRECTED GRAPH FOR A MODEL OF COMPUTATION        | 42 |

# **List of Tables**

## List of acronyms

ADL Architecture Description Language

ASIC Application-specific Instruction Processor

ASIP Application-specific Integrated Circuit

CAD Computer-aided Design

CDFG Control-data Flow Graph

CFSM Communicating Finite State Machines

CPU Central Processing Unit

CSP Communicating Sequential Processes

DFA Deterministic Finite Automata

DFG Data Flow Graph

DSL Domain-specific Language

DSP Digital Signal Processor(Processing)

FSA Finite State Automata

FSM Finite State Machine

GPL General-purpose Language

IP Intellectual Property

MoC Model of Computation

NFA Non-deterministic Finite Automata

OS Operating System

PCB Printed Circuit Board

RPC Remote Procedure Call

RTL Register-transfer Language

RTOS Real-time Operating System

SOS Structural Operational Semantics

#### Elements of System Design

UI User Interface

UML Unified Modelling Language

(Very High Speed Integrated Circuits) Hardware Description Language VHDL

VLSI Very Large Scale Integration

#### **Document Organization**

The document is organized as follows. A section of introduction brings out in detail, the purpose of our work. It is followed by reviewing an operational classification of systems, which is to be used later. Here, the concept of system modelling is introduced gradually. Elements such as model of computation, its constituents, relationship to languages and themselves, as well as an example operational semantics is introduced. Now, the design process is elaborated using the new systems modelling concept. Factoring for optimization, heterogeneity(the major treatment) and details about design methodologies is introduced. The design elements such as analysis, synthesis, refinement and abstraction are treated in the same section. Finally, the emerging fields of hardware-software Codesign and Reconfigurable Systems' design are explained using the new model.

#### 1 Introduction

Systems have been employed by both nature, and humans, to perform specific functions. There is a sense of **order** in all natural processes, which one can **observe**; even when there exist apparently random, or chance events. This is because of the tendency to fill in our lack of understanding of nature, with explanations that tend to replace noise with meaningful pattern and effects with probable causes. Earth's climatic system, human immune system etc. are examples of natural systems(otherwise known as physical systems), which exhibit a specific pattern of behaviour.

Human race itself has been involved in creation of systems, mainly as aids for the day-to-day work it has to carry. Starting with simple mechanical systems such as a crowbar and the flint(stone)-based spark ignition, the evolution of such systems has come to a point where they can be as complex, as their natural counterpart. Internet is an example of such a communication (network) system. Such systems are also frequently called *Artificial Systems*, mainly to underline the fact that they are man-made.

Structurally, artificial systems are a collection of objects called components, or subsystems. The components can be **heterogeneous** in nature, and their interaction may be regulated by some simple or complex means. Note that it is only (complex) artificial systems, which *require* a structure; for providing a structure(divide-and-conquer) is the human's way of dealing with complexity.

Human-made systems can be classified into many categories; prominent amongst them are electronic systems, power systems and mechanical systems. This document focuses on electronic systems, or (embedded) electronic component of a complex system, such as the *information processing systems*. Any reference to the term, system, has also to be taken as an artificial system. Electronic systems are getting more prevalent, because they demonstrate richness of functionality, superior performance, safety/reliability and low-cost aspects.

Microelectronics domain, especially VLSI, has had the "more specialized/guided/formal" set of design methods so far. The design of microelectronic systems consists of realizing(synthesis) the desired functionality(using circuits etched on a wafer), while satisfying certain design constraints(optimization). Optimization is done to maximize certain system quality(qualities) for competitive advantages. Such optimizations lead to design tradeoffs; some quality is gained on the expense of the other. Computer-aided design methodologies, which have been successfully used in reducing design times and performing optimization for integrated circuit designs, can also be applied/scaled for system design purposes. The terms "design space", "design tradeoff", "design space exploration" etc. have been carried over from the IC design domain into the broader system design domain.

There is been at least one comprehensive work on similar area already[22], and few useful tools and frameworks based on that(PTOLEMY, POLIS) are already being in use now. Though it covers a lot of "what all exists", the authors feel that there is still a scope of debating, "why all the gamut exists", or in other words, ontology. That is the question, which is tried for treatment in this short document.

There have also been papers pointing out the disparity in the various definitions floating about many of the terms used by design community. Also, there have been specific papers, which have tried to formally address semantic definitions of these, in order to bring precision. Our approach is novel in the sense that we propose a generalized semantic framework that encapsulates all the aspects of heterogeneous system design; and hence provides opportunity

to look into all possible design terminologies, with it's aid. Going a step further, we propose a way to use this framework for all system-related design, analysis and verification tasks.

#### 2 Systems Classification

Much of the background established in this section deals with *information-processing systems*. Information processing systems are automatic, electronic machines whose function is to generate a **set** B of output information items(e.g., the results of computation on the data), from some **set** A of input information items(for example, data, and at times, a program representing a computation in some form). The mapping is formally represented by a function  $F: A \rightarrow B$ .

Before we move into describing our modelling framework, it is important to classify the information-processing systems. Different elements of the framework will be used in the corresponding design methods for these systems. A traditional classification provided in [14] is detailed out as follows.

#### 2.1 Transformational Systems

These systems take a body of input data, and transform it into a body of output data. Generation of the correct result is the primary concern of these systems, and hence issues such as program termination gain importance. Initially, the term information-processing systems used to refer to these systems only.

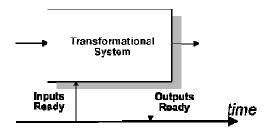

A continuous-time processing view of these systems is that they have all inputs ready when invoked and the outputs are produced after a certain computation period. After the computation, the system halts, till the next set of inputs is provided. Hence, the model of such system is required to specify only the functional/transformational aspect.

Figure 1: Transformational Systems

#### 2.2 Reactive Systems

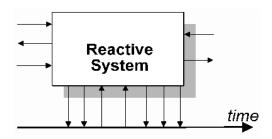

These systems are repeatedly prompted by the environment, and their role is to continuously respond to external inputs, at the speed required by the environment. Such a system never has all its inputs ready--the inputs arrive in endless and perhaps unexpected sequences. Hence, in general, it does not compute or perform a function, but is supposed to maintain a certain ongoing relationship, so to speak, with its environment. Such systems do not lend themselves naturally to descriptions in terms of functions and transformations, making it virtually impossible to write a transformational program for them. However, meta-models such as tagged-signal model[25] exist for reactive systems, for a purpose described in section 3.3.2.

A model of such systems thus requires specification of behaviour, which includes both the functional and timing aspects[8]. It will be clearer later(section 3.5), that such systems can also utilize temporal logic expressions to specify timing constraints in the model itself.

In fact, most controllers(control-dominated systems) are by definition reactive, not transformational, with application domains ranging from process control, military, aerospace, and automotive applications to signal processing, ASIC design, medical electronics, and similar embedded systems. Real-time systems also get classified under reactive systems.

Figure 2: Reactive Systems

#### 2.3 Interactive Systems

These types of systems use additional inputs from the user, to determine the output. This makes such systems as an extension of the classical transformational systems, and an old definition[27] merges these into transformational systems. Unlike reactive systems, such systems react with the environment at their own speed(respond to the user only when they can), gathering more inputs, and also providing control(to user) to manipulate the sequence of steps towards eventual output, which the user wants. Such finer distinctions make them a separate class than both transformational and specially reactive systems(unlike few authors, who treat reactive and interactive systems as functionally similar).

Graphical user interfaces and operating system are examples of such systems. These systems are also frequently termed under human-computer interaction systems, though the user need not be a human being.

This document will not focus on interactive systems.

Few other categories, such as concurrent, distributed and parallel systems are introduced[12] while dealing with systems that *necessarily* exhibit some kind of concurrence in their computation. We do not use any such distinction; and hence we omit the details of these as well.

#### 3 Systems Modelling

Much of the usage of models can be attributed to usage of *formal methods*. A formal method in system development is a method that provides a formal language for describing an artefact (e.g. specifications, designs, prototypes, to be introduced later) such that formal proofs are possible, in principle, about properties of the artefact so expressed. The benefits of proving, for example, that unsafe states will not arise, can justify the cost of using such approach.

It will be clearer in section 4.5 that formal proving(known as formal verification activity) needs the artefact description to be *rigorous*. While formal methods can never dislodge the requirement of gathering the system requirements from general users in a non-formal way, the design process can benefit if these informal and hence non-rigorous requirements were converted into a formal specification. Defining what a system should do, and understanding the implications of these decisions, are one of the most troublesome problems in design of complex systems. Hence, usage of formal methods here also, can have major benefits. In fact, practitioners of formal methods frequently use formal methods solely for recording precise specifications, not/not just for formal verifications.

As we can sense from the definitions of the various classes of systems, not many systems are simple enough to be directly(formally) represented as a function mentioned in the beginning of section 2. Similar to a given non-linear transfer characteristic, and design of a corresponding circuit required; the design process of such systems becomes complex. In such cases, the power of heterogeneous systems' modelling is used to assist the design and verification process. Such models are often captured using particular *model of computation*.

#### 3.1 Motivation for Model of Computation

Different papers have touched upon the definition of model of computation: [17], [19], [22], [24], [25] and [26]. None of these deals with the historical perspective of it. To understand that, we need to understand it with respect to the notion of computation.

#### 3.2 Computations and Computational Models

Informally, an algorithm(for a function f) is a finite set of instructions which, given an input x, calculates and yields after a finite number of steps, an output y = f(x). When these steps include arbitrary branching and looping steps to control the formation of output, then the algorithm implies a computation rather than a calculation. The algorithm must specify how to obtain each step in the calculation/computation, from the previous steps and from the input. The algorithm may only yield a partial function<sup>1</sup>. An algorithmic partial function, which is defined on all arguments(i.e., which is total), is called computable or effectively calculable function.

Certain classes of computable functions can be obtained using certain types of steps/procedures/operations; these are the computational models corresponding to those classes of functions. For example, to specify the motion functions(trajectory etc.) of a ball in a Euclidean space, analysis was carried out, and a Newtonian model of computing these functions(the type of steps are the laws of mechanics here) was born. Another example could be the way arithmetic as a model was born: various types of counting

<sup>&</sup>lt;sup>1</sup> Hence, non-deterministic for certain inputs.

\_

systems(integers/rational/irrational etc.) can be modelled using same steps(brackets/division/multiplication/subtraction/addition).

Thus, these models define a framework for **composing** certain types of computations(global actions)(as a sequence of steps, or local actions), much in the same way as axioms are combined in proving theorems. The composition carries some semantics, and hence the framework can only encompass those compositions, whose semantics is expressible. Such a restriction eliminates the possibility of arbitrary compositions: something into which the designers are never interested. Further, the composition style can have space-time flavour. If the local action(steps) are combined in time(one after the other), then the model of computation has a sequential nature(e.g., Von Neumann model). In contrast, If the local action(steps) are combined in time(one after the other), then the model of computation has a parallel nature(e.g., CSP).

#### 3.2.1 Power of Computational Models

These models can be classified<sup>2</sup> according to their computational power, i.e. how large is the class of functions and languages they can cope with. Historically, the initial work done around Turing's time was to figure out a model with "universal power", i.e. model for universal computation. Many different people came up with different models for universal computation at the same time: notable among them are Turing's Machine, Recursive Functions and Lambda Calculus. The same people also proved the equivalence and inter-convertibility of all of these(Hence the name, Church-Turing Thesis), something that is at the core of heterogeneous system design methodology, to be introduced later.

But to perform, or rather model and understand computation behind other kind of scenarios(such as many computers in a room, doing coordinated computation such as pointer-jumping), the sequential model of computation fell short. Hence *distributed computing* was born, which is a different model of computation, and different powers. Similar example can be taken in *quantum computation*, arising out of needs of neural systems' modelling.

Further, these models can also be characterized by their behaviour, or the class of computable functions they represent. Such representation of steps lends them to a domain of application for computation(an example being signal processing, for data flow model of computation). The introduction and usage of *domain-specific languages* (introduced in section 3.5.1) is an outcome of development of such models.

Thus, to summarize, a model of computation is a domain-specific(or domain-independent), often-intuitive understanding of how the computations(in that domain) are done. They arise out of attempts to understand certain physical phenomenon(such as ball-motion), or attempts to use computer in various applications. The components of model of components will be clear in the following sections.

#### 3.3 Relation to System Models

The above definition of model of computation can be concretely *instantiated*, when looked from the angle of various **types** of systems. It is easy to analyze it first from the perspective of transformational systems, such as a compiler.

<sup>&</sup>lt;sup>2</sup> Chomsky's hierarchy is an example of such classification.

**TATA** Consultancy Services

#### 3.3.1 Modelling Transformational Systems

A formal design of system starts from formally specifying the desired behaviour(informal designs such as that used in certain software development communities need not follow this paragraph). To describe system behaviour with a level of precision, we need to think of the system as a collection of simpler subsystems, or pieces, and the method or the rules for composing these pieces to create system functionality. Example of this is the arithmetic model: it deals with a set of objects called integers etc., and operations become the composition rules. Such a specification *models* the desired behaviour. A model is a formal system consisting of objects and composition rules. Thus, whenever a transformational system is tractable, it can be represented as a *composition* in a suitable model of computation. Most simple systems of this kind need only one model of computation, and a representative language for specification of all their pieces.

The notion of composition physically manifests as interaction pattern between objects. In real life, a model of computation typically imbibes sense of concurrency, sequential behaviour and data communication, to name a few types of interaction patterns amongst (computing) objects. Note that interaction patterns noted here are properties of computational models pertaining to system design only; computational models such as arithmetic(used to express calculations) need not exhibit such patterns. Henceforth, we will be using the term *model of computation* only in context of system design.

#### 3.3.2 Modelling Reactive Systems

Though the primary concern of reactive systems is to react to the environment with the speed of it, according to us, even the simplest systems such as an alarm clock has an element of computation hidden behind it(such as the counter). It is that computation, which is functional, and hence tractable<sup>3</sup>. Perhaps for this reason, not only we need to model communication behaviour of such systems, but also the functional behaviour[17]. By considering time itself as an input(or output) parameter<sup>4</sup>, it is possible to depict certain reactive systems as a transformational system.

In any case, a *functional specification* for such system is represented as a set of components<sup>5</sup>, which can be considered as isolated monolithic blocks, interacting with each other and with an environment, which is not part of the specification.

Because of the complexity of (reactive) systems prevailing now-a-days, it makes sense to use domain-specific models of computations to specify sub-behaviours only. Such systems are termed as heterogeneous systems. We will be focusing on heterogeneous system design, section 4.2 onwards.

It is important to differentiate between models used to represent functionality, with the models used to represent intermediate design stages of the system. The models there tend to be successively more detailed in terms of *implementation information*, and the visibility of "which computation" gets subdued. Perhaps the worst confusion arises from the usage of the following terms: abstraction hierarchy of models, synthesis mapping and refinement mapping. A more *generalized* model covering all such definitions, with hopefully more clarity, will be introduced in the remainder of this document.

<sup>&</sup>lt;sup>5</sup> Simple systems such as 8051-based timer used in alarm-only device(hypothetical) may just have a singleton set of components

**TATA** Consultancy Services

Page 16 of 51

<sup>&</sup>lt;sup>3</sup> Models of computation such as CSP and CFSM observe this "local computation" phenomenon; see section 4.6.

<sup>&</sup>lt;sup>4</sup> E.g., Synchrony Hypothesis

#### 3.3.3 Modelling Interactive Systems

Interactive systems also have their idiosyncratic behaviour. Some categories of behaviour commonly observed in interactive systems are: performing an activity in a repeatable way, performing a set of activities in *any order* assuring that each activity will be performed once(e.g., clicking of start/stop/refresh buttons of a web browser), etc. Also required for specifying models is way to capture the dataflow between users and the various elements of the system<sup>6</sup> itself.

In modelling interactive systems, visual formalisms have been observed to reduce the gap between users and analysts. Object-oriented methods like UML offer one of these formalisms<sup>7</sup>. Especially in UI design, UML or the object-oriented methods are now quite prevalent. Even Petri-nets have been quoted as usable model of computation for interactive systems[36].

#### 3.4 Using Model of Computation

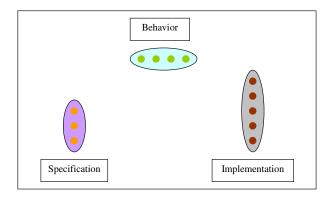

Given that a model of computation has primitives to compose functions, one needs to understand how it is used in the process of system design. Let us understand it *first* from the view of simple systems(or a particular view of system), ones that will *not require*<sup>8</sup> more than one model of computation for detailing, due to their homogeneity.

#### 3.4.1 Enumeration of Behaviour

A typical system *design task* is an enumeration of the behaviour instances that it is supposed to produce. It the set of behaviours carry some structure, the term *behaviour space* can be used in the context.

Given a behaviour space, one can determine the suitable model of computation which denotes a particular kind of behaviour, and hence can be used for, e.g. by formal verification or simulation-based verification to check the consistency of the design. The behaviour can be deterministic, or non-deterministic in the automata-theoretic sense. Even the non-deterministic behaviours can be captured using formalism of model of computation; such capturing is further elaborated in [25].

Behaviour is defined as the unordered set of behavioural units(extensional definition). When the input and output spaces are defined by a set of (important) variables, then a (determinate) behavioural unit is an ordered tuple of values for the input and the corresponding output (vectors). This is the operational view of behaviour. The set of all possible behaviour units denotable by a model of computation is the corresponding behaviour space<sup>9</sup>. When the system is physically excited with a particular input vector, it generates a *simulation run* for the system. Such a run yields an element(point) of the set of all possible behaviour units of the system<sup>10</sup>. Note that such variables should adhere to observability criterion(some authors denote

<sup>&</sup>lt;sup>10</sup> A system will typically implement a part of the overall behaviour space of the computational model, which need not be a sub-space. If the behaviour is determinate, it will have an alternate functional representation.

**TATA** Consultancy Services

<sup>&</sup>lt;sup>6</sup> The destination of dataflow tends to be different, for each dialogue between the user and the system.

<sup>&</sup>lt;sup>7</sup> Harel's StateCharts is the model of computation behind UML

<sup>&</sup>lt;sup>8</sup> There are times when same system(view) can be represented in two or more models of computation; in one, the representation is succinct, while in the others, not. We are ignoring this detail here; though it helps to make a succinct model in general.

<sup>&</sup>lt;sup>9</sup> Only if the units show some structure, the points can be organized in some space. E.g., model of computation for signal processing can imply a linear space of behaviour.

behaviour in terms of internal state change, or a snapshot, of a system, which is defined but not observable for all types of systems<sup>11</sup>).

A denotational view at the term behaviour tells that it is a view, which captures both the function and the timing aspects of any system(already pointed out in section 2.2).

#### 3.4.2 Providing Specification

One can also represent the desired system behaviour as a formal specification(for computation) within the model of computation. For details of specification languages, see section 3.5; at this point it is sufficient to say that such a formal representation requires a (formal) specification language. A sentence<sup>12</sup>, or a syntactical structure<sup>13</sup>, in a specification language represents a set of behaviour units(in other words, subset of the power set of behaviour units denotable by a model of computation). Hence, a set of sentences representing the system behaviour, actually imply set of such subsets. A *functional* input-output *relation*(behaviour), when specified using some language, is known as the system functionality.

A misnomer for behaviour is the algorithm, and to the extent, specification[17]. Actually, an algorithm is outcome of an implementation decision, and hence cannot represent either. Our definition of behaviour and specification makes it clear that using algorithm is indeed a misnomer. As another contradiction to above statement, sometimes the algorithm(for system) is standardized, in which case behaviour and specification get (reverse-)derived from the same!

Formal specification languages are based on mathematical/logical semantics, and hence the sentences of specifications in them can be used to reason about(validating) extensional properties of the system, or the behaviour. Like the (truth) satisfaction criterion of logic formulae, a specification covers a system, if there exists a satisfaction relation between the set of sentences of the specification, and the set of expected behaviours.

#### 3.4.3 Providing Structure

One can construct physically, an implementation<sup>14</sup> of the system, by providing a structure consisting of (countable) sets of components of various types, and their interconnections as well as interaction patterns(e.g., scheduling strategy). While the specification tells how the system will work(behave), the design process is incomplete till it is described, how the system will be manufactured. Many-a-times, especially for simpler systems, the design process is interchangeably used for the implementation (sub-)process, which is a loose usage. An implementation of a component, or an artefact, subdues certain information about it, such as design constraints, standards, performance goals, etc., which are part of the design process.

While we discuss the difference between the terms, architecture and implementation, in a later section, it is important to state that implementation within a model of computation does not

<sup>&</sup>lt;sup>14</sup> We will differentiate between architecture and implementation in a later section: a difference that is important, but can only be understood while dealing with multiple models of computation.

**TATA** Consultancy Services

Page 18 of 51

<sup>&</sup>lt;sup>11</sup> E.g., the state of an executing program over a processor is supposed to be the snapshot of all its variables/registers and the program counter.

<sup>&</sup>lt;sup>12</sup> Abstractly represents notion of equation between two sets of variables, whose solutions are points in the behaviour space.

<sup>&</sup>lt;sup>13</sup> Similar to notion of a non-terminal in context-free grammars

necessarily imply an "executable" artefact<sup>15</sup>. This is because the (high-level) structure may not have all the details required for execution.

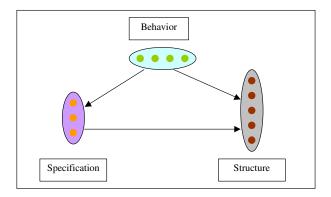

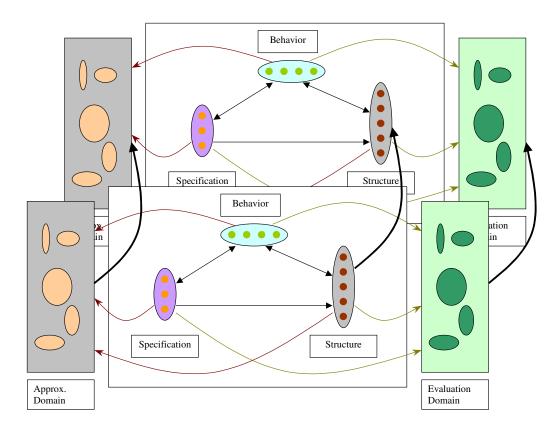

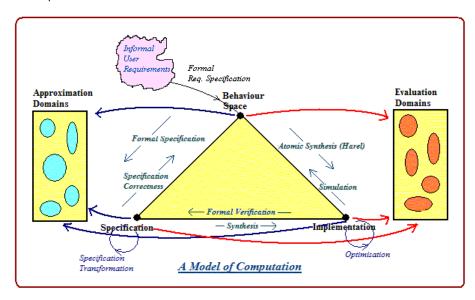

A usage diagram for model of computation can be viewed as follows.

Figure 3: Using Model of Computation

#### 3.4.4 An Example

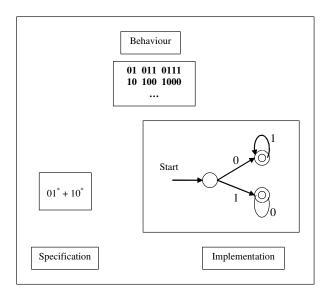

Finite-state automata[2](the corresponding languages being *regular languages*) is a typical example of a model of computation, used in design of control-dominated systems, and also components such as user interface.

The behaviour space for this model of computation is the set of all regular sets  $\beta\subseteq \Sigma_k^*.$   $\Sigma_k$  is the k-element alphabet for input/output.  $\beta$  is a particular collection of strings formed out of  $\Sigma_k^*$ , hence the behaviour units involved here the strings itself. The behaviour of an individual FSA is thus a regular set.

The specification of an individual FSA is done via the notion of *language*: the language describes the *intension* of the regular set in some way. For example,  $\{$  w: w consists of equal number of 0's and 1's  $\}$ , and 01\* + 10\*(the regular expression notation) are two different (types of) specifications for automata.

The structure, or the implementation of an FSA is provided by the five-tuple notation: A = (Q,  $\Sigma$ ,  $\delta$ , q<sub>0</sub>, F). Visually, it is also represented as a graph. The structural elements of the FSA implementation are the states and inputs symbols. There can be multiple implementations of a FSA: DFA, NFA and  $\epsilon$ -NFA are equivalent implementations. A more detailed structure can be captured in the Esterel-Lustre common format, OC.

The usage diagram for the FSA thus looks as following.

<sup>&</sup>lt;sup>15</sup> Unless one uses an interpreter.

TATA Consultancy Services

Figure 4: Using Model of Computation for FSA

#### 3.5 Languages and Models of Computation

To do formal specification, modelling(or specification) languages are required in each model of computation. But the scope of what can be specified using a language need not be restricted to elements of single model of computation. Some good discussion on languages and models of computation can be found in [17], [24].

It is important to distinguish between programming languages and specification languages. Programming languages have been conceived primarily to express algorithms, which, as said earlier, is an outcome of implementation decision. Hence, programming languages should be seen as a tool to describe *implementation* details. In terms of generality, programming languages support many models of computation, and hence sometimes be classified into a separate, heterogeneous model of computation[24]. Specification languages are used to capture *a set of* properties of the system; for the model to be able to represent, what is to be designed for. Hence, not only specification languages focus on providing aid for specifying one or more properties of the system(such as temporal aspect of behaviour), but also they can be abstract and incomplete. This is perfectly valid, for the purpose of modelling is to look at useful abstractions of a system. We will focus here on specification languages.

The semantics of a language maps a given(syntactically correct) specification into a point of the behaviour space corresponding to the model of computation. The mapping may not be surjective: it depends on the level of abstraction, or the degree of incompleteness, that the specification language exhibits. This degree is captured using the term *expressiveness* of a language. Expressiveness implies which behaviour units can be described using a particular language. Intuitively, there can be preorder relation between the languages based on expressiveness[15]. Such partial order of languages is denoted by language embeddings. It is such partial order, which is exploited while doing design (process) using a set of specifications.

#### 3.5.1 Domain-specific Languages

A domain-specific language (DSL) is a programming language or executable specification language that offers, through appropriate notations and abstractions, expressive power focused on, and usually restricted to, a particular problem domain. Hence, in different domains, more succinct models can be designed.

The initial work on models of computation was mostly domain independent, i.e. universal model of computation. Scott introduced denotational semantics, and it resulted in domain-specific models of computation. Correspondingly, the new-generation languages such as SILAGE differ from the GPL such as 'C'.

Because these languages are declarative and hide much of the implementation details, some of them can be considered more as specification languages than programming languages. Hence, one of the (many) important advantages of these languages is that they enable more properties about programs to be checked. In contrast to a GPL, the semantics of a DSL can be restricted to make decidable some properties that are critical to a domain. For example, Unix command make reports any cycle in dependencies and thus totally prevents non-termination (assuming the individual actions do not loop).

#### Ordering using Expressiveness of Models of Computation

Just like the expressiveness of language can form a partial order, a set of models of computation may themselves be partially ordered.

The "order" relationship gets formed due to the notion of relative computational power(defined in section 3.2). The computational power, i.e. what functional aspect and what temporal aspect a model of computation can cover(we are looking from system design perspective throughout) can be understood(if not a quantitative comparison) using denotational and other semantics of the model of computation[17],[22] and [25].

A reflection of such order can be seen in the so-called abstraction-based hierarchy of models of computation(an example being the stages of design flow in hardware-only system, or digital circuits', design). Though that hierarchy is based only on the level of implementation details which can be captured in models of computation, it will be clear in section 4 that even specifications can be refined. This is possible only when the model of computations involved have a known subset sequencing  $^{16}$  in terms of computational power (MoC<sub>1</sub>  $\subseteq$  MoC<sub>2</sub>  $\subseteq$  MoC<sub>3</sub>  $\subseteq$  ...  $\subseteq MoC_n$ ).

At times, the order of subsuming is not very evident, or perhaps cannot be quantified. In such cases, analogies can be used to approximate the order. For example, differential equations(model of computation for analog domain) which govern a sequential circuit may not be comparable to finite automata. But, differential equations can be approximated into difference equations, which drive the design of an FSA for the sequential circuit. Hence, they are comparable. Of course, analog equation subsumes finite automata, due to additional semantics(there can be non-linear differential equations).

Diagrams such as Gajski and Kuhn's Y-state diagram, and their extensions become a specialization of such a formulation(a planar diagram can be developed for the order mentioned

<sup>&</sup>lt;sup>16</sup> Note that only reflexivity and transitivity are required from the relation: not the anti-symmetry, and hence the sequencing forms a preorder rather than partial order.

above). Once we introduce the mapping functions amongst the three views of usage, as depicted in Figure 3, in section 4, this statement will become intuitively clear to the reader.

Interested people can also look into meta-models of computations, such as X-framework[11], or the tagged-signal model[25]. Such meta-models form the basis of comparison of models of computation. A category-theoretic formulation will be introduced in section 4.3.4.

#### 3.7 Operational Semantics and Model of Computation

To be able to specify runtime behaviour of a specific model, the following aspects can be used:

- Nature of components from which the system will be constructed (e.g. cyclic, sporadic, protected, passive)<sup>17</sup>

- Scheduling paradigm under which the system is executed and the associated mechanisms(e.g., interleaving or non-interleaving semantics).

- Means of communication between components/objects (e.g. mailboxes)(not required for SOS)

- Means of synchronization between components/objects (e.g. clock edge, semaphores)(not required for SOS)

- If applicable, the means of distribution and inter-node communication (e.g., shared memory, RPC)(not required for SOS)

- Means of providing timing facilities(clocks)(not required for SOS)

- Means of providing asynchronous transfer of control(interrupt controlling)(not required for SOS)

This list is only suggestive; there is no general method to define the semantics(of any kind) for any model of computation.

$<sup>^{\</sup>rm 17}$  E.g., intensional definition of sets in E-R model of computation for databases.

#### 4 Design Using Formal Models

A significant application of formal models in designing systems arose from the semiconductor design area. There has been evolutionary change in the functionality packaged in an IC. Previously, there used to be a lot of printed circuit boards(PCBs) doing various individual functions. This required a lot of hardware integration skills. But as the Moore's law defines the temptation of chip making companies to pack more and more electronic functions on the same chip, the world within the chip moves from just being a computational component, to a complete system. Such an evolution brings the idea of dealing with models and synthesis, which come from hardware domain. Thus, the digital circuit design for VLSI is moving into what is known as digital systems' design, with integration level still as high. This is what is known as the system-on-chip design movement in semiconductor area<sup>18</sup>. However, it is not that all components get inside one chip. It is the system design process, which takes such architectural decisions.

We will first try to look at designing systems using one model of computation. By this, we imply the dominant view of a system, which can be one, such as FSA in an FSA simulator. Note that the *structure* we come up with is not the final implementation. For that, refinement is required to make it either a hardware or software piece, something, which we introduce in later sections. For notational purposes, we will call such systems *simple*.

#### 4.1 Simple Design

Figure 5: Mappings within Model of Computation

Mapping a specification into an implementation, or structure, within a model of computation is known as synthesis step<sup>19</sup>. It is also possible to map(at least in few cases) a set of orthogonal behaviours, of a behaviour space, into the required structure of the system. For example, using the *Shannon's expansion theorem*, and using multiplexers, complex logic circuits can be built

<sup>&</sup>lt;sup>19</sup> We reserve a term, "heterogeneous synthesis", to be used in context of heterogeneous system design.

icsci

<sup>&</sup>lt;sup>18</sup> Also to note that applications of system design methodology is not restricted to chips only; embedded systems as simple as a digital wristwatch can be designed using this. In fact, Esterel, a language to specify reactive systems has been already used in design of digital wristwatches.

inductively from 1-variable systems, using finite number of synthesis steps. Another example of such atom-level synthesis is the usage of (trivial) state-walker design pattern. A computation function can be designed for each such atom(can be FSA/procedure/circuit), and notions of combining them in parallel(using  $\epsilon$ -transitions/switch-case/multiplexer) be used to make them all running together. Such a synthesis in most probability will not be optimal: element-by-element design may ruin the cost requirements(see next section).

#### 4.1.1 Cost Functions

No structure can be designed, without having certain cost constraints as requirements. We quote here a few examples.

- Transformational systems such as compiler may not have run-time specified as cost, but most reactive systems will show stringent run-time costs.

- A software processor(running a RTOS) can be characterized from the performances point of view by its utilization rate (acceptation level can be less than 80%).

- A communications node such as a bus can be characterized by its throughput, a shared memory by its read/write latencies.

- Code size is another cost, which is measured in case of automatic software generation.

- Clock cycles taken per instruction execution can be taken as cost for a microprocessor.

- The cost can be *business*-driven: life-cycle cost(time-to-market), monetary cost(product pricing), speed, reliability, size, weight etc.

It is imperative, that the costs need to be captured during the time of specification. The specification process captures primarily the properties of computation involved(can be used for formal verification), and secondarily, the cost properties(sometimes as *constraints*). The design process, hence, also needs to analyze the cost of a particular structure.

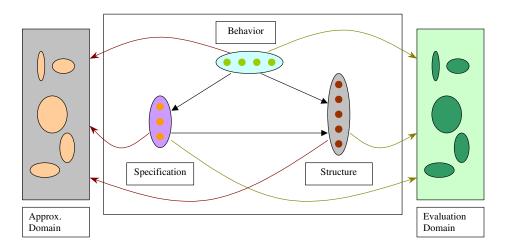

For this purpose, we introduce two domains in our diagram: the evaluation and the approximation domain. These domains can be extensionally defined as sets of integers, reals etc, and the cost functions become the mapping to such domains. If a cost is measurable(the domain of the mapping observes either a total order, or a lattice), then the functions can be evaluated. In a particular model of computation, certain cost can just be approximated(such as delay calculation in a DFG). In such case, the actual cost can mostly be evaluated(e.g., delay calculation after a gate-level model evolves from DFG, post scheduling/binding), when sufficient implementation details are available in another model of computation, into which we have refined our structure(see section 4.3.2).

Thus, we introduce side functions to these domains: they can be performance evaluation or constraint<sup>20</sup> analysis. The model is analyzed to derive value for these constraints. One might need to look at *intensional* aspects of the domain of the mapping(say, for property verification), or at the *extensional* aspects(say, performance evaluation). There can be secondary parameters, rather the just properties of computation, which give rise to these costs. Implicit overheads of event handling, access time to driver are examples.

$<sup>^{\</sup>rm 20}$  The constraints can be min/max delay constraints, execution rate constraints etc.

[21] provides an example treatment on constraint specification and analysis. Recent frameworks such as METROPOLIS also provide support for this, explicitly.

The evaluation domain can also have members as properties that the design must specify. For example, presence of a dead state in an FSA points to something wrong in the synthesis algorithm. These are the condition evaluations; i.e. the conditions, which are supposedly true for some model expressing a type of computation.

Abstract interpretation is one of the ways of realizing the approximation functions. Once approximated, techniques such as model-checking(refer section 4.5) can be combined as well, for property analysis[37].

Figure 6: More Meaningful Structure of Model of Computation

#### 4.1.2 Sources of Cost

The problem can also be thought of describing the *domain* for the cost *function*. The cost is calculated for a particular implementation, or a structure; though specification/behaviour analysis can also provide approximate costs, or bounds on the (range of possible structures).

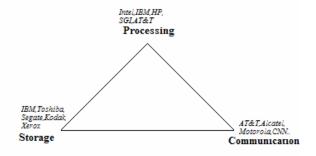

Irrespective of the model of communication, the major *quantifiable* resources constituting any information-processing system are <u>processing</u> power, <u>communication</u> bandwidth and <u>storage</u> capacity. This is because these are terms are also embedded in the notion of computation. Their representation is known as the info-action triangle<sup>21</sup>[10].

$<sup>^{21}</sup>$  The term **info-action** is used to denote any of the **info**rmation handling **action**s listed above.

т.

Figure 7: Info-actions and companies built upon them<sup>22</sup>

Let us take a simple, sequential machine system. The processing power is representative of the power of individual elements: e.g., 2-input AND gate has less processing power than 3-input AND gate. The communication power manifests as the bandwidth of internal busses. The storage manifests as the capacity of registers.

As another example for a *non-trivial* data-flow graph[3], in which the processing and communication resources are obvious, but not the memory resource, it can be found represented in the loop-back edges of the graph.

Thus, these terms are polymorphic; in various models of computation, they arise under different guises. A few exceptions are, for example, a resistive network. Though memory is present in terms of parasitic inductance and capacitance, it does not play significant role in the computation represented.

We conjecture that these resources are *implicit constituents* of any known cost function, in any model of computation. As an example, the communication aspect of a system/computation impacts the wire/bus/protocol cost(in a distributed system) of a particular structure. A high-end processor may impact the monetary cost, simply because it is very expensive. A memory-intensive design can impact the reaction speed of a system to a stimulus, simply because i/o operations tend to take more time<sup>23</sup>.

As noted in [10], the costs associated with these resources are functions of the "state of the art" of the core technologies associated with these areas. Since this "state of the art" is continuously changing due to the advances in *scientific understanding* and *technological innovation*, it is clear that these costs themselves are a function of time.

Since these constituents impact cost, one would ideally like to minimize each one of these. They cannot be but minimized to zero; the *lower-bound theory* ensures that they can be designed to meet time/space complexity asymptotically. As an example, the Myhill-Nerode theorem tells that there need to be a minimum number of states in a FSA designed for a regular language. This impacts the size of memory, which is correspondingly required for

<sup>&</sup>lt;sup>23</sup> The invention of B-trees as data structure for efficient search was driven by the fact that secondary storage devices, on which huge amount of data can be stored(required for certain database applications), are slow in responding, and hence disk i/o operations needed to be minimized.

\_

<sup>&</sup>lt;sup>22</sup> Adapted and extended from *Wavelet Analysis*, *The scalable structure of Information*, H. L. Resnikoff and R. O. Wells Jr., Springer 1998

computation. As another example, in a plastic cell configuration for Reconfigurable computing(see section 4.9), the processing can be just as less as lookup table function.

The three resources mentioned above, though conceptually independent, admit the existence of techniques, which allow one resource to be traded off for the others. This is quite important from an economic point of view, since at a given point in time the relative costs of the resources **do show** a large variance. Supposing we are in need of a resource B which is costlier than A and C. In such a situation, it may be economical to use A and/or C in conjunction with techniques which trade off B for A and/or C.

Tradeoffs are a way of life in doing *optimal designs*: there are resource tradeoffs not just to optimize a single property, but also there are tradeoffs to optimize a property at the expense of other. Hardware literature gives a nice picture of such optimizations: an example being the delay-area trade-off(arising out of a lower bound on area-time complexity).

#### 4.1.3 Choices during Design

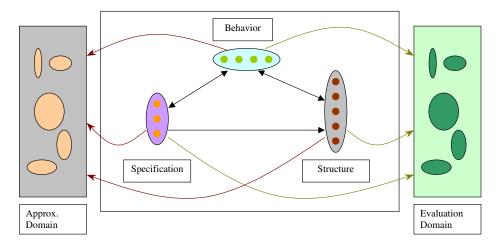

Most of the arrows in Figure 6 imply one-to-many mappings that lead to availability of choices during design process.

Since the behaviour is fundamental to a model of computation, it can be captured by more than one specification in the same model. For example,  $0^{n}1^{n}$  and  $\{w: w \text{ has equal number of 0s and 1s}\}$  are essentially the same specifications for some language. Hence, the relation between behaviour and implementation is a one-to-many relation.

Similarly, a specification may have many correct implementations. Such an implementation is said to satisfy the specification. The reason driving many correct implementations is the optimality of solution, given the constraints. There can be many optimal solutions; such a phenomenon is known as Pareto Optimality in design community.

Finally, behaviour to structure mapping is one-to-many. The notion of model of computation for the overall design can be intuitively described as composing the required computation, or behaviour, in terms of various computing elements(executing certain types of steps, or subcomputations). There can be many such compositions, the better design will correspond to the degree of satisfaction of constraints specified. Hence, one might think of this mapping as many-to-many as well.

All the mappings can be partial: not all behaviours are *expressible* using formal specification notations. Similarly, not all behaviour/specification are *implementable*. An example is the existence of synthesizable subset in VHDL behavioural modelling.

By modifying Figure 6, we have the following figure, in which arrowheads denote the direction of the many-side of the mappings.

Figure 8: Complete Structure of Model of Computation

#### 4.2 Motivation for Heterogeneous Systems' Design

The systems we discussed in last section are far too simple to be used in practical life. In general, the systems are *heterogeneous*, implying that there is co-existence of a large number of components of disparate type, function and properties.

As an example, a banking system involves transformational payroll programs, interactive access to database of clients, and reactive automatic teller machines and man-machine interfaces. Another example is of a compiler, that may be seen as a transformational from the outside, but internally it may be constructed in an interactive style out of concurrent processes which communicate via data streams; or a client-server application is interactive, but the calculation of the server's return upon the client's request may be a transformational step such as just returning the contents of a requested file.

A formal capturing of heterogeneity can be done using the concept of model of computation. Not all systems are simple enough to exhibit monolithic behaviour in one particular model of computation. For example, a simple numeric calculator not only requires a model in which a sets of "modes" and transitions can be handled, but also a model in which calculations, it's primary function, can be done. In such a case, perhaps a marriage of FSM model for modemanipulation, and "arithmetic" model for representing numeric calculations will be sufficient.

This gives us an opportunity to think, that there can be choice for sub-systems or components as to which computational model is most suitable(e.g., type of FSM for representing the UI component). The next section is devoted on such details.

There are times, when the presence of human-friendly mechanisms[28] nudges a person to make the specification in a different model of computation. For example, 'C' derivatives: HardwareC/SpecC etc., or the C++ derivative: SystemC. In such a case, we anyway need to deal with multiple models of computation. We cover this angle as well.

#### 4.3 Tackling Heterogeneity

#### 4.3.1 Multi-modelling

We already hinted the usage of multiple(see section 4.6 for details) models of computation. We elaborate here using an example of a mobile handset. The RF transmitter/receptors can be designed using analog electronics as the computational model. The baseband processing of signals can be designed using the dataflow family models of computation such as synchronous dataflow. The protocol stack can be designed using models such as CFSM, or in a little more crude way, Harel's StateCharts. The middleware components such as event manager can be represented using semantics of entity-relationship model, and the applications can be driven by a normal FSM.

Another fundamental requirement of having multiple model is to accommodate components, which are *external IP*. By this term, we imply a component, which has been specified and developed by others, and purchased for the sake of making a bigger system.

Given such a thrust, we also need to look at how these models combine together. Furthermore, we need to look at what it means by combining models of computation.

#### 4.3.2 Cost Distribution

We now refer back to section 4.1.2, and notice a few things about the cost or property mappings. One thing to notice that certain costs and properties(barring the ones in info-action triangle) are only measurable in a limited(or one) model of computation. For example, number of dead states can only make sense to be evaluated in FSA model, though the presence of significant number of such states can adversely affect the overall performance of a heterogeneous system, in which it is a component.

What is consistent, however, is the presence of the info-action triangle, which, according to our conjecture, drives all these cost mappings. The limit to which they can be reduced is dependent on the model of computation(e.g., in a plastic cell configuration, processing can be really reduced). Still, once the trade-off between these within a model of computation hits a wall, in a heterogeneous system, one can further try to redistribute these costs by appropriately choosing the models of computation. E.g., the whole cost of memory can be reduced by choosing an appropriate set of models of computation.

Design of heterogeneous systems based on info-action cost distribution, though obvious and intuitively appealing, according to our limited study, has not been explored. Hence concrete examples cannot be provided.

#### 4.3.3 Refinements

Refinement literally means that crude oil still produces refined oil! Refinement(and abstraction) mappings are one aspect of combining multiple models of computation. Refinement implies defining vertical mapping between same aspect of two MoC: say a structure in MoC 1, mapped to structure in MoC 2. Refinements can be **concatenated**: this forms the design methodology. The terms initial MoC, intermediate MoC and final MoC have their meanings implied, thereby.

There is an associated notion of abstraction level. Refinement is defined as mapping from an (more) abstract MoC to a less abstract MoC. The level of abstraction can be measured by comparing implementation details[8]. Furthermore, the MoC in question theoretically should

also be related. The relation implies that the behaviour space should be preserved(in at least one direction), while refinement, though this relation may not be as straightforward to state. Finally, the abstraction level perhaps is defined only **within** a particular flow chosen; the same MoC may be less abstract, or more abstract, depending on which MoC it is compared with. Hence, the hierarchy of abstractions used in a flow might look independent of each other.

Why is refinement done? Or how is it identified, that an artefact in a particular MoC needs to be translated into another MoC as intermediate, before having a specific MoC as final? We point here few of the reasons:

I. One of the reasons is the availability of tools for verification/simulation at a particular level of abstraction. There are instances of such trials: e.g., usage of VHDL(RTL/behavioural) simulator for doing co-simulation in POLIS, while the specification language is in ESTEREL. Multiple specifications can be refined to such a level, where commercial tools are available.

On the negative side, such a refinement, e.g. refinement to VHDL, implies restricted symbolic debugging capabilities. This is because the correspondence between the refined VHDL code and the original specification can be fairly loose.

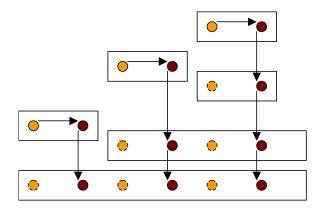

Figure 9: An Example Refinement

II. The other reason is exploiting the partial order of MoC, wherever possible, for better calculation of associated costs. Partial order can give rise to refinement of properties(both intensional and extensional), which can be measured at some MoC, and which can be close approximate of a final calculation.

One hidden problem in this case is that one MoC can be refined into more than one(can participate in multiple partial orders). In that case, one has to decide which one to choose. Parameters such as familiarity with a particular model of computation are used to help resolve the tie in practice.

- By refining few models to a particular MoC, insertion of external IP can become easy. Bringing them to a single platform saves the overhead of thinking and using the interaction semantics. Non-sophisticated tools can be used at this particular MoC level.

- For formal verification of some property, abstraction mapping(opposite of refining) are used at times. This implies that certain properties are dropped from consideration. There are instances of CFSM being converted into synchronous FSMs<sup>24</sup>. When we explicitly focus on proving one property, the job can be eased by omitting the non-relevant details.

- At times, an intermediate MoC is defined for portability reasons. That is, a model is translated into another model in another MoC, from which components can be translated independently into multiple MoCs. E.g., the CDFG created by 'C' compilers. The CDFG can then be synthesized into the instruction-set model of computation for various processors.

There are many types of refinements, all driven out of formal methods. Interested person can look into [12].

Figure 9 depicts a simple refinement process.

#### 4.3.4 Category Theoretic Formulation of Problem

The best way to mathematically formulate the above two issues into a single problem is by using Category Theory[4], which is a general theory of structures. It deals with describing precisely many similar phenomena, or specifically, constructions with similar properties. One can thus transport, and study the set of all models of computation using Category Theory. By doing so, one essentially studies the semantics of various models of computations, and the relationship(such as embeddings) amongst them.

As an example, a category can be formed to deal with study of class of all vector spaces, and linear transformations amongst them.

Quoting [4], a category is denoted as a quadruple  $(\Theta, H, id, o)$ , where

- ⊕ denotes a class of similar structures, such as class of vector spaces

- H is a set of relation between two members of  $\Theta$ : members of H(A,B), where A,B  $\in \Theta$  are known as morphisms.

- Id is an identity morphism for each object A:  $id_A: A \rightarrow A$ .

<sup>&</sup>lt;sup>24</sup> CFSM is more detailed MoC here.

• o is the composition law for morphisms. If f: A  $\rightarrow$  B, and g: B  $\rightarrow$  C, then gof: A  $\rightarrow$  C. Composition is the fundamental primitive in Category theory, in the same sense that membership is the fundamental primitive in Set theory.

By looking carefully, it makes sense to treat each MoC as a Monoid. That is, the refinement relations(wherever applicable) between them, which form the morphisms, will be associative, and there will be an identity element. The identity element maps the set(in our case, a MoC) to the same MoC, thus forming a loop. One of the interpretations of such loop is local optimization, which may lead to a different structure within the same MoC. The morphisms can be interpreted as interaction between two MoC, i.e. how two structures in two different MoC interface with each other, and cope with the dynamics of such interfacing(paramount problem in composing heterogeneous systems). In real life, such morphisms are implemented using transducers.

Point work has existed so far, marrying two models of computation at time. Category Theoretic approach promises a "grand unified model of computation".

The issues with doing such unification are perhaps expected: notable among them are

- Out of the universal set of computational models, few subsets form a set(non-zero) of partially-ordered computational models. The partial order relationship is a kind of embedding.

- A particular computational model may be part of more than one subset. In such a case, work can still be done to form a total order out of these two partial orders.

Pioneering work has already been done on these lines: one can refer to [25] and [30].

#### 4.3.5 Terms and Details

Now, we introduce few terms related to system design.

#### 4.3.5.1 Design Task

A design task is a bare-bones definition of the system to be designed: it is like a customer telling: "Gimme a reference design of a digital camera having 256 KB flash, auto focus ability, ...". The design task may further mandate re-use of certain pre-designed components. The design task may also have a collection of specifications(only a part of the overall system behaviour) of for re-use purposes.

#### 4.3.5.2 Design Methodology

Typically known in the industry as the job of an architect, this involves breaking up the design task into design subtasks. The design subtasks imply modelling and designing components in the MoC decided for them, e.g. auto-focus algorithm on a DSP processor. To make a choice of componentization and their bindings requires understanding of various application domains. The design subtasks also utilize refinements, wherever required.

If we were to visualize a vertical tiling of various MoC, as depicted in Figure 9, then we can see that a design methodology forms a path in the graph. The jumps in the graph consist mainly of synthesis and refinement steps(Harel[27] was the first to note these). There is also at least one node with in-degree as 1, and multiple out-degrees. This is the node where the high-level

architecture is defined. This node can be the source itself, or can be a virtual node, where we simply start with predefined set/architecture of components.

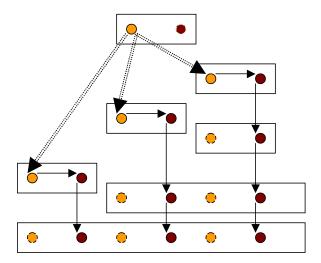

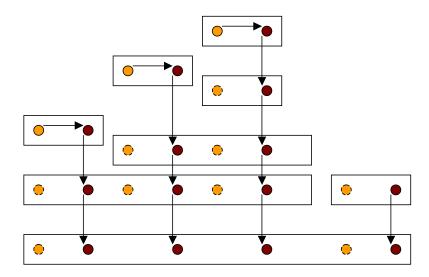

A few figures, based on the reasons cited in section 4.3.2, are shown below.

Thus, formally speaking, a methodology is a set of models and transformations, possibly implemented by CAD tools, that refines the abstract, functional or behavioural specification into detailed implementation description ready for manufacturing. Typically, in the hardware verification domain, the machine derived from a high-level system description like RTL or behavioural spec is termed the specification, and the description corresponding to the low-level difficult system description, perhaps at the gate or the switch-level, is termed the implementation. Such incomplete definition gives rise to confusion, for it does not reflect the essence of behaviour-preserving refinements. For example, compiling a Lustre specification into gate-level netlist(using it's compiler), with FSA as intermediate MoC, resembles a vertical, diagonal refinement, which can lead to confusion.

Figure 10: General Methodology

Figure 11: Methodology for reason V

Mostly the refinements are done structurally; but it has to explicitly or by simulation, guarantee that the behaviour is also consistent(equivalent), or it gets refined as well. The independent hierarchies(functional/behavioural and structural) are defined in [8].

The design flow need not start at all from a specification. The requirement can be changing a structure in one MoC to another. For example, someone gives a digital filter, and wants it to be converted from DSP code, to sequential circuitry, and then to hardware. This is driven by the fact that the customer foresees some kind of constraint satisfaction/cost advantage, for which the implementation is being changed. There can be point conversions also, driven by similar constraints. By adopting such definition, we counter the myth that the design methodology is a sequence of steps that transforms a set of specifications, described informally, into a detailed specification that can be used for manufacturing. Such a definition implies that intermediate steps are characterized by a transformation from a more abstract description, to a more detailed one[22], which is not always the case in industry(author's experience).

Figure 12: Methodology for reason I and III

#### 4.3.5.3 Design Process

The design process comprises of the complete details("how") of all the sub-tasks under the design methodology *adopted* for the required design task. It includes defining configuration management, quality matrix, tools to be used at various stages and in various MoC, checkpoints during refinement and the method used, the choice of language for software components, to name a few. Needless to say, this is the point where abstraction stops, and reality sinks in!

#### 4.4 Elements of Methodologies

Methodologies exist for hardware-only design[3], software-only design[12], mix-mode IC design(having both analog/digital hardware), hardware-software Codesign, and the emerging field of Reconfigurable systems' design. We look here at details of design methodologies, in general.

#### 4.4.1 Models and Specifications

What is provided at times, or is rather available in case of heterogeneous systems is the collection of requirements, mostly stating input/output tuples for the system in some form, in the name of design task. The analysis step from this should lead to regrouping them into subsets of related requirements. If it is possible, then the design task is said to have a behaviour space. In the degenerate case, the set of independent requirements in practice being finite, they form a space by themselves: we do not cover such case in our definition. In such a case, one can write down specifications(as some type of logical formulae), in some specification language, which will relate to each of these subsets. It is from these subsets, the author's experience says, that one can derive the first hints of a possible architecture. A variation of this

problem is also known as the hardware/software partition problem, to be introduced in section 4.8; and this is currently an active area of research.

From these specifications, models are prepared, which then go into the design flow. For complex systems, it is inevitable that specification and implementation views of an evolving model have to be intertwined or interplayed, during the development activities, at different moments and also at distinct levels of abstraction. For instance, the whole system can be seen as a module and a state machine devised for it. We can later decompose the system in subsystems and create, for each one, an activity diagram that represents the respective function. The sub-systems can by themselves, be decomposed in objects, which can have their life-cycles represented by a Petri net. We can go as many levels as we want, and as modellers, we are always changing specification/behaviour rather, into structural view, and vice-versa.

#### 4.4.2 Design Flow

Design flow refers to the patterns shown in section 4.3.5.2. A design flow need not be a vertical line: though any strand of vertical line implies that models show an embedding. There can be many models of computation, which will play part of intermediate models of computation. A set of models of computation will be the final models: after reaching an implementation/structure here, the designer/architect will not bother about any further conversion to any such structure. At these MoC, implementation details are very clear, and each component also has a clearly defined function/behaviour.

The design flow can branch out at any point(see Figure 11) into multiple MoC. This introduced additional interfacing requirements, which can be broadly grouped into *synchronization*(e.g., software scheduling) and *communication*(e.g., transducer design) requirements.

Integrating reusable blocks of IP into a particular model requires compatible abstraction levels between the reused IP and the rest of the model, or at least bridges between levels. For example, most of today's IP blocks are available either at the register transfer or transaction level for hardware, and either source or object code for software. Bring to same MoC can help in joint verification(an important requirement) of the entire model.

Existing design tools are basically of two sorts:

- Mainly focusing on functional design, the first come from the specifications domain to reach the detail design of the components(top-down process).

- Mainly focusing on platform design. This introduces a re-use based design process, and hence tends to be bottom-up.

The current problem in industry also lies in the fact that different people follow different design methodologies tailored by the experience of their development communities. Still, these methodologies can be broadly grouped under three categories.

#### 4.4.2.1 Top-down Approach

In top-down approach, a comprehensive model is captured using a single specification language, such as SpecC/SystemC. At the topmost level, both the behaviour and the structure may be highly unspecified(lacking details). The behaviour of such a model is then decomposed. Decomposition includes the delegation of part of behaviour(function) to an architectural

component. As a side observation, the structure of this graph resembles the structure of a DFA. A detailed picture of this approach is given in [27].