# Optimization of silicon nitride for SONOS flash memories by trap characterization

#### A dissertation

Submitted in the partial fulfillment of the requirements for the degree of

### Master of Technology

by

### VVSS SATYASURESH CH 08307R22

under the guidance of

Prof. Anil Kottantharayil

Department of Electrical Engineering

Indian Institute of Technology Bombay

June 2011

#### Abstract

This report describes the process optimization and trap characterization of the silicon nitride charge trap layer for SONOS flash memories by using Low Pressure Chemical Vapor Deposition (LPCVD) with SiH<sub>4</sub> and NH<sub>3</sub> as source gases. Silicon nitride in LPCVD can also be deposited using chloro-silanes typically dichloro-silane (DCS) and ammonia (NH<sub>3</sub>) but requires extra bubbler and vaporizer arrangement to feed the reaction tube. Also the formation of NH<sub>4</sub>Cl during deposition is detrimental to the pumping system due to the clogging of NH<sub>4</sub>Cl particulates. On the other hand, the LPCVD system with SiH<sub>4</sub> and NH<sub>3</sub> is simple and easy to maintain. However the large non-uniformity in thickness and film composition are the main issues with silicon nitride films deposited by SiH<sub>4</sub> and NH<sub>3</sub> system. In this work the results of SiH<sub>4</sub> - NH<sub>3</sub> system with N<sub>2</sub> as diluent for depositing silicon nitride films are presented. A significant improvement in uniformity is observed when N<sub>2</sub> is used during deposition. Effect of process parameters on the film thickness and composition is studied. A breakdown field of 8.5 MV/cm is obtained for stoichiometric silicon nitride films.

Trap characterization results on SNS capacitors are described and effect of  $N_2$  dilution on trap density and distribution is studied. Trap density and energy distribution of traps are determined from program transients and retention measurements. The trap density is of the order of 2.5E18 cm<sup>-3</sup> and is distributed in the energy range 0.74 - 1.5 eV. Capture cross sections of both electron and hole traps are calculated.

#### Acknowledgements

First of all, I would like to thank Indian Institute of Technology Bombay for giving me the opportunity and providing facilities to do this project.

I sincerely thank my guide Prof. Anil Kottantharayil for his encouragement, direction, guidance and support during the project. His recommendations and suggestions have been invaluable for the project. I would like to thank him for sparing his valuable time to review manuscript of the thesis.

It is my pleasure to thank all the people who helped me directly or indirectly in the progress of this project. I am grateful to all the technical and non-technical staff members of the nanoelectronics fabrication facility for their support without whom this project would not have been possible.

I would like to thank all the members of flash memory group for their valuable suggestions in solving process related issues. I would also like to thank the RAs of characterization lab for their support.

Special thanks are due to my friends in IITB for their support and motivation during hard times.

Finally, I would like to thank my family members for their support and encouragement during my academics.

## Contents

| 1 | Intr  | oducti  | on                                               | 1  |

|---|-------|---------|--------------------------------------------------|----|

|   | 1.1   | Organ   | zation of the Report                             | 4  |

| 2 | Lite  | erature | Review                                           | 5  |

|   | 2.1   | Evolut  | on of SONOS memory                               | ŀ  |

|   | 2.2   | SONO    | S charge injection mechanisms                    | 6  |

|   |       | 2.2.1   | Tunneling based charge injection                 | 7  |

|   |       |         | 2.2.1.1 Direct band to band tunneling (DT)       | 7  |

|   |       |         | 2.2.1.2 Fowler-Nordheim Tunneling (FN)           | 8  |

|   |       |         | 2.2.1.3 Modified Fowler-Nordheim Tunneling (MFN) | 8  |

|   |       |         | 2.2.1.4 Trap Assisted Tunneling (TAT)            | 8  |

|   |       | 2.2.2   | Hot carrier injection (HCI)                      | 8  |

|   | 2.3   | Erasin  | g                                                | 10 |

|   | 2.4   | Issues  | with SONOS                                       | 10 |

|   | 2.5   | Silicon | nitride by LPCVD - Literature review             | 11 |

|   |       | 2.5.1   | Silicon nitride in semiconductor industry        | 12 |

|   |       | 2.5.2   | Silicon nitride in memory                        | 14 |

|   | 2.6   | Natur   | of the traps in silicon nitride                  | 15 |

|   |       | 2.6.1   | Amphoteric Trap model                            | 15 |

|   |       | 2.6.2   | Trap distribution                                | 15 |

|   | 2.7   | Trap o  | naracterization methods - Literature review      | 18 |

| 3 | Silio | con nit | ride process optimization and Results            | 20 |

|   | 3.1   | Exper   | ments                                            | 20 |

|   |       | 3.1.1   | Results of initial experiments                   | 21 |

|   |       | 3.1.2   | Solutions to reduce non-uniformity               | 2: |

|   | 3.2 | Effect of $N_2$ dilution                                          | 25 |

|---|-----|-------------------------------------------------------------------|----|

|   | 3.3 | Change in $SiH_4$ flow                                            | 26 |

|   | 3.4 | Effect of pressure                                                | 28 |

|   | 3.5 | Effect of deposition temperature                                  | 28 |

| 4 | SOI | NOS device fabrication and measurements                           | 30 |

|   | 4.1 | Development of thin films for SONOS flash memory gate stack       | 30 |

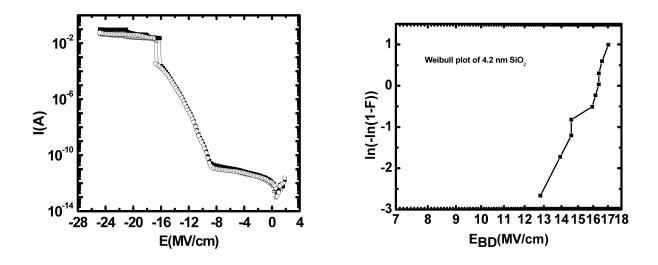

|   |     | 4.1.1 Tunnel oxide                                                | 30 |

|   |     | 4.1.2 Blocking oxide                                              | 31 |

|   |     | 4.1.3 N-poly gate                                                 | 32 |

|   | 4.2 | SONOS structure fabrication and Characterization                  | 33 |

|   |     | 4.2.1 SONOS capacitor process flow                                | 34 |

|   |     | 4.2.2 SONOS memory stack characterization                         | 35 |

| 5 | Tra | p characterization methods of MNS devices                         | 37 |

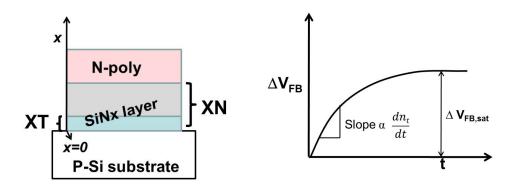

|   | 5.1 | Trap density                                                      | 37 |

|   | 5.2 | Trap capture cross section                                        | 38 |

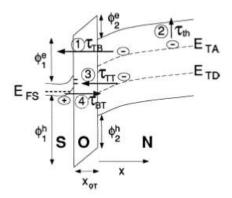

|   | 5.3 | Retention Model for trap level extraction                         | 40 |

| 6 | Ext | raction of trap parameters and Results                            | 43 |

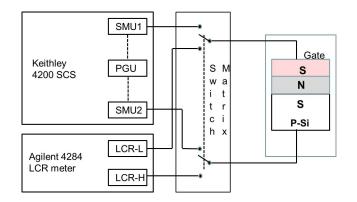

|   | 6.1 | Electrical Characterization Setup                                 | 43 |

|   | 6.2 | Results                                                           | 44 |

|   |     | 6.2.1 SiN <sub>x</sub> film thickness and RI data                 | 44 |

|   |     | 6.2.2 Electrical characterization                                 | 44 |

|   | 6.3 | Trap Characterization Measurements                                | 45 |

|   |     | 6.3.1 Trap Density from Programming Transients                    | 46 |

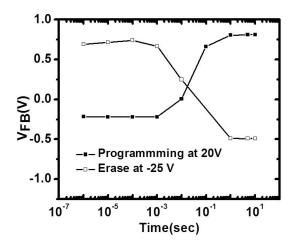

|   |     | 6.3.1.1 C-V characteristics with program and erase                | 47 |

|   |     | 6.3.2 Trap capture cross section                                  | 49 |

|   |     | 6.3.3 Retention measurements for extracting the trap energy level | 50 |

|   | 6.4 | Discussion                                                        | 51 |

| 7 | Cor | aclusions and Future Work                                         | 57 |

|   | COL | crusions and ruture work                                          | •  |

|   | 7.1 | Conclusions                                                       | 57 |

| Rε | efere | aces                             | 58 |

|----|-------|----------------------------------|----|

| A  | Pro   | cess recipes                     | 63 |

|    | A.1   | Tunnel oxide                     | 63 |

|    | A.2   | Silicon nitride                  | 64 |

|    | A.3   | Low temperature oxide (LTO)      | 65 |

|    | A.4   | n-doped poly Si                  | 65 |

|    | A.5   | Dopant activation anneal         | 65 |

|    | A.6   | Front side etching - Dry etching | 65 |

|    | A.7   | Back side n-poly Si etch         | 66 |

|    | A.8   | Back side ONO stack etch         | 66 |

|    | A.9   | Back side Al contact             | 66 |

|    | A.10  | Forming gas anneal               | 66 |

# List of Figures

| 1.1  | Floating Gate flash                                                                                 | 2  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 1.2  | Percolation path in thin and thick tunnel oxides [2]                                                | 2  |

| 2.1  | Evolution of SONOS NVSM device [6]                                                                  | 5  |

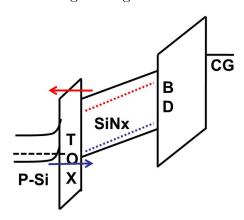

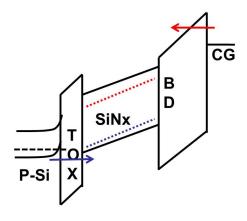

| 2.2  | The SONOS memory transistor                                                                         | 6  |

| 2.3  | I-V characteristics of tunnel oxide for memory [8]                                                  | 6  |

| 2.4  | Band diagram during Direct tunneling                                                                | 7  |

| 2.5  | Fowler-Nordheim tunneling                                                                           | 8  |

| 2.6  | Modified Fowler-Nordheim tunneling                                                                  | 8  |

| 2.7  | Trap assisted tunneling                                                                             | 9  |

| 2.8  | (a) Channel hot electron injection (b) Band diagram during CHEI                                     | 9  |

| 2.9  | Erasing in SONOS                                                                                    | 10 |

| 2.10 | Band diagram of SONOS device with standard nitride [9]                                              | 11 |

| 2.11 | Erase saturation                                                                                    | 12 |

| 2.12 | Trap distribution model by Ross and Wallmark [13]                                                   | 16 |

| 2.13 | Energetical trap distribution model by Dorda and Pulver [14]                                        | 16 |

| 2.14 | Spatial and Energetical trap distribution model by Ferris-prabhu [15]                               | 17 |

| 2.15 | Simple trap distribution model by White and Cricchi [16]                                            | 17 |

| 2.16 | Currents in n-channel SONOS device (a) Programming (b) Erasing [17]                                 | 18 |

| 3.1  | Typical three Zone LPCVD reactor                                                                    | 21 |

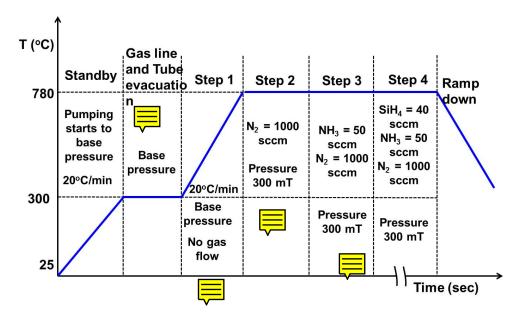

| 3.2  | Temperature vs time of a example recipe (not to scale). Standby temperature is                      |    |

|      | $300^o\mathrm{C},\mathrm{process}$ temperature is 780°C and pressure is 300 mTorr. Base pressure is |    |

|      | < 0.005 Torr                                                                                        | 22 |

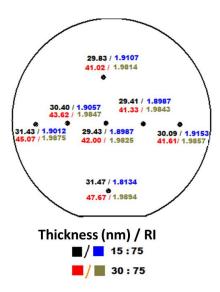

| 3.3  | Thickness nonuniformity in two cases (a) SiH <sub>4</sub> - 15 sccm, NH <sub>3</sub> -150 sccm at $780^{o}$ C                                   |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and 300 mTorr (for two wafers). (b) SiH <sub>4</sub> - 15 sccm, NH <sub>3</sub> -225 sccm at $780^{o}$ C and                                    |    |

|      | 300 mTorr (measured in the center part of the wafer map in (a))                                                                                 | 23 |

| 3.4  | (a) Bull's eye effect, SiH <sub>4</sub> - 30 sccm, NH <sub>3</sub> -75 sccm at $780^{o}$ C and 300 mTorr. (b)                                   |    |

|      | Ring formation along the wafer circumference, $SiH_4$ - 15 sccm, $NH_3$ -45 sccm at                                                             |    |

|      | 780°C and 300 mTorr                                                                                                                             | 23 |

| 3.5  | Thickness variations after dummy wafers used during deposition for two recipes.                                                                 |    |

|      | $SiH_4{:}NH_3$ are 15:75 sccm and 30:75 sccm respectively at $780^{o}\mathrm{C}$ and 300 mTorr                                                  | 24 |

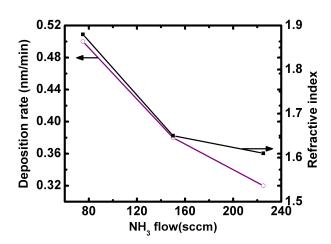

| 3.6  | Deposition rate and refractive index with change in $\mathrm{NH_{3}}$ flow. $\mathrm{SiH_{4}}$ - 15 sccm,                                       |    |

|      | Temperature - 780°C and Pressure - 300 mTorr                                                                                                    | 24 |

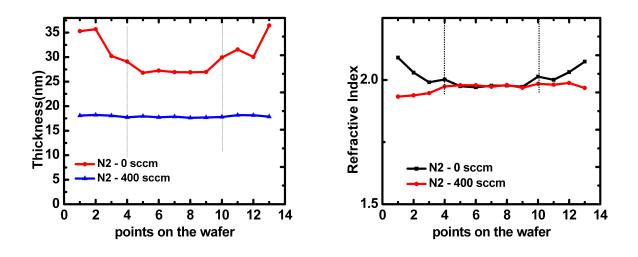

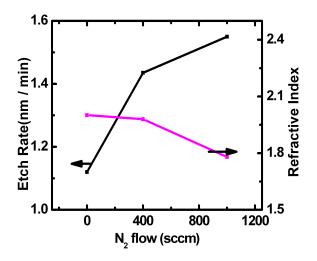

| 3.7  | Effect of $N_2$ dilution on (a) thickness (b) refractive index. $SiH_4:NH_3$ - $40:50$ sccm,                                                    |    |

|      | 780°C, 300 mTorr and 20 min                                                                                                                     | 25 |

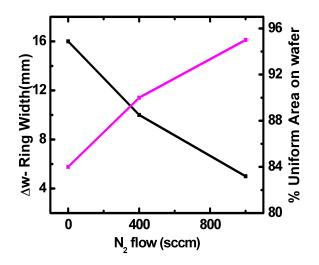

| 3.8  | Wafer map showing the measurement points on 4-inch wafer by ellipsometer                                                                        | 25 |

| 3.9  | Ring width vs $N_2$ flow. SiH <sub>4</sub> :NH <sub>3</sub> - 40:50 sccm, 780°C, 300 mTorr and 20 min                                           | 26 |

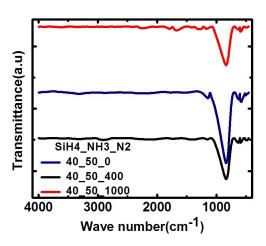

| 3.10 | FTIR measurements on as-deposited $\mathrm{SiN}_x$ films. The legend in the figure indicates                                                    |    |

|      | gas flow in sccm. Temperature-780°C, pressure-300 mTorr and deposition time-20                                                                  |    |

|      | min                                                                                                                                             | 26 |

| 3.11 | Etch rate in 5:1 HF with different $N_2$ flow. $SiH_4:NH_3$ - $40:50$ sccm, $780^{o}C$ , $300$                                                  |    |

|      | mTorr and 20 min                                                                                                                                | 27 |

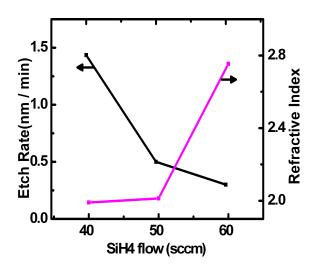

| 3.12 | Etch rate in 5:1 HF with different SiH $_4$ flow. SiH $_4$ :N $_2$ ratio is 1:10, NH $_3$ - 50 sccm,                                            |    |

|      | 780°C, 300 mTorr and 20 min                                                                                                                     | 27 |

| 3.13 | Effect of SiH <sub>4</sub> flow on thickness. SiH <sub>4</sub> :N <sub>2</sub> ratio is 1:10, NH <sub>3</sub> - 50 sccm, $780^{\circ}$ C, $300$ |    |

|      | mTorr and 20 min                                                                                                                                | 27 |

| 3.14 | Effect of deposition pressure. SiH <sub>4</sub> :NH <sub>3</sub> :N <sub>2</sub> - 40:50:400 sccm, 780°C, 300 mTorr                             |    |

|      | and 20 min                                                                                                                                      | 27 |

| 3.15 | Effect of deposition temperature and dilution on (a) thickness (b) refractive index.                                                            |    |

|      | Numbers in the figure indicates temperature (°C) - SiH <sub>4</sub> flow (sccm) - NH <sub>3</sub> flow                                          |    |

|      | (sccm) - $N_2$ flow (sccm) - deposition time (minutes)                                                                                          | 28 |

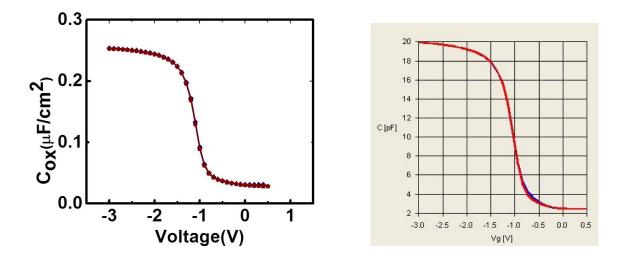

| 4.1  | (a) C-V characteristics and (b) Hauser fit of the C-V of 4.2 nm tunnel oxide                                                                    | 31 |

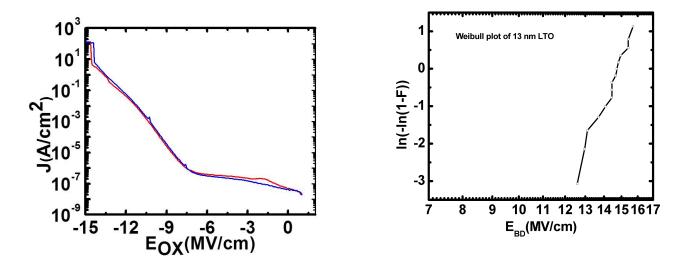

| 4.2  | (a) I-E characteristics and (b) Weibull distribution plot of 4.2 nm tunnel oxide                                                                | 32 |

| 4.3  | (a) C-V characteristics and (b) Hauser fit of the C-V of 13.5 nm LTO after an-                                                                  |    |

|      | nealing at $850^{\circ}$ C in N <sub>2</sub>                                                                                                    | 32 |

| 4.4 | (a) 3-E characteristics and (b) werbuil distribution plot of 13 min E1O                                                                 | 99 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

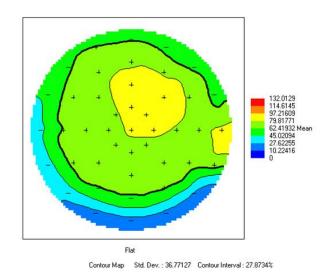

| 4.5 | Sheet resistance map of n-poly film deposited at $630^{0}\mathrm{C}$ with SiH <sub>4</sub> :PH <sub>3</sub> :N <sub>2</sub> - 90:20:210 |    |

|     | sccm and 300 mTorr for 4500 seconds                                                                                                     | 33 |

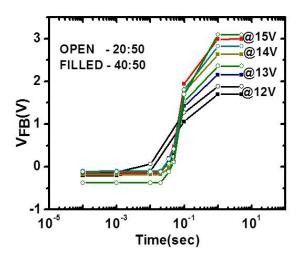

| 4.6 | Programming transients                                                                                                                  | 35 |

| 4.7 | P/E transients with improved blocking oxide                                                                                             | 35 |

| 5.1 | (a) Schematic of SNS structure for trap density calculation (b) $V_{FB}$ vs time during                                                 |    |

|     | charge trapping                                                                                                                         | 37 |

| 5.2 | Charge loss mechanisms in SONOS device [23]                                                                                             | 40 |

| 6.1 | Characterization setup for for C-V, I-V, P/E and retention measurements                                                                 | 44 |

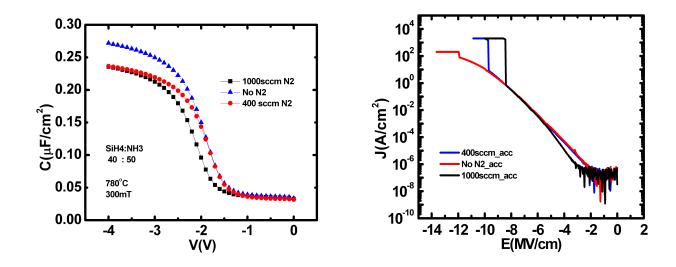

| 6.2 | (a) C-V characteristics and (b) J-E characteristics of SNS devices with different                                                       |    |

|     | $N_2$ flow. The device area is 5.02E-5 cm <sup>2</sup>                                                                                  | 45 |

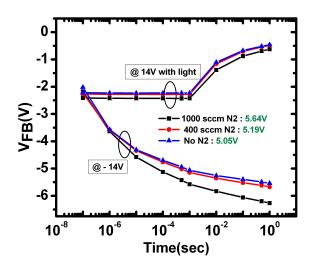

| 6.3 | Program transients of devices D1,D2 and D3                                                                                              | 46 |

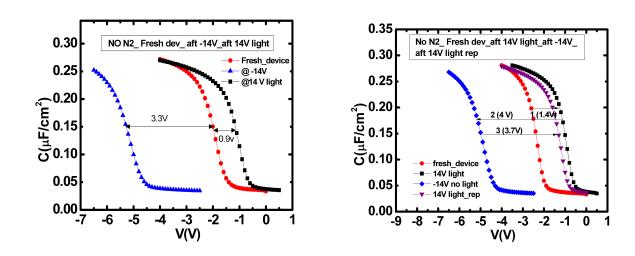

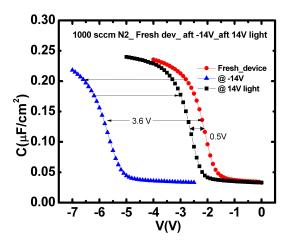

| 6.4 | C-V characteristics of D1 (a) Fresh device - after stressing with -14 V - after                                                         |    |

|     | stressing with $+14~\mathrm{V}$ and light ON. (b) Fresh device - after stressing with $+14~\mathrm{V}$                                  |    |

|     | and light ON - after stressing with -14 V -after stressing with +14 V and light ON.                                                     | 48 |

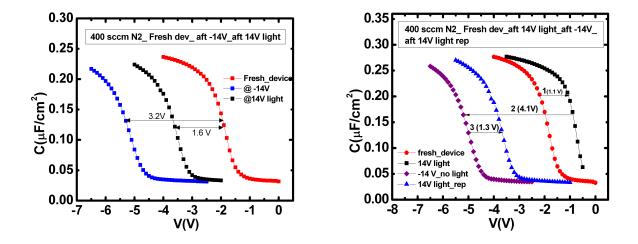

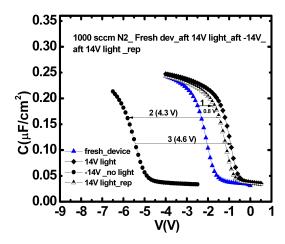

| 6.5 | C-V characteristics of D2 (a) Fresh device - after stressing with -14 V - after                                                         |    |

|     | stressing with $+14~\mathrm{V}$ and light ON. (b) Fresh device - after stressing with $+14~\mathrm{V}$                                  |    |

|     | and light ON - after stressing with -14 V -after stressing with +14 V and light ON.                                                     | 48 |

| 6.6 | C-V characteristics of D3 (a) Fresh device - after stressing with -14 V - after                                                         |    |

|     | stressing with $+14~\mathrm{V}$ and light ON. (b) Fresh device - after stressing with $+14~\mathrm{V}$                                  |    |

|     | and light ON - after stressing with -14 V -after stressing with +14 V and light ON.                                                     | 49 |

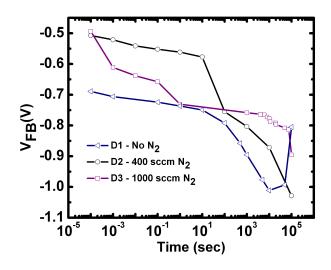

| 6.7 | Retention measurement on devices D1,D2 and D3 showing $V_{FB}$ vs time. The                                                             |    |

|     | devices are programmed for 1 s                                                                                                          | 50 |

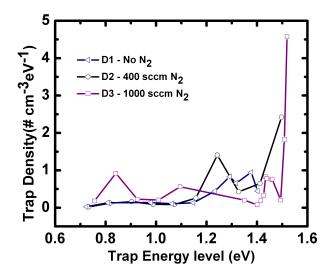

| 6.8 | Electron trap distribution in devices D1,D2 and D3                                                                                      | 50 |

## List of Tables

| 2.1 | Charge injection mechanisms                                                                                         | 10 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Trap distribution and memory performance                                                                            | 15 |

| 4.1 | Tunnel oxide parameters extracted from C-V by using hauser fit. Process condi-                                      |    |

|     | tions: T - 800°C,<br>O2 - 5000 sccm, time - 10 minutes and annealed at 900°C for 5                                  |    |

|     | minutes in $N_2$ ambient                                                                                            | 31 |

| 4.2 | Blocking oxide parameters extracted from C-V by using hauser fit. Process con-                                      |    |

|     | ditions: SiH <sub>4</sub> :O <sub>2</sub> - 40:100 sccm, N <sub>2</sub> - 500 sccm, temperature - 430°C, pressure - |    |

|     | 150 mTorr, Time - 5 minutes                                                                                         | 31 |

| 4.3 | SONOS device details                                                                                                | 34 |

| 6.1 | Thickness and RI data of the $SiN_x$ films deposited at 780°C, 300 mTorr and with                                   |    |

|     | different $N_2$ flow. $SiH_4$ -40 sccm and $NH_3$ -50 sccm                                                          | 44 |

| 6.2 | $\Delta V_{FB}$ values of samples D1,D2 and D3 with ±14 V programming                                               | 46 |

| 6.3 | Calculated trap density values from program transients                                                              | 47 |

| 6.4 | Current density values of D1,D2 and D3 in accumulation and inversion at 14 V $$ .                                   | 50 |

| 6.5 | Hole and Electron trap capture cross sections                                                                       | 50 |

| A.1 | Process recipe for 4 nm tunnel oxide                                                                                | 67 |

| A.2 | Process recipe for Silicon nitride                                                                                  | 68 |

| A.3 | Process recipe for LTO                                                                                              | 69 |

| A.4 | Process recipe for n-doped poly Si                                                                                  | 70 |

## List of Abbreviations

BD Blocking Dielectric

CHE Channel Hot Electron

CHEI Channel Hot Electron Injection

CMOS Complementary Metal Oxide Semiconductor

CTF Charge Trap Flash

C-V Capacitance - Voltage

DCS Di-chloro silane

DCTS Discharge Current Transient Spectroscopy

DT Direct Tunneling

EOT Equivalent Oxide Thickness

FG Floating Gate

FN Fowler - Nordheim

FTIR Fourier Transform Infrared spectroscopy

GCR Gate Coupling Ratio

HF Hydro Flouric Acid

HNA HF/Nitric acid/Acetic acid

ITRS International Technology Road map for Semiconductor industry

LPCVD Low Pressure Chemical vapor Deposition

LTO Low temperature Oxide

MFN Modified FN

MNS Metal/Silicon nitride/Silicon

MNOS Metal/Silicon nitride/Oxide/Silicon

MOS Metal/Oxide/Silicon

NC Nano Crystal

ONO Oxide/Silicon nitride/Oxide

P/E Program/Erase

p-Si p- type Silicon

RBS Rutherford Back Scattering

RI Refractive Index

RIE Reactive Ion Etching

RTP Rapid Thermal Processing

SNOS poly Silicon/Silicon nitride/Oxide/Silicon

SNS poly Silicon/Silicon nitride/Silicon

$SONOS \qquad poly \ Silicon/Oxide/Silicon \ nitride/Oxide/Silicon$

TAT Trap Assisted Tunneling

TOX Tunnel Oxide

XPS X-ray Photoelectron Spectroscopy

## Constants

Electron charge  $q = 1.602 \times 10^{-19} \text{ C}$

Free electron mass  $m_0 = 9 \times 10^{-35}$  g.J/erg

Boltzmann's constant  $k_B=1.38{\times}10^{-23}~\mathrm{J/K}$

Planck's constant  $h = 6.62 \times 10^{-34} \text{ J.s}$

Permittivity of free space  $\epsilon_0 = 8.854 \times 10^{-14} \text{ F/cm}$

## List of symbols

$X_{OX}$  Thickness of oxide (nm)

$X_N$  Silicon nitride thickness (nm)

$X_T$  Thickness of the charge trapped region in Silicon nitride (nm)

$\phi_{OX}$  Barrier height at Si-SiO<sub>2</sub> interface w.r.t Si conduction band (eV)

$\phi_N$  Barrier height at SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub> interface (eV)

$\phi_t$  Energy level of the trap in silicon nitride (eV)

$E_{OX}$  Electric field in the oxide (MV/cm)

$E_N$  Electric field in silicon nitride (MV/cm)

$\epsilon_{OX}$  Dielectric constant of SiO<sub>2</sub>

$\epsilon_N$  Dielectric constant of silicon nitride

$\rho$  Spatial charge density (C/cm<sup>3</sup>)

$\sigma_t$  Trap capture cross section (cm<sup>2</sup>)

$\vartheta_d$  Drift velocity of the carriers in silicon nitride (cm/s)

$\xi$  Total emission rate from traps (#/s)

J Current density in the silicon nitride  $(A/cm^2)$

$E_{TA}$  Trap energy level (eV)

$g(E_{TA})$  Density function of traps (# cm<sup>3</sup>eV<sup>-1</sup>)

$C_N$  Capacitance of MNS/SNS structure (F/cm<sup>2</sup>)

$N_t$  Total number of traps (#/cm<sup>3</sup>)

$n_t$  Number of filled traps (#/cm<sup>3</sup>)

$n_c$  Number of available carriers for trapping (#/cm<sup>3</sup>)

$V_G$  Gate voltage

$V_{FB}$  Flat-band voltage

$\Delta V_{FB}$  Change in flat-band voltage

$\Delta Q_P$  Change in positive trapped charge

$\Delta Q_N$  Change in negative trapped charge

$V_{TH}$  Threshold voltage

$\Delta V_{TH}$  Change in threshold voltage

## Chapter 1

## Introduction

Non volatile semiconductor flash memory market is one of the driving forces of the present semiconductor industry. This storage technology simply consists of storing a few electrons surrounded by a dielectric well with the application of suitable voltage. Though the concept looks simple, producing reliable and high density memories is a challenging task. Floating gate flash is a mature technology in the semiconductor memory area that has been well understood and demonstrated from 0.8  $\mu$ m to 45 nm technology nodes. The requirement of high density data storage in portable storage drives enables continuous floating gate (FG) flash scaling up to 32 nm node, but it may not be possible for further scaling.

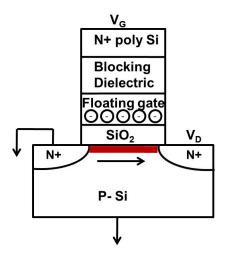

Floating gate device stores charge in a polysilicon floating gate that is surrounded by insulators from all sides. The floating gate is thicker than both tunnel oxide and blocking dielectric. The floating gate device is similar to that of standard MOSFET except the gate stack. In standard MOSFET the gate stack consists of single oxide layer followed by poly-Si/metal gate whereas in floating gate devices the gate stack is made up of Tunnel Oxide/Poly-Si FG/Blocking Oxide/poly or metal gate (Figure 1.1).

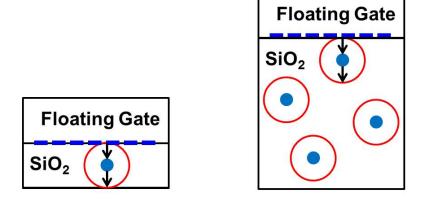

The performance of the FG flash memory depends on the thickness of the layers used in the gate stack. Thick tunnel oxide is good for long term retention but higher programming and erase voltages are not compatible with the present CMOS technology. To be consistent with the scaling trend tunnel oxide thickness must be reduced below 4 nm. It is very difficult to grow such good quality thin tunnel oxides without any pin hole defects. Since the electrons stored in conductive floating gate, any single pin hole defect can cause tunneling of electrons back to substrate through Poole-Frenkel mechanism. The tunnel oxide must be thick enough to prevent charge tunneling through percolation path for long term retention. Defects in the oxide are created by electrical stress during P/E cycles. The defect formation continues until a chain of defects is formed called

Figure 1.1: Floating Gate flash.

percolation path. The red circle in Fig. 1.2 shows the characteristic length of the electron while tunneling and the blue dot represents the defect in oxide [2]. If the thickness of the tunnel oxide is comparable to tunneling characteristic length of the electron (as is the case with Ultra Thin Tunnel oxides), a single defect can leak the charge through Poole-Frenkel conduction, whereas this is not a problem with thicker oxides.

Figure 1.2: Percolation path in thin and thick tunnel oxides [2].

As per ITRS 2009, the tunnel oxide thickness for floating gate flash memory is 6-7 nm (up to 32 nm node) and the P/E voltages are 17-19 V and 15-17 V for 45 nm and 32 nm technology nodes respectively [1]. Tunnel oxide with thickness >8 nm can be relatively leak free because a single defect in the oxide is insufficient to provide a leakage path, but oxides with thickness less than 8 nm are vulnerable to leakage through defects. This limits the scaling of floating gate technology in vertical direction. Also higher P/E voltages causes reliability problems such as stress induced leakage currents and hot carrier degradation.

Gate coupling ratio (GCR) is another concern with the floating gate devices with respect

to scaling. The GCR indicates the amount of control by the control gate over channel. GCR is defined as C (control gate to floating gate capacitance)/C (total floating gate capacitance). The GCR must be >0.60 for the control gate to be effective. But the scaling limitation on the blocking oxide to reduce leakage does not permit to achieve GCR > 0.5 [2]. To achieve high GCR, floating gate is wrapped around by the control gate in the width direction. With continuous scaling there is no space left for the control gate to wrap around the floating gate after the blocking dielectric filling. This limits the scaling in lateral direction.

Another problem in FG flash is inter-cell interference. As the scaling continues, cell to cell interference increases due to the physical proximity of the devices. To reduce inter-cell interference with continuous scaling the floating gate must be thin. But recent results demonstrated that there is a limit to thinning of the floating gate up to  $\sim 10$  nm below which further thinning is not possible. This is due to the ballistic transport of those electrons which are not scattered in the thin poly floating gate during programming [3]. These ballistic currents in scaled floating gate devices causes reliability problems, reduces P/E speeds and limits the FG scaling. Overall further scaling of FG flash does not seem to be effective and alternative technologies must be considered to drive the scaling of the semiconductor non-volatile memory.

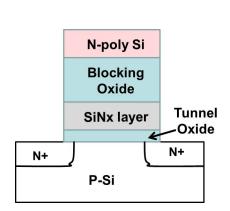

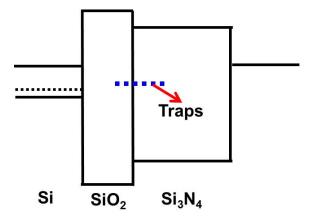

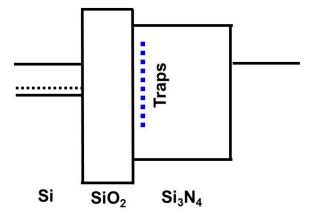

The main issue with FG flash is the charge storage in a conductive poly-Si layer which is continuous. If the charge storage is discrete in nature then the fundamental problem of scaling the tunnel oxide can be solved (to the extent that direct tunneling limits the retention). Charge Trap Flash (CTF) is the best alternative to the floating gate flash in which charge is stored in the discrete form. Two types of CTF technologies are under research. One is SONOS (Si/Oxide/Nitride/Oxide/Poly-Si) technology in which the charge is stored in the traps in the nitride<sup>0</sup> layer. The other CTF technology is the Nanocrystal (NC) memory in which the storage node is either Si or metal nanocrystals. The nanocrystal memory has its own problems such as poor programming efficiency due to smaller density and area coverage, poor size distribution etc.

The main motivation for SONOS technology is that it allows scaling in both directions and can be operated with lower P/E voltages compatible with the CMOS technology. Also the SONOS technology is immune to radiation (radiation hard) and can be used in space applications.

The main focus of this work is to develop thin silicon nitride films for the application of charge trap layer in SONOS flash memories. LPCVD is the best method for depositing such memory quality nitride films. The performance of memory stack depends on the composition of charge trap layer. Si dangling bonds act as the trap centers which are responsible for memory

<sup>&</sup>lt;sup>0</sup>Here nitride means Silicon nitride. The same convention is followed elsewhere in this report.

action [4]. Si-rich nitride is needed for faster programming where as for long term retention the traps in the nitride should be deep [23]. Therefore proper (spatial and energetic) distribution of traps is very important and this depends on the processing conditions. The deposition conditions should be free from oxygen and hydrogen impurities as well as metallic impurities. The metallic impurities cause charge loss whereas the O and H atoms reduce the trap density [4].

In this work, development of good quality uniform silicon nitride films from SiH<sub>4</sub>-NH<sub>3</sub>-N<sub>2</sub> system with varying stoichiometry and thickness is presented. The memory properties of asdeposited films were investigated and trap parameters are extracted.

### 1.1 Organization of the Report

- 1. Chapter 1 The present chapter served as introduction.

- 2. Chapter 2 Literature review, describes the basic principles of SONOS technology and nature of traps.

- 3. Chapter 3 Silicon nitride process optimization, issues and results.

- 4. Chapter 4 SONOS device fabrication and P/E measurements.

- 5. Chapter 5 Trap density analysis and trap characterization methods.

- 6. Chapter 6 Trap characterization experiments, results and discussion.

- 7. Chapter 7 Conclusion and Future work to be done.

## Chapter 2

## Literature Review

#### 2.1 Evolution of SONOS memory

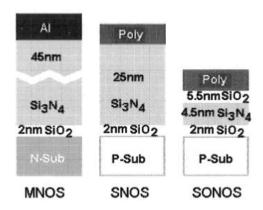

Early charge trapping devices in 1960s were MNOS (Metal/Nitride/Oxide/Si) type. The first MNOS device was a p-channel device with thick silicon nitride (~45 nm) as charge trap layer and thin tunnel oxide (2 nm). The gate was Al metal gate (Figure 2.1). Because of thicker charge trap layer, the programming and erasing voltages were relatively high (~30 V). These memory devices suffered from low speed and less density.

Figure 2.1: Evolution of SONOS NVSM device [6].

With the advent of LPCVD, researchers started depositing high quality silicon nitride and poly silicon films. Slowly the MNOS device transformed into SNOS (Poly-Si/Nitride/Oxide/Si) device with thinner dielectric layers. The nitride layer was reduced to 25 nm whereas the tunnel oxide was 2 nm. This resulted in lower programming and erase voltages compared to MNOS devices. Programming and erasing of these devices were done by Fowler-Nordheim tunneling. Later many researchers proposed scaled SNOS devices in which the nitride layer was scaled to 20 nm and the tunnel oxide of 1.6 nm with a low programming voltage of 10 V. The main problem

with the scaled SNOS devices was hole injection from the gate that limits the memory window.

The charge injection from gate can be reduced by sandwiching an oxide layer between the poly-Si gate and nitride layer [7]. This idea led to the present form of SONOS transistor. The advantages of triple dielectric structure are:

- Reduced programming voltages due to reduction in nitride thickness

- Because of the top oxide, charge injection from and to the gate electrode is minimized.

- Since there is minimal loss of charge through the gate, the memory window is improved.

The SONOS device is triple dielectric device in which a silicon nitride layer is sandwiched between two oxide layers as shown in Fig. 2.2. Charge storage takes place in the traps distributed in the nitride layer. The bottom oxide called as tunnel oxide permits the charge transfer from silicon substrate to the charge trap layer through quantum mechanical tunneling.

Retention Program/Erase

Steeper slope improves program and erase efficiency

SILC degrades retention

Tunnel Oxide Field

Figure 2.2: The SONOS memory transistor.

Figure 2.3: I-V characteristics of tunnel oxide for memory [8].

The thickness of the tunnel oxide decides the programming efficiency and retention characteristics. Figure 2.3 shows the requirements of the tunnel oxide in the memory devices. Leakage at low fields should be very less to improve the retention whereas higher tunneling currents are needed at moderate fields for faster and low voltage programming.

The top oxide layer between poly-Si gate and charge trap layer is called as blocking oxide. As the name indicates its function is to block the charge transfer to and from the gate. The blocking oxide thickness is decided in such a way that it should not allow any charge injection from the gate.

### 2.2 SONOS charge injection mechanisms

The charge injection mechanisms in SONOS devices are broadly classified into two categories:

- Tunneling based charge injection and

- Hot carrier injection

The type of charge injection depends on how the SONOS device is connected in memory configuration, either NAND or NOR.

#### 2.2.1 Tunneling based charge injection

This type of charge injection is based on the quantum mechanical tunneling of carriers through oxide. In these mechanisms the required voltage is applied between the gate and substrate of the memory transistor. SONOS devices in NAND configuration use tunneling based charge injection. The different tunneling mechanisms are:

- 1. Direct band to band tunneling (DT)

- 2. Fowler-Nordheim tunneling (FN)

- 3. Modified Fowler-Nordheim tunneling (MFN)

- 4. Trap Assisted Tunneling (TAT)

The type of tunneling depends on the thickness of the dielectric layers and applied field.

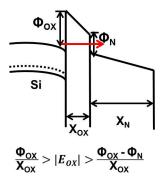

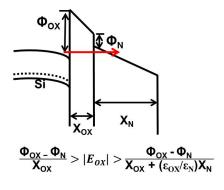

#### 2.2.1.1 Direct band to band tunneling (DT)

In this mechanism, the carriers tunnel from the silicon conduction band to nitride traps through the oxide directly. The band diagram for this type of tunneling is shown in Fig. 2.4. Direct tunneling depends on the thickness of the oxide and occurs when the fields are not very high. In the SONOS devices with ultra-thin oxides (< 3 nm), the dominant injection mechanism is Direct tunneling.

Figure 2.4: Band diagram during Direct tunneling.

#### 2.2.1.2 Fowler-Nordheim Tunneling (FN)

This is the most prominent charge injection mechanism in flash memory devices. In fact this is field assisted tunneling. Under the application of large electric fields ( $\sim 10 \text{ MV/cm}$ ), the electrons in the silicon conduction band see a triangular energy barrier whose width depends on the applied field. The width of the barrier becomes so thin that electrons in the silicon conduction band tunnel through the barrier (Figure 2.5). Since the effective barrier width is reduced, the FN tunneling currents are higher than DT currents.

Figure 2.5: Fowler-Nordheim tunneling.

Figure 2.6: Modified Fowler-Nordheim tunneling.

#### 2.2.1.3 Modified Fowler-Nordheim Tunneling (MFN)

In this mechanism, the carriers first tunnel through the oxide directly into the nitride band gap and then through FN tunneling to the nitride conduction band (Figure 2.6). This depends on the barrier height and the barrier height on the nitride side should be less than the barrier on gate or substrate.

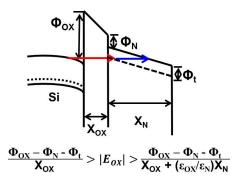

#### 2.2.1.4 Trap Assisted Tunneling (TAT)

This is similar to MFN. In this case the carriers are captured by the traps in nitride close to nitride conduction band by direct tunneling. Then the trapped carriers tunnel from the traps to the conduction band (Figure 2.7). Since the trap is closer than the conduction band edge in the tunneling path, TAT currents are higher compared to that of MFN.

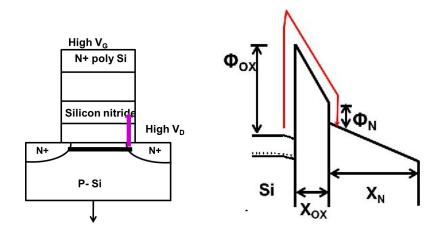

#### 2.2.2 Hot carrier injection (HCI)

In tunneling based charge injection mechanisms the electric field in the channel is constant and depends on the voltage applied between gate and substrate. Whereas in hot carrier injection, voltage is applied to both gate and drain terminals such that the carriers in the channel see a

Figure 2.7: Trap assisted tunneling.

gradual increase in lateral electric field towards drain and becomes energetic (Figure 2.8). Those 'hot'energetic carriers that are having sufficient energy to cross the oxide barrier will be trapped in the nitride. For the SONOS devices made on p-Si substrate, Channel hot electron (CHE) injection is the hot carrier injection mechanism. SONOS devices in NOR configuration use HCI technique for programming.

Figure 2.8: (a) Channel hot electron injection (b) Band diagram during CHEI.

With the tunneling mechanisms used for programming, the charge distribution in the nitride layer is uniform whereas with CHE programming the charge is localized near drain. The trapping efficiency is better in the tunneling charge injection compared to hot carrier injection. Since, the carriers are accelerated by lateral field, programming time with HCI is small. Also, CHE programming needs higher voltages and results in higher charge pump voltages. Table 2.1 summarizes the charge trapping mechanisms.

<sup>&</sup>lt;sup>1</sup>Since the electrons overcome the barrier at Si-SiO<sub>2</sub> interface, CHEI can be used with the oxides of any thickness. But the thickness decided by leakage during retention (Section 2.1).

<sup>&</sup>lt;sup>2</sup>Both vertical and lateral fields are needed for carrier injection. Lateral field ensures that carriers get enough energy, vertical field favors the charge injection.

| Injection Mechanism | Tunnel oxide thickness   Electric Field |                                    |

|---------------------|-----------------------------------------|------------------------------------|

| FN Tunneling        | Thick (~5nm)                            | Very High (10MV/cm)                |

| Direct Tunneling    | Thin (< 3nm)                            | High $(6-7 \text{ MV/cm})$         |

| MFN Tunneling       | Thin                                    | Medium                             |

| TAT                 | Thin                                    | Low                                |

| CHE Injection       | Any <sup>1</sup>                        | depends on the channel length $^2$ |

Table 2.1: Charge injection mechanisms

#### 2.3 Erasing

The stored charge in a SONOS device is removed by tunneling in both configurations NAND and NOR. By applying a voltage of opposite polarity (to that of programming) between gate and substrate, the fields are opposite and the energy bands are in such a way that hole tunneling from substrate takes place. This neutralizes the electrons stored in the nitride layer. At the same time FN tunneling of electrons from nitride to Si conduction band also takes place. But the main component for erasing is the hole direct tunneling from Si valance band to nitride Fig. 2.9. Therefore, the thickness of tunnel oxide should be minimum for faster erase but this increases the chance of low field leakage during retention and memory window is reduced.

Figure 2.9: Erasing in SONOS.

#### 2.4 Issues with SONOS

The localized charge trapping nature of the SONOS devices allows further scaling and overcomes some of the disadvantages of floating gate technology. It allows higher density due to reduced cell size in both directions, lower programming and erasing voltages, excellent scalability, compatibility with existing CMOS process technology and superior resistance to radiation. In spite of many advantages there are some issues with SONOS technology such as poor trapping efficiency, short retention times and erase saturation. These problems slowed down the growth of the SONOS

technology and needs to be resolved before replacing the existing floating gate technology.

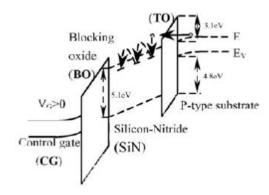

Because of smaller barrier heights between nitride and surrounding oxides ( $\sim 1.3$  eV) (Figure 2.10) the trapped charges in the nitride escape easily and leads to poor trapping efficiency [9]. If the traps are located at deeper energy levels, this small barrier height is not an issue but in silicon nitride the traps are distributed every where. Therefore, the electrons trapped in those shallow traps distributed near the band edge can escape easily.

Figure 2.10: Band diagram of SONOS device with standard nitride [9].

The deep trap levels in the standard nitride is another concern for the SONOS memories. Detrapping is very slow and high gate voltages (i.e, High electric fields) are not much helpful to detrap the electrons from these deep traps. Moreover injection from the gate is a problem at high gate voltages. One solution to this is to use ultra thin oxides which allow hole tunneling from the substrate. But with ultra thin oxides low field leakage is a problem and this leads to retention loss even at room temperature thus reduces memory window. If thicker oxides are to be used to reduce low field leakage then erase speed will be reduced. Thus there is a trade-off between retention and erase speed [10].

Another problem with SONOS is the erase saturation. During erasing by FN tunneling, electron injection from gate (through FN tunneling) is faster than hole tunneling from the substrate to nitride layer. This is shown in Fig. 2.11. The memory device is not completely erased and the threshold voltage is clamped at single value. The solution to this problem is to use p-poly gate instead of n-poly gate or use high work function metal gate such as TaN [11].

### 2.5 Silicon nitride by LPCVD - Literature review

This section highlights some of the research done on silicon nitride from LPCVD. The main sources of Si reacting species in LPCVD silicon nitride are either chlorosilanes (SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>)

Figure 2.11: Erase saturation.

or monosilane (SiH<sub>4</sub>) and the nitrogen source is NH<sub>3</sub>. The other Si source under research is Si<sub>2</sub>H<sub>6</sub> (Disilane). The first LPCVD nitride was produced by SiH<sub>4</sub> and NH<sub>3</sub>. Very few research groups have experimented with SiH<sub>4</sub>-NH<sub>3</sub> system. Due to the non-uniformity issues the SiH<sub>4</sub>-NH<sub>3</sub> process was quickly abandoned. Majority research groups across the globe are currently using SiH<sub>2</sub>Cl<sub>2</sub>-NH<sub>3</sub> process.

#### 2.5.1 Silicon nitride in semiconductor industry

After the introduction of LPCVD in the semiconductor industry, synthesis of silicon nitride films by using LPCVD was first reported by R.S.Rosler et al., [29]. They first used SiH<sub>4</sub>, NH<sub>3</sub> gases with N<sub>2</sub> under different pressures and gas flows in a tubular hot wall reactor. The deposition temperature ranges from 780°C-850°C. The thicknesses obtained were in the range of 50 nm-200 nm and the refractive index from 1.98 to 2.02 for different gas flows and temperature profiles. They reported a large thickness non-uniformity of  $\pm 20\%$  within wafer. They observed the bull's eye effect of being much thicker deposition at the wafer edges compared to the center part of the wafer. With the modification of quartz boat they reported better within wafer uniformity of  $\pm 2$  to 5%. They also reported that the deposition rate and thickness uniformity were sensitive to wafer spacing. Etch rates (in 48% HF) of 1.2-1.5 nm/min were reported.

The same group reported the silicon nitride films from  $SiH_2Cl_2$  and  $NH_3$ . They mentioned that excellent uniformity of  $\pm 3.2\%$  has been obtained without any quartz modification. The refractive index obtained was 2 and the reported etch rates in 48% HF were 1.8-2.1 nm/min. They also have reported that the  $SiH_2Cl_2$ - $NH_3$  system is very insensitive to wafer spacing. This may be due to difference in diffusivity between  $SiH_2Cl_2$  and  $SiH_4$ .

Chramova et al., [43] deposited amorphous Si<sub>3</sub>N<sub>4</sub> films to study the oxidation effects of silicon nitride films. They used 2.5% SiH<sub>4</sub> (diluted in Ar) and NH<sub>3</sub> to deposit 100-300 nm thick films.

No details about thickness and compositional uniformity were mentioned. The IR measurement results indicate strong Si-N peak at  $900 \text{ cm}^{-1}$  -  $1200 \text{ cm}^{-1}$  and N-H peak at  $3000 \text{ cm}^{-1}$  -  $3500 \text{ cm}^{-1}$ .

The effect of change in precursor gas flow on the composition and structure of silicon nitride was reported by T.Makino [30] and correlated the refractive index with N/Si atomic ratio. The gas flow ratio ( $R = NH_3$  flow/  $SiH_2Cl_2$  flow) was varied from 0.1 to 10 and the deposition temperature was 770°C. The RBS measurements show that the silicon concentration increases with the decrease in R. As R increases the refractive index and etch rate in 49% HF decreases.

Popova et al., [31] reported the electrical characteristics (I-V and C-V measurements) on thin silicon nitride films deposited from SiH<sub>2</sub>Cl<sub>2</sub> and NH<sub>3</sub> at 800°C with 500 mTorr pressure. The deposition rate was around 6 nm/min with gas flow ratio (SiH<sub>2</sub>Cl<sub>2</sub>:NH<sub>3</sub>) of 1:3. They concluded, from the RBS measurements, that LPCVD process yields stoichiometric films. Their conduction model shows that both FN tunneling and Poole-Frenkel conduction are the dominant mechanisms.

Many researchers modeled the LPCVD silicon nitride process from SiH<sub>2</sub>Cl<sub>2</sub>-NH<sub>3</sub> ([32], [33], [34]). Carlos et al., [35] studied the thermophysical properties of low stress Si-rich silicon nitride films for sensor and actuator applications prepared from SiH<sub>2</sub>Cl<sub>2</sub>-NH<sub>3</sub>.

Schied et al., produced the silicon nitride films from Si<sub>2</sub>H<sub>6</sub> and NH<sub>3</sub> [20]. They compared all the three processes (SiH<sub>4</sub>-NH<sub>3</sub>, SiH<sub>2</sub>Cl<sub>2</sub>-NH<sub>3</sub> and Si<sub>2</sub>H<sub>6</sub>-NH<sub>3</sub>). The main advantage of Si<sub>2</sub>H<sub>6</sub> process is the low deposition temperature (600°C) compared to other processes. They also reported large non-uniformity in thickness in the silicon nitride films produced from the SiH<sub>4</sub>-NH<sub>3</sub> process compared to other two processes. As-deposited films from Si<sub>2</sub>H<sub>6</sub>-NH<sub>3</sub> show chemical resistance to buffer HF is comparable to that of standard nitride. They reported a breakdown field of 7 MV/cm for stoichiometric nitride (with RI of 2).

Liu et al., [36] reported silicon nitride films from SiH<sub>4</sub>-NH<sub>3</sub>-N<sub>2</sub> system with varying composition from stoichiometric to Si-rich. They studied the deposition kinetics and concluded that the deposition mechanism follows Langmuir-Hinhselwood theory where the surface adsorption and desorption of the SiH<sub>4</sub> limit the reaction rate. They also investigated the effects of temperature, pressure and gas flow ratio. The FTIR measurements showing strong peak at 837 cm<sup>-1</sup> suggests the Si-N bond and no other peaks relating to hydrogen were observed.

The detailed analysis of LPCVD silicon nitride from SiH<sub>4</sub> and NH<sub>3</sub> is given by Yacoubi et al. [37]. They reported 26 gas phase reactions are involved in the final film deposition on the silicon surface. They also observed a significant radial non-uniformity in thickness (bull's eye).

They proposed complete modeling of the silicon nitride from SiH<sub>4</sub>-NH<sub>3</sub>.

#### 2.5.2 Silicon nitride in memory

The early memory transistors were MNOS and the silicon nitride in those structures obtained by normal pressure CVD at a temperature of 900°C [16]. Fujita et al., [4] used the LPCVD silicon nitride at 700°C with SiH<sub>4</sub>, NH<sub>3</sub> and Ar as carrier gas to study the behavior of trap states by changing the SiH<sub>4</sub>/NH<sub>3</sub> ratio. They concluded that Si dangling bonds create deep trap states and the trap density increased from 2E19 cm<sup>-3</sup> to 8E19 cm<sup>-3</sup> with increase in SiH<sub>4</sub>/NH<sub>3</sub> ratio from 0.001 to 0.1.

The variation in stoichiometry of the silicon nitride and its relation to memory traps was studied by Bailey and Kapoor [38]. They used single wafer cold wall reactor with  $SiH_4$  and  $NH_3$  gases at temperatures ranging from  $700^{\circ}$ C to  $950^{\circ}$ C. They reported an increase in Si concentration with decreasing gas ratio  $NH_3$ :  $SiH_4$  from 300:1 to 25:1 and corresponding trapped electron density from 9.5E17 cm<sup>-3</sup> to 2.1E18 cm<sup>-3</sup>.

Brown et al., [39] have used 45 nm LPCVD silicon nitride in the MONOS memory transistor deposited at  $750^{\circ}$ C. They studied the effect of  $N_2$  anneal at  $900^{\circ}$ C after the formation of blocking oxide and concluded that the memory window is increased by 40%. They attributed this to annihilation of Si-H bonds with  $N_2$  anneal.

Kamigaki et al., [40] calculated the electron and hole traps in amorphous silicon nitride films from LPCVD from SiH<sub>2</sub>Cl<sub>2</sub> and NH<sub>3</sub>. The deposition temperature was 790°C and other parameters were not mentioned. They used MNOS structures to extract the trap densities and reported electron and hole trap densities were 7E18 cm<sup>-3</sup> and 1.2E19 cm<sup>-3</sup> respectively.

Libsch and White [41] studied the charge transport in SONOS devices and proposed a low voltage SONOS device programmable with 5 V. The reported deposition conditions were: SiH<sub>2</sub>Cl<sub>2</sub>: NH<sub>3</sub> - 100:30 (sccm), pressure 300 mTorr and temperature 725°C. The deposition time was varied from 4 minutes to 8 minutes to get thicknesses from 5 nm to 8 nm. Almost all publications from the research group led by M. H. White in the SONOS area use the LPCVD silicon nitride from SiH<sub>2</sub>Cl<sub>2</sub> and NH<sub>3</sub>.

Wong et al., [42] reported high quality dielectric films with small hydrogen content for non-volatile memory applications by using SiCl<sub>4</sub> and NH<sub>3</sub> at 820°C. Yun et al., [21] investigated the formation of Si-rich silicon nitride for nanoscale nonvolatile memory applications. They have used SiH<sub>2</sub>Cl<sub>2</sub> and NH<sub>3</sub> at different pressures (100-600 mTorr) and temperatures (685°C-785°C) with varying flow ratios. They reported that increase in leakage current and large flat band

voltage shift for the Si-rich (RI-2.255) nitride films compared to the films with RI 1.96.

Thus majority of the research groups uses the SiH<sub>2</sub>Cl<sub>2</sub> - NH<sub>3</sub> process for depositing the silicon nitride films. Only very few groups worked with SiH<sub>4</sub> and NH<sub>3</sub> precursors in horizontal reaction tubes for the development of silicon nitride films. The aim is to develop uniform silicon nitride films by using SiH<sub>4</sub> and NH<sub>3</sub> gases in LPCVD system.

#### 2.6 Nature of the traps in silicon nitride

The traps in the silicon nitride layer are responsible for the memory action in the SONOS device. Therefore the performance of the SONOS device depends on the distribution and density of the traps in the silicon nitride layer. Table 2.2 compares the erase speed and retention time for different energy distribution of traps. The carriers trapped in shallow traps have smaller emission times and therefore shorter retention time.

| Density of Traps | Energy Distribution | Erase speed | Retention time |

|------------------|---------------------|-------------|----------------|

| High             | Shallow             | Fast        | Short          |

| High             | Deep                | Slow        | Good           |

Table 2.2: Trap distribution and memory performance

#### 2.6.1 Amphoteric Trap model

The origin of traps is attributed to the Si dangling bonds during silicon nitride film formation [12]. A saturated Si-N bond has four N atoms covalent bonded with Si atom whereas in a dangling Si-N bond the Si atom is short of one N atom. This incomplete covalent bonding creates an energy level in the band gap of Si and acts as trap center. When a single electron is attached to this dangling bond, the charge state is neutral  $(D^0)$ . When two electrons are attached the charge state is negative  $(D^-)$  and the state is positive  $(D^+)$  when no electron is attached. The negatively charged  $D^-$  state is a hole trap and the  $D^+$  is an electron trap.

#### 2.6.2 Trap distribution

Since the earlier nitride based devices were MNOS type, the studies on trap properties and their distribution were entirely on MNOS devices. Researchers have proposed different trap distributions to study the charge trapping and detrapping mechanisms. Ross and Wallmark [13] assumed that the traps located at single energy level and distributed uniformly (Figure 2.12). They used direct tunneling theory to explain trapping and detrapping. During programming

electrons tunnel from the valance band of silicon to the traps in the nitride. During detrapping, the trapped electrons in the nitride tunnel through the oxide to the conduction band of Si.

Figure 2.12: Trap distribution model by Ross and Wallmark [13].

They considered rectangular barrier for tunneling calculations and found that the flat band voltage shift  $\Delta V_{FB}$  is proportional to logarithm of the applied pulse width.

$$\Delta V_{FB} \propto (0.577 + \ln(\frac{t}{t_0})) \tag{2.1}$$

where  $t_0$  is the time required for one transition from conduction band (valance band) edge to trap center.

Dorda and Pulver [14] considered spatially fixed but energetically distributed traps (Figure 2.13). They used direct tunneling model to explain trapping and detrapping. They neglected the conduction current in the nitride and considered the effect of transferred charge on the tunneling probability. They proposed that the traps are located at the nitride-oxide interface.

Figure 2.13: Energetical trap distribution model by Dorda and Pulver [14].

As per their theory the shift in flat band voltage given by

$$\Delta V_{FB} \propto 1 - e^{[-C_1(1 - e^{(-C_2 t)})]}$$

(2.2)

where  $C_1$  and  $C_2$  are positive constants determined by the device structure and material properties. From the tunneling kinetics they found the trap distribution is continuous and trap density of  $10^{13}cm^{-2}eV^{-1}$ .

Ferris-Prabhu [15] considered traps distributed spatially and energetically (Figure 2.14). By using direct tunneling and charge transport equation they have shown that the charge transfer with respect to time is initially linear and then varied logarithmically.

Figure 2.14: Spatial and Energetical trap distribution model by Ferris-prabhu [15].

Figure 2.15: Simple trap distribution model by White and Cricchi [16].

All the above models assumed rectangular barriers for tunneling approximation and no effect of transferred charge on the tunneling. White and Cricchi [16] assumed a simple trap distribution with single trap located near the oxide-nitride interface (Figure 2.15).

They considered the effect of transferred charge on further tunneling of carriers and used direct tunneling theory for charge transfer from deep traps to Si conduction band. Their results indicate that the shift in  $V_{TH}$  is proportional to logarithm of pulse duration.

The above models used thin oxide MNOS devices and the direct tunneling theory is applicable. Similar theory can also be applied to SONOS devices. But the tunneling mechanism depends on thickness of the ONO stack. Bachhofer et al., [17] studied the transient conduction in the SONOS devices and suggested one of the tunneling mechanisms (depends on the field and thickness) is responsible for charge transfer. The various conduction mechanisms in a n-channel SONOS device under both biases is shown in Fig. 2.16.

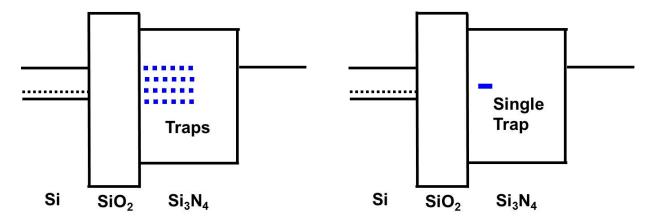

When the gate bias is positive, during charge trapping, electron tunneling from substrate to

Figure 2.16: Currents in n-channel SONOS device (a) Programming (b) Erasing [17].

nitride traps is the dominant component (J1). These electrons are then redistributed by Poole-Frenkel conduction (J2). Those electrons that are reaching the blocking oxide interface may tunnel through the blocking oxide and collected by the gate (J3). This component is negligible due to the blocking action of the top oxide. The component J4 is the hole injection from the gate and is negligible. During erase (with negative gate voltage) hole tunneling from the substrate is the main component (J5). The electric field is such that electrons tunnel from traps to substrate (J6). Electron injection from gate (J7) is the other component and is the main reason for erase saturation. Electron-hole recombination (J8) in the nitride is another component during charge transfer.

### 2.7 Trap characterization methods - Literature review

Discharge current measurement, change in flat band voltage  $\Delta V_{FB}$  and retention measurement i.e., decay in  $\Delta V_{FB}$  w.r.t time are the important characterization methods to evaluate the traps in MNOS/SONOS devices. Discharge current measurement and  $\Delta V_{FB}$  are used to calculate the trap density whereas the retention measurement is used to estimate the energy levels of the traps.

Matsuura et al., [24] used DCTS technique for evaluating the trap density and their distribution. In this method, sufficiently high voltage pulse of suitable polarity is applied to the MNS device for complete charge trapping. After the pulse is applied, the discharge current from the MNS capacitor is measured and analyzed to evaluate the trap density and trap distribution. MNS devices made on p-Si with 76 nm  $SiN_x$  layer and Al gate were used for DCTS measurements. A voltage pulse of 50 V and width 600 s was applied. They considered the hole trapping

in the nitride. The discharge currents were measured up to  $10^3$  seconds. The calculated trap density was  $2E17 \text{ cm}^{-3}$  in the energy level  $0.83 \text{ eV} < E-E_V < 0.94 \text{ eV}$ .

Roy and White [25] used retention model to extract the spatial distribution and density of traps. During the retention measurement the MONOS transistor is biased such that the Si surface is in either weak inversion or depletion. Therefore the back tunneling of the captured charge is the dominant component for the threshold voltage decay. They used the  $\Delta V_{TH}$  decay vs time data to calculate the trap distribution. The extracted trap density was 1E19 cm<sup>-3</sup> and located from 2-3 nm from the tunnel oxide-nitride interface.

Martin and Aymhich [26] characterized the charge distribution in the nitride layer by using  $\Delta V_{FB}$  decay with field assisted discharge. Since the charge stored in the deep traps, it takes very long time for detrapping. In order to accelerate the discharge process they applied voltage such that decay rate is increased. They then used the basic trap kinetics equation with Pool-Frenkel emission to extract the spatial distribution. The trap density calculated by  $\Delta V_{FB}$  was 2.4E19 cm<sup>-3</sup> and located at oxide-nitride interface with exponential tail distribution up to 10 nm in the nitride.

Chao and White [27] used linear voltage ramp technique and basic trap kinetic equation with amphoteric trap model to extract the trap density and capture cross section. The linear ramp voltage technique separates the charges at the interface, minimizes the back tunneling of trapped charge and simultaneously measures  $\Delta V_{FB}$  and injected charges  $\Delta Q_n$ ,  $\Delta Q_p$ . By considering charge centroid, they calculated the trap density and trap capture cross section 2E19 cm<sup>-3</sup> and 2E-14 cm<sup>2</sup> respectively.

Kim et al., [28] used charge decay model to determine the energy distribution of traps in SONOS devices. This is similar to the retention model proposed by White [25] but considered the effect of internal electric field at the interface between tunnel oxide and nitride. The calculated trap density was 9E18 cm<sup>-3</sup> in the energy level 1.15 - 1.55 eV from the conduction band edge.

This chapter discussed the evolution and basic principle of SONOS memory device. Issues with SONOS technology, nature of traps in the nitride layer, various trap distributions and charge transfer mechanisms were described. Literature review of process details of silicon nitride by LPCVD and trap characterization methods were presented. The next chapter describes the process optimization of silicon nitride charge trap layer.

## Chapter 3

## Silicon nitride process optimization and

## Results

As a charge trapping node for the scaled SONOS memories, the film thickness and composition of silicon nitride layer greatly determines the nonvolatile memory properties. As per ITRS 2009, charge trap layer thickness in current technology is 5 nm and expected to scale down to 4nm by 2014 [1]. Moreover the trapping efficiency depends on the thickness of the charge trap layer and the film composition. Therefore the deposition conditions must be chosen to yield good deposition rate and proper composition.

The target thickness for optimizing the deposition conditions is 20 nm with stoichiometric nitride. The refractive index of stoichiometric nitride is 1.99 - 2.0. We started the process optimization by selecting the process conditions based on literature review. The following are generally used process parameters for LPCVD silicon nitride:

- 1. Temperature range: 750°C -850°C

- 2. Pressure: 50 mTorr 1 Torr (depends on pumping system)

- 3. Gas flow ratio: depends on the required film composition, thickness and the type of precursor gases.

- 4. Deposition time: depends on the target thickness

### 3.1 Experiments

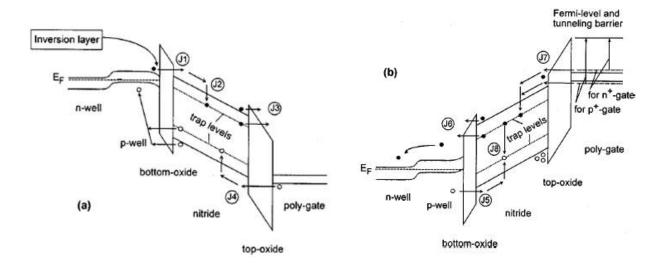

The LPCVD system used for deposition consists of a tubular hot wall reactor with three zone heater control. Figure 3.1 shows the schematic of typical LPCVD system. P-type 100 mm Si

<100>, 5-10 ohm-cm resistivity wafers were used for  $SiN_x$  deposition. After the standard RCA cleaning with HF last, the wafers were loaded into the LPCVD system and kept normal to the gas flow.

Figure 3.1: Typical three Zone LPCVD reactor.

On each side of the process wafer(s) 10 dummy wafers were placed. The wafer spacing was 0.5 cm unless otherwise specified. Every time one of the process parameters was varied systematically while keeping the other parameters constant to study the effect of process parameters on the film deposition and quality. The deposition process was automated such that all the gas lines and process tube were evacuated and temperature has been stabilized before the actual deposition step. Figure 3.2 shows temperature vs time of a example silicon nitride recipe with other process parameters.

#### 3.1.1 Results of initial experiments

The initial experiments were done with one dummy wafer on each side with temperature fixed at 780°C. To avoid gas depletion along the tube length and maintain the wafer to wafer uniformity along the boat, temperature gradient is maintained inside the process tube. The front zone is operating at 750°C, the center zone at 780°C and the rear zone at 790°C.

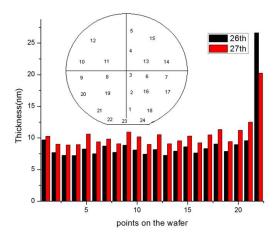

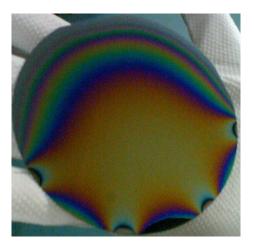

As-deposited films with pure silane, ammonia and without nitrogen dilution were very non-uniform in thickness and composition. The deposited film at the wafer periphery was very thick and of different composition when compared with the middle part of the wafer. This thick film along the circumference of the wafer forms a ring with a width  $\Delta$ w. Figure 3.3 shows the thickness non-uniformity of two wafers measured by the ellipsometer.

It is observed that the ring width (measured from wafer periphery) is increasing with the

Figure 3.2: Temperature vs time of a example recipe (not to scale). Standby temperature is 300°C, process temperature is 780°C and pressure is 300 mTorr. Base pressure is < 0.005 Torr.

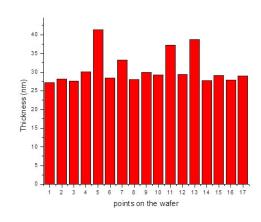

film thickness (Bull's eye effect). This may be due to insufficient supply of intermediate gas phase reacting species to the center part of the wafer. Bull's eye effect is significant in depositing thicker nitride films. Figure 3.4 shows the images of bull's eye and ring formation along the wafer periphery.

The following gas phase reactions are important for the successful deposition [18].

- Diffusion of initial reactants into the gap between wafers  $(W_{D,in})$

- Reaction in the gas phase  $(W_{hom})$

- Diffusion of intermediates to the surface  $(W_{D,P})$

- Heterogeneous reaction generating final product  $(W_{het})$

The non-uniformity is due to different values of  $W_{D,P}$  and  $W_{het}$  at the wafer edge and at the center part of the wafer. Especially,  $W_{D,P}$  is very less than  $W_{het}$  in the center part of the wafer. The ellipsometry measurements confirmed the non-uniformity in thickness and composition. The measurement on the ring gives high thickness with silicon rich nitride compared to the middle part of the wafer. The reason for this non-uniformity could be the gas flow inside the process tube is not laminar enough. In order to streamline the gas flow inside the process tube, 10 dummy wafers were kept on both sides of the process wafer. Both the wafer-to-wafer and within wafer thickness variations were reduced by small amount. Figure 3.5 shows the thickness variations on 4-inch wafer for two recipes with dummy wafers used during deposition.

Figure 3.3: Thickness nonuniformity in two cases (a) SiH<sub>4</sub>- 15 sccm, NH<sub>3</sub>-150 sccm at  $780^{\circ}$ C and 300 mTorr (for two wafers). (b) SiH<sub>4</sub>- 15 sccm, NH<sub>3</sub>-225 sccm at  $780^{\circ}$ C and 300 mTorr (measured in the center part of the wafer map in (a)).

Figure 3.4: (a) Bull's eye effect,  $SiH_4$ - 30 sccm,  $NH_3$ -75 sccm at  $780^{\circ}C$  and 300 mTorr. (b) Ring formation along the wafer circumference,  $SiH_4$ - 15 sccm,  $NH_3$ -45 sccm at  $780^{\circ}C$  and 300 mTorr.

For a given NH<sub>3</sub> flow rate, the deposition rate increases with the SiH<sub>4</sub> flow rate and also the non-uniformity. It is also observed that deposition rate drops with the increase in NH<sub>3</sub> flow suggesting that NH<sub>3</sub> inhibits the adsorption of Si reacting species onto the substrate. The deposition rate and refractive index with varying NH<sub>3</sub> flow is shown in Fig 3.6.

Following no. of trials, it is observed that the flow ratio ( $R = SiH_4:NH_3$ ) 40:50 (sccm) giving optimum results and further optimization is carried out by using this gas flow ratio.

# 3.1.2 Solutions to reduce non-uniformity

The main reason for this non-uniformity in thickness and composition across the wafer could be insufficient diffusion of the intermediate reaction products (that are responsible for the final

Figure 3.5: Thickness variations after dummy wafers used during deposition for two recipes.  $SiH_4:NH_3$  are 15:75 sccm and 30:75 sccm respectively at 780°C and 300 mTorr.

Figure 3.6: Deposition rate and refractive index with change in  $NH_3$  flow.  $SiH_4$  - 15 sccm, Temperature - 780°C and Pressure - 300 mTorr.

film formation) to the center part of the wafer. From section 3.1.1, the non- uniformity can be reduced by making  $W_{D,P}$  is equal to  $W_{het}$ . The following could be the probable solutions to improve the uniformity.

### 1. Use diluent gas

The diluent gas helps in reducing the concentration of the reactive gases and enables the mixing of gases without any spontaneous reaction. The diluent gas also helps in diffusing enough mixture to the surface of the heated substrate. This condition is necessary for film deposition [19].

### 2. Modification of wafer boat

The significant radial non-uniformity in both thickness and composition can also reduced by modification of the wafer boat<sup>1</sup>. A specially designed wafer boat having small holes to allow the gases in which the wafers are enclosed can reduce the non- uniformity. However, the design and maintenance of such wafer boats are difficult and expensive.

We implemented the solution 1 by adding extra  $N_2$  line to the existing system. The following sections describe the results of the modified process.

<sup>&</sup>lt;sup>1</sup>Unpublished work by Rosler et al.(1977)

# 3.2 Effect of $N_2$ dilution

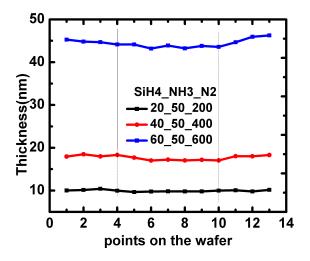

A significant improvement in uniformity is observed when  $N_2$  is used during deposition. The diluent gas optimizes the turbulence and gas flow conditions for establishing good film uniformity. Therefore, adding  $N_2$  to the reaction chamber reduces desorption of  $SiH_2$  intermediate from the surface of the wafer and hence the deposition rate. Too high flow rate of diluent gas reduces the deposition rate drastically. The  $SiH_4$  to  $N_2$  ratio is the key to obtain optimum deposition rate. Figure 3.7 shows the effect of  $N_2$  dilution on deposition rate and refractive index respectively. The decrease in refractive index is attributed to the desorption of  $SiH_2$ .

Figure 3.7: Effect of  $N_2$  dilution on (a) thickness (b) refractive index.  $SiH_4:NH_3$  - 40:50 sccm,  $780^{\circ}C$ , 300 mTorr and 20 min.

Points 1-4 and 11-13 are measured along the wafer periphery. Points 5-10 are measured in the central part of the wafer. This convention is followed in the figures with x-axis named "points on the wafer". This is shown in Fig. 3.8.

Figure 3.8: Wafer map showing the measurement points on 4-inch wafer by ellipsometer.

With  $N_2$  dilution the uniform area on the wafer increases. This is shown in Fig. 3.9. On a 4-inch wafer, around 95% area with uniform film thickness was obtained when 1000 sccm of  $N_2$  is used in the reaction chamber. In terms of yield, around 13% increment was obtained with dilution for the same deposition time.

Figure 3.9: Ring width vs  $N_2$  flow. SiH<sub>4</sub>:NH<sub>3</sub> - 40:50 sccm, 780°C, 300 mTorr and 20 min.

Figure 3.10: FTIR measurements on asdeposited  $SiN_x$  films. The legend in the figure indicates gas flow in sccm. Temperature-780°C, pressure-300 mTorr and deposition time-20 min.

In order to study the presence of other impurities such as oxygen and hydrogen, FTIR measurements were done. Figure 3.10 shows FTIR transmission spectra of as-deposited  $SiN_x$  films. The main absorption band located at 833 cm<sup>-1</sup> to 840 cm<sup>-1</sup>. This belongs to Si-N stretching bond. Some weak bonds were also observed in the vicinity of 580 cm<sup>-1</sup>. These were identified as Si-N bending bonds. No significant Si-H and N-H bond was observed in the as-deposited SiNx films. With no dilution the main absorption peak was observed at 833 cm<sup>-1</sup> whereas the same absorption peak was shifted to 837 cm<sup>-1</sup> when  $N_2$  was used as diluent.

The quality of the as-deposited films was verified by chemical etch test. Figure 3.11 shows the effect of  $N_2$  dilution on etch rate and refractive index. The deposition time is same for these experiments. The etch rate of the  $SiN_x$  films in 5:1 HF increases with the  $N_2$  dilution. This suggests that the films with more silicon content were very dense in nature. In order to confirm this, Si-rich  $SiN_x$  films were deposited by changing the  $SiH_4$  flow and tested (Figure 3.12).

# 3.3 Change in SiH<sub>4</sub> flow

For a fixed NH<sub>3</sub> flow of 50 sccm, the thickness increases with SiH<sub>4</sub> flow. For comparison, the deposition time is same for all experiments and also SiH<sub>4</sub>:N<sub>2</sub> is 1:10. The ring width  $\Delta$ w along

Figure 3.11: Etch rate in 5:1 HF with different  $\rm N_2$  flow.  $\rm SiH_4:NH_3$  - 40:50 sccm,  $780^o\rm C$ , 300 mTorr and 20 min.

Figure 3.12: Etch rate in 5:1 HF with different SiH<sub>4</sub> flow. SiH<sub>4</sub>:N<sub>2</sub> ratio is 1:10, NH<sub>3</sub> - 50 sccm,  $780^{\circ}$ C, 300 mTorr and 20 min.

the wafer periphery increases with the SiH<sub>4</sub> flow. For the flow ratio ( $R = SiH_4$  flow/ NH<sub>3</sub> flow) 0.8, the film is stoichiometric. With R = 1.2 the film becomes Si rich as expected and also the deposition rate increases. Thickness measurements by ellipsometer are shown in Fig. 3.13. As the films become Si rich the etch rate is reduced (Figure 3.12).

Figure 3.13: Effect of SiH<sub>4</sub> flow on thickness. SiH<sub>4</sub>:N<sub>2</sub> ratio is 1:10, NH<sub>3</sub> - 50 sccm,  $780^{\circ}$ C, 300 mTorr and 20 min.

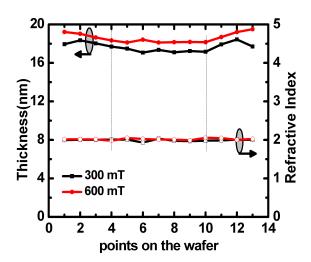

Figure 3.14: Effect of deposition pressure.  $SiH_4:NH_3:N_2$  - 40:50:400 sccm,  $780^{o}C$ , 300 mTorr and 20 min.

# 3.4 Effect of pressure

The deposition pressure has very little effect on the deposition rate and film composition as shown in Fig. 3.14. The thickness and refractive index increases by very small value with the deposition pressure. But for reduced pressure and gas flow, the deposition rate increases and also the uniformity. This may be due to higher diffusion at lower pressures still maintaining the surface reaction limited deposition.

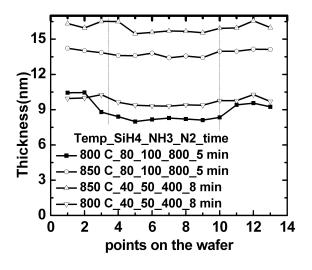

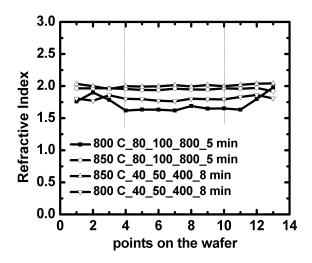

# 3.5 Effect of deposition temperature

The effect of temperature on deposition rate and refractive index is shown in Fig. 3.15. For a given gas flow ratio, the deposition rate increases with the temperature. The refractive index measurement shows that Si content in the  $SiN_x$  film is increasing with the temperature. The increase in thickness is attributed to increase of surface diffusion of Si reacting species at high temperatures. This is similar to the results of LPCVD  $SiN_x$  thin films from DCS and  $NH_3$  reported by Yun et al., [21].