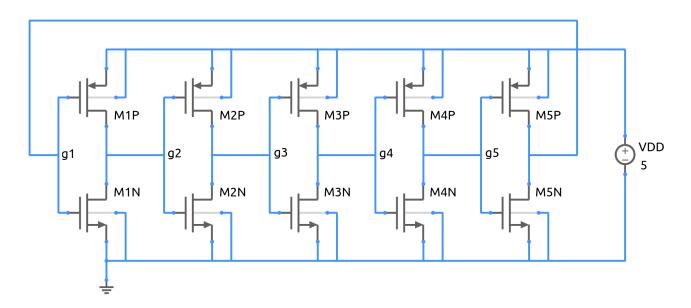

## mos\_ring\_osc.sqproj

A ring oscillator with five CMOS inverters is shown in the figure. The oscillation frequency is given by

$$f_o = \frac{1}{n \ (t_{PHL} + t_{PLH})} \,, \tag{1}$$

where n is the number of inverters, and  $t_{PHL}$ ,  $t_{PLH}$  are the propagation delays of one inverter driving another identical inverter. The delays are determined broadly by two factors: (i) the capacitance seen at the output of the inverter, (ii) the current carrying capability of the transistors. The capacitance seen at the inverter output node is proportional to  $W \times L$  (the transistor area), and the current carried by a transistor is proportional to W/L.

## Exercise Set

- Run the simulation, plot the voltages at the five inverter output nodes (together), and explain how they are related. From the plot, calculate the oscillation period and frequency.

- 2. Make the following changes, run the simulation, plot V<sub>G1</sub>(t), and compare the oscillation period with the original value. Explain qualitatively your results in each case. (Note that the global parameters w\_n, w\_p, phi\_n, phi\_p are convenient here, with phi\_n, phi\_p controlling the threshold voltages<sup>1</sup> of the n- and p-channel transistors, respectively.)

<sup>&</sup>lt;sup>1</sup>The circuit file mos\_iv\_1.sqproj may be used to see the effect of phi on the  $I_D$ - $V_G$  curve.

- (a) The length as well as width of each *n*-channel transistor are doubled.

- (b) Width of each *n*-channel transistor is changed from  $5 \,\mu\text{m}$  to  $20 \,\mu\text{m}$ .

- (c) Width of each *p*-channel transistor is changed from  $5 \,\mu\text{m}$  to  $20 \,\mu\text{m}$ .

- (d) Width of each transistor is changed from  $5 \,\mu m$  to  $20 \,\mu m$ .

- (e) The parameter phin is decreased by 0.5.

- (f) The parameter phi\_p is decreased by 0.5.

## References

R. J. Baker, H. W. Li, and D. E. Boyce, CMOS Circuit Design, Layout, and Simulation, Prentice-Hall India, 1998.