## Power Issues in SoCs: Power Aware DFT Architecture and Power Estimation

A THESIS SUBMITTED FOR THE DEGREE OF

### Doctor of Philosophy

IN THE COMPUTER SCIENCE AND ENGINEERING

by

### Jaynarayan Thakurdas Tudu

Department of Computer Science & Automation Division of Electrical Sciences Indian Institute of Science BANGALORE – 560 012

July 2016

©Jaynarayan Thakurdas Tudu July 2016 All rights reserved i

Dedicated to

Jagannatha

## Declaration

I, Jaynarayan Thakurdas Tudu, with SR No. 4714-120-101-07951 hereby declare that the material presented in the thesis titled

### Power Issues in SoCs: Power Aware DFT Architecture and Power Estimation

represents original work carried out by me in the **Deparment of Computer Science** and Automation at Indian Institute of Science during the years 2010 - 2016. With my signature, I certify that:

- I have not manipulated any of the data or results.

- I have not committed any plagiarism of intellectual property. I have clearly indicated and referenced the contributions of others.

- I have explicitly acknowledged all collaborative research and discusions.

- I have understood that any false claim will result in severe disciplinary action.

- I have understood that the work may be screened for any form of academic misconduct.

## Certificate

In my capacity as supervisor of the above-mentioned work, I certify that the above statements are true to the best of my knowledge, and I have carried out due diligence to ensure the originality of the report.

Prof. Matthew Jacob Thazhuthaveetil

Signature

## Acknowledgements

It gives me immense pleasure to express my sincere thanks and gratitude to all those who have kindly helped me in carrying out this research work. I am very much thankful to Prof. Virendra Singh, IIT-Bombay and Prof Matthew Jacob for their guidance through out the research. From the very beginning of my PhD days Prof. Matthew and Prof. Singh have been guiding me in all the aspects of my research. I am particularly thankful to Prof Virendra Singh for he has kindly welcomed me to IIT Bombay and ensured my stay and research in every visit to CADS laboratory. Prof Matthew has been constantly monitoring my progress which helped me pursue the research even when I used to feel moral weakness. Prof. Matthew has provided me a several technical inputs though my research area is slightly different than his usual area of interest, the inputs has latter on resulted in the publications. Prof. Matthew has been very much accommodative in various situation particularly for my visit to IIT-Bombay. I am thankful to MHRD, Govt. of India and IISc for supporting my entire research by institute scholarship.

It was my pleasure to share and discuss some our ideas with Prof Shankar Balachandran, IIT Chennai. I respect his quick ideas and suggestions, many of our work got good shape partly because of his suggestions.

Prof Kewal Saluja of University of Wisconsin for all of our works has given many valuable suggestions and reviewed our ideas on Joint-scan architecture. In the starting of this work Prof. Saluja has given us a good motivation to look into the architectural aspect of Joint-scan. Prof Jank Patel, University of Illinois, UC, used be our frequent guest at CADSL, IIT Bombay. Many of our ideas which sprung from our daily meeting are strengthen by Prof. Janak Patel. He often boosts our moral in pursuing research with engineering attitude. Prof Janak has taught us how by taking care of minor aspects of research work, the larger problem get better understanding.

During my stay at IISc I have met with some of the fine professors whose words are filled with inspirations and encouragements. I thank Prof Y Narahari for his support in each and every difficulty of my IISc research life. Prof Narahari is the person who understand the student's difficulty from the first person perspective. Prof M Narasimha Murthy has always helped me and ensured my timely research and completion of the thesis. I am very much thankful to the current chairman of our department Prof. Jayant Haritsa for he has always pushed me for early completion of the thesis, Professor has officially ensured all of my visits to IIT-Bombay for research to happen in fast track.

I would like to acknowledge the help I got from the technical staff member of ALTERA laboratory at Department of Electronic System Engineering, IISc in using Synopsys and other CAD tools. I also would like thank my colleagues at VLSI Design laboratory, EE, IIT-Bombay for providing me access to Synopsys and Cadence tools. I acknowledge the collaborative work with LSI Logic where we performed experiments on peak power issues.

Many of my friends have contributed to our research work. I am extremely thankful to my co-authors who have actually experimented upon many of our ideas. My colleague Deepak Malani has contributed in several aspect of our work on worst power estimation. Thanks to Alok Malakar for conducting a lot of experiments on flip-flop design, building libraries, doing place and routing of the proposed architecture. Thanks to Binod and Nehru for exploring and experimenting on dynamic and bombay scan. Our friend Satdev has done a work for which I am really thankful to him. We have designed a set of flip flops for high performance and low power scan test. Thanks to Rohini and Nihar for extending the work on worst power estimation. I am thankful to Suryakantji and Toral madam for their constant support in several technical difficulties. Our research atmosphere has always been kept vibrant by several of my friends at CADSL, I thank to Prashant, Sandipan, Nitant, Karthik, Virat, and Vijay for always keeping me encouraged in doing research of some or other kind.

IISc campus has always been a place of quest. Though I am ordinary researcher but my friends have always kept my quest alive for knowing nature or something. I thank Hrishikesh, Ramesh, Ashish, Thulasi Raman, Govind and other friends for helping me in several occasion for several reasons. We have always cherished the discussions on topic which great scientists sometime feel reluctant to discuss. Specially I thank to Ramesh and Ashish for sparing time for me to make me understand the CAD tools and the detail concept of VLSI technology.

Staying in Bangalore has always been a pleasant for me. The due goes to my senior brothers of Bhaktivedanta Institute, Bangalore who have always provided me an opportunity to explore the different horizon of life.

The love and care that I have received from my parents can not be acknowledged formally, those are priceless. I pray to lord that may I ever serve them and keep them in a happy life.

Saying is that without the mercy of supreme lord even a blade of grass does not move. Lord, you are great, may your greatness be always echoed in my mind.

## Vita

I am a bottom line PhD research scholar in the Department of Computer Science and Automation, IISc, Bangalore. I have completed MSc(Engg) from the same department in the year of 2010. My master research work has been supervised by Prof. Virendra Singh and Prof. Matthew Jacob T. During my master I have worked on peak power issues in SoC testing. As part of the master work I have co-authored some of the papers in proceedings of leading test conferences. During my PhD I have worked on power issues in SoC during test and worst power estimation problem. I have co-authored a few number of papers in proceedings of some of the test conferences and symposiums. I have volunteered as a peer reviewer for ATS, VLSID, VDAT and few other conferences. Also, severed as an organising member for some of the conferences and workshop on vlsi test.

I have done my BE (Bachelor of Engineering) in Computer Science and Engineering from Institute of Technical Education and Research (then affiliated to Biju Patnaik University of Technology), Bhubaneswar, Odisha in the year of 2005. I have spent a year in self learning in pursuance of higher study. Thereafter, briefly for one year I taught a BTech course at Silicon Institute of Technology, Bhubaneswar, Odisha from 2006 to 2007.

I am born and brought up in the state of Odisha. Most of my early life I have spent in village and now I am in middle of my life, spending time in moving around in different cities. I hope, one day I could return back to my village and spend a time in peace and silence with that scenic nature. I take interest in philosophy, often try to find out whether the technology have any link with the principle of life. I write blogs, visit: www.consciousnessasitis.blogspot.com for more articles.

## **Publications**

#### Included in Thesis

- Jaynarayan Tudu, Alok Malakar, and Virendra Singh, "An Architectural Approach to Efficient Hybridization of Serial and Random Access Scan". [Manuscript under preparation for *IEEE Trans*action in VLSI].

- Jaynarayan Tudu and Virendra Singh, "Efficient Test Control Mechanism for Joint-scan DFT Architecture", IEEE 25th Asian Test Symposium (ATS-2016), Hiroshima, Japan. [Under review].

- Satyadev Ahlawat, Jaynarayan Tudu, Anzhela Matrosova, and Virendra Singh, "A High Performance Scan Flip-Flop Design for Serial and Mixed mode Scan Test", *Proceedings in IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS-2016)*, Catalunya, Spain, July, 2016.

- Jaynarayan Tudu, "JSCAN: A Joint-scan DFT Architecture to Minimize Test Time, Data Volume, and Test Power", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT-2016), Guwahati, India, May, 2016.

- Jaynarayan Tudu and Satyadev Ahlawat, "Guided Shifting of Test Pattern to Minimize Test Time in Serial Scan", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT-2016), Guwahati, India, May, 2016.

- Jaynarayan Tudu, Deepak Malani, Virendra Singh, "Level-Accurate Peak Activity Estimation in Combinational Circuit Using BILP", Communication in Computer and Information Science, Springer Berlin Heidelberg, Proceeding in 17th VLSI Design and Test(VDAT)-2013, Jaipur, India, pp. 345 - 352.

- Jaynarayan Tudu, Deepak Malani, and Virendra Singh, "ILP Based Approach for Input Vector Controlled Toggle Maximization in Combinational Circuits", Springer Berlin Heidelberg, 16th International Symposium on VLSI Design and Test (VDAT) 2012, Kolkata, India, pp. 172 - 179.

Jaynarayan Tudu, Erik Larsson, Virendra Singh, and Hideo Fujiwara, "Graph Theoretic Approach for Scan cell Reordering to Minimize Peak Shift Power", Proc. in 20th IEEE/ACM Great Lakes Symposium on VLSI (GLSVLSI-2010), Rhode Island, USA.

#### Other Contributions

- Rohin Gulve, Nihar Hage, and Jaynarayan Tudu, "On Determination of Instantaneous Peak and Cycle Peak Switching using ILP", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT-2016), Guwahati, India, May, 2016.

- Binod Kumar, Boda Nehru, Brajesh Pandey, and Jaynarayan Tudu, "Bombay Scan: A Low Power Reconfigurable Scan Architecture", *IEEE-TTTC Reliability Aware System Design and Test (RASDAT-2016)*, Kolkata, India.

- Binod Kumar, Boda Nehru, Brajesh Pandey, and Jaynarayan Tudu, "Skip-scan: A Methodology for Test Time Reduction", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT-2016), Guwahati, India, May, 2016.

- Satyadev Ahlawat and Jaynarayan Tudu, "On Minimization of Test Power through Modified Scan Flip-flop", Proceedings 20th International Symposium on VLSI Design and Test (VDAT-2016), Guwahati, India, May, 2016.

- Satdev Ahlawat, Jaynarayan Tudu, Anzhela Matrosava, Virendra Singh, "A New Scan Flip Flop Design to Eliminate Performance Penalty of Scan", Proc. in IEEE 24th Asian Test Symposium (ATS-2015), Mumbai, India.

## Abstract

Test power, data volume, and test time have been long-standing problems for sequential scan based testing of system-on-chip (SoC) design. The modern SoCs fabricated at lower technology nodes are complex in nature, the transistor count is as large as billions of gate for some of the microprocessors. The design complexity is further projected to increase in the coming years in accordance with Moore's law. The larger gate count and integration of multiple functionalities are the causes for higher test power dissipation, test time and data volume. The dynamic power dissipation during scan testing, i.e. during scan shift, launch, and response capture, are major concern for reliable as well as cost effective testing. The excessive average power dissipation leads to a thermal problem which causes burn-out of the chip during testing. The peak power on other hand causes test failure due to power induced additional delay. The test failure has direct impact on yield. The test power problem in modern 3D stacked based IC is even a more serious issue. Estimating the worst case functional power dissipation is yet another great challenge. The worst case functional power estimation is necessary because it gives an upper bound on the functional power dissipation which can further be used to determine the safe power zone for the test.

Several solutions in the past have been proposed to address these issues. In this thesis we have proposed two sets of design-for-test (DFT) solutions: 1) Sequential scan chain reordering, and 2) JScanan alternative Joint-scan DFT architecture to address primarily the test power power along with test time and data volume, and an integer linear programming based methodology to address the power estimation problem. We have proposed a graph theoretic based formulation for scan chain reordering and for optimum scan shift operation. For each formulation a set of algorithms is proposed. The experimental results on ISCAS-89 benchmark circuit show a reduction of around 25% and 15% in peak power and scan shift time respectively.

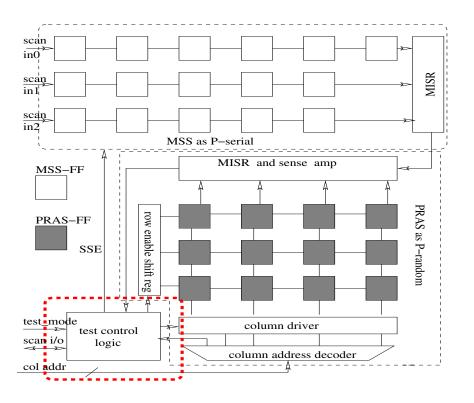

In order to have a holistic DFT architecture which could solve test power, test time, and data volume problems, a new DFT architecture called Joint-scan (*JScan*) have been developed. In *JScan* we have integrated the serial and random access scan architectures in a systematic way by which the *JScan* could harness the respective advantages from each of the architectures. The serial scan architecture suffers from test power, test time, and data volume problems. However, the serial scan is simple in

terms of its functionality and is cost effective in terms of DFT circuitry. Whereas, the random access scan architecture is opposite to this; it is power efficient and it takes lesser time and data volume compared to serial scan. However, the random access scan occupies larger DFT area and introduces routing congestion. Therefore, here we have proposed a methodology to realize the *JScan* architecture as an efficient alternative for standard serial and random access scan. Further, the *JScan* architecture is optimized and it resulted into a 2-Mode 2M-*Jscan* Joint-scan architecture. The proposed architectures are experimentally verified on larger benchmark circuits and compared with existing state of the art DFT architectures. The results show a reduction of 50% to 80% in test power and 30% to 50% in test time and data volume. The proposed architectures are also evaluated for routing area minimization and we obtained a saving of around 7% to 20% of chip area.

Estimating the worst case functional power being a challenging problem, we have proposed a binary integer linear programming (BILP) based methodology. Two different formulations have been proposed considering the different delay models namely zero-delay and unit-delay. The proposed methodology generates a pair input vectors which could toggle the circuit to dissipate worst power. The BILP problems are solved using CPLEX solver for ISCAS-85 combinational benchmark circuits. For some of the circuits, the proposed methodology provided the expected worst possible power dissipation i.e. 80 to 100% toggling in nets.

# Keywords

VLSI Testing, Design-for-Test, Random Access Scan, Multiple Sequential Scan, Congestion Aware Scan Architecture, Power aware test, Vector reordering, Scan reordering, Graph algorithm, Power Estimation, and BILP Programming

# Notation and Abbreviations

| $C_L$                | Load Capacitance                  | IC                     | Integrated Circuit                |

|----------------------|-----------------------------------|------------------------|-----------------------------------|

| $C_p$                | Capture Pulse                     | ILP                    | Integer Linear Programming        |

| $E_{CL}$             | Energy Stored in Load Capacitance | JScan                  | Joint-scan                        |

| $E_{VDD}$            | Total Energy Dissipation          | Κ                      | Krishna                           |

| $G_w(E, V, W)$       | Weighted complete graph           | LOC                    | Launch on Capture                 |

| $G_{wd}(E,V,W)$      | Weighted directed complete graph  | LOS                    | Launch on Shift                   |

| $I_{stat}$           | Static current                    | LSSD                   | Level Sensitive Scan Design       |

| $L_p$                | Launch Pulse                      | MISR                   | Multiple Input Signature Register |

| $P_{dyn}$            | Average Dynamic Power             | MOS                    | Metal Oxide Seminconductor        |

| $P_{stat}$           | Average Static Power              | MSDFF                  | Multiplexed Scan D Flip-flop      |

| $V_{DD}$             | Drain Supply Voltage              | MSS                    | Multiple sequential scan          |

| 2M-JScan             | 2-Mode Joint-scan                 | MT-Fill                | Minimum Transition Fill           |

| ATE                  | Automatic Test Equipment          | MaxST                  | Maximum Spanning Tree             |

| ATPG                 | Automatic Test Pattern Generation | $\operatorname{MinST}$ | Minimum Spanning Tree             |

| ATSP                 | Asymetric TSP                     | NMOS                   | N-type MOS                        |

| BILP                 | Binary Integer Linear Programming | OSC -                  | Optimum shift cycle               |

| BIST                 | Built-In Self-Test                | P-random               | Partial random access scan        |

| C-X                  | Care - don't care bit pair        | P-serial               | Paritial serial scan              |

| CBR                  | Care Bit Ratio                    | PBSAT                  | Pseudo Boolean Satisfiability     |

| CMOS                 | Complementary MOS                 | PCB                    | Printed Circuit Board             |

| CP                   | Clock Signal/Pulse                | PDN                    | Power Distribution Network        |

| $\operatorname{CUT}$ | Circuit Under Test                | PI                     | Primary Input                     |

| DC                   | Direct Current                    | PMOS                   | P-type MOS                        |

| $\mathrm{DFT}$       | Design-for-Test                   | РО                     | Primary Output                    |

| DSM                  | Deep Sub Micron                   | PPI                    | Pseudo Primary Input              |

| G(V, E, W)           | Unidirected Graph                 | PPO                    | Pseudo Primry Output              |

| PRAS            | Progressive Random Access Scan           |

|-----------------|------------------------------------------|

| PRAS-FF         | Progressive random access scan flip-flop |

| RAM             | Random Access Memory                     |

| RAS             | Random Access Scan                       |

| RTL             | Register Transfer Laguage                |

| RVW             | Response Vector Weight                   |

| SAF             | Stuck-at-Fault                           |

| SAT             | Satisfiability Problem                   |

| SE/SEn          | Scan Enable                              |

| $\mathrm{SF}_i$ | $i^{th}$ Scan flip-flop                  |

| SSD-FF          | Serial scan D flip-flop                  |

| SoC             | System On Chip                           |

| TCL             | Test Control Logic                       |

| TCLK            | Test Clock                               |

| TCl             | Test Clock                               |

| TDF             | Transition Delay Fault                   |

| TSP             | Travelling Sales Person Problem          |

| TVM             | Test Vector Weight                       |

| VLSI            | Very Large Scale Integration             |

| WOR-BIST        | Word oriented build in self test         |

| WTM             | Weighted Transition Metric               |

| X-C             | Don't care - care bit pair               |

| X-Fill          | Don't Care Fill                          |

# Contents

| Declar                                                                      | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i                                                                                                                                                          |  |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Certifi                                                                     | Certificate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |  |  |

| Ackno                                                                       | wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | iii                                                                                                                                                        |  |  |

| Vita                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\mathbf{v}$                                                                                                                                               |  |  |

| Public                                                                      | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\mathbf{vi}$                                                                                                                                              |  |  |

| Abstra                                                                      | act                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | viii                                                                                                                                                       |  |  |

| Keywo                                                                       | ords                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{x}$                                                                                                                                               |  |  |

| Notati                                                                      | on and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xi                                                                                                                                                         |  |  |

| <ol> <li>Intra<br/>1.1<br/>1.2</li> <li>1.3</li> <li>1.4<br/>1.5</li> </ol> | roduction and MotivationIntroductionPower Dissipation in VLSI Circuit1.2.1 Dynamic Power Dissipation1.2.2 Static Dissipation1.2.3 Metrics to Measure PowerTesting of VLSI Circuit1.3.1 VLSI Design and Test Flow1.3.2 Scan Architecture and Scan Testing1.3.3 Shift and Capture PowerPower Estimation ProblemThesis Contributions and Organization                                                                                                                                                                                                                                                          | 1<br>3<br>4<br>5<br>6<br>8<br>9<br>11<br>15<br>17<br>18                                                                                                    |  |  |

| <ul> <li>2 Pre</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> </ul>            | evious Work         Scope of the Literature Review         Minimization of Average Power         2.2.1       Circuit Modification Techniques         2.2.2       ATPG Based and Test Vector Modification Techniques         2.2.3       Test Vector Ordering Techniques         2.2.4       Scan Chain Ordering Techniques         2.3.1       Circuit Modification Techniques         2.3.2       ATPG Based and Test Vector Modification Techniques         2.3.3       Test Vector Ordering Techniques         2.3.4       Scan Chain Ordering Techniques         2.3.5       Test Scheduling Approaches | <ul> <li>20</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> <li>28</li> <li>29</li> <li>29</li> </ul> |  |  |

### CONTENTS

|   | 2.4          | Random Access Scan Architecture (RAS)    30                                                                                                                |

|---|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.5          | Worst Case Power Estimation    31                                                                                                                          |

|   | 2.6          | Motivation                                                                                                                                                 |

|   | <b>D</b>     |                                                                                                                                                            |

| 3 |              | Power Minimization in Serial Scan       34         Introduction       34                                                                                   |

|   | $3.1 \\ 3.2$ |                                                                                                                                                            |

|   | 3.2<br>3.3   |                                                                                                                                                            |

|   | ა.ა          |                                                                                                                                                            |

|   |              | 0 I                                                                                                                                                        |

|   | 3.4          | 3.3.2 Basis of Power Reduction by Scan Cell Reordering39Problem Formulation39                                                                              |

|   | 3.4          |                                                                                                                                                            |

|   |              | 1                                                                                                                                                          |

|   | 9 5          | 1                                                                                                                                                          |

|   | 3.5          | Proposed Algorithm                                                                                                                                         |

|   |              | 3.5.1 Construction of Hamiltonian cycle                                                                                                                    |

|   | 2.0          | 3.5.2 Construction of Hamiltonian path $\dots \dots \dots$ |

|   | 3.6          | Time and Space Complexity    48      2.6.1    Time Complexity                                                                                              |

|   |              | $3.6.1  \text{Time Complexity} \qquad 48$                                                                                                                  |

|   | 0.7          | $3.6.2  \text{Space Complexity}  \dots  48$                                                                                                                |

|   | 3.7          | Experimental Results                                                                                                                                       |

|   | 3.8          | Conclusion                                                                                                                                                 |

| 4 | Test         | Time Minimization in Serial Scan 51                                                                                                                        |

| - | 4.1          | Introduction                                                                                                                                               |

|   | 4.2          | Previous Work                                                                                                                                              |

|   | 4.3          | Proposed Scan Chain Ordering Technique                                                                                                                     |

|   | 1.0          | 4.3.1 Basic Idea                                                                                                                                           |

|   |              | 4.3.2 Graph Construction                                                                                                                                   |

|   |              | 4.3.3 Hamiltonian Path Problem Formulation                                                                                                                 |

|   |              | 4.3.4 Kruskal's MaxST and MinST Algorithm                                                                                                                  |

|   | 4.4          | Test Pattern Reordering       63                                                                                                                           |

|   |              | 4.4.1 Graph Construction                                                                                                                                   |

|   |              | 4.4.2 TSP and MST Based Heuristic                                                                                                                          |

|   | 4.5          | Experimental Result and Discussion                                                                                                                         |

|   | 4.6          | Conclusion and Prospects       67                                                                                                                          |

|   | 1.0          |                                                                                                                                                            |

| 5 | JSc          | an: A Joint-scan DFT Architecture 68                                                                                                                       |

|   | 5.1          | Introduction                                                                                                                                               |

|   |              | 5.1.1 Chapter Organization                                                                                                                                 |

|   | 5.2          | Previous Work                                                                                                                                              |

|   | 5.3          | Proposed JScan Architecture                                                                                                                                |

|   |              | 5.3.1 Architecture                                                                                                                                         |

|   |              | 5.3.2 Functionality                                                                                                                                        |

|   |              | 5.3.3 Scan Cell Segregation Methodology                                                                                                                    |

|   |              | 5.3.4 Test Time, Data Volume, and Power                                                                                                                    |

|   | 5.4          | Experimental Result and Discussion                                                                                                                         |

|   | 5.5          | 2M-JScan Architecture                                                                                                                                      |

|   |              | 5.5.1 The Architecture                                                                                                                                     |

|   |              | 5.5.2 Limitations of JScan                                                                                                                                 |

|   |              | 5.5.3 Test Pattern Alignment                                                                                                                               |

|   |              | 5.5.4 Test Control Mechanism                                                                                                                               |

|   |              | 5.5.5 Functionality                                                                                                                                        |

|   |              | 5.5.6 Clustering of Scan Flip-flops                                                                                                                        |

### CONTENTS

|   |     | 5.5.7 Computation of Test Parameters                                       | 94  |

|---|-----|----------------------------------------------------------------------------|-----|

|   | 5.6 | Experimental Result and Discussion                                         | 96  |

|   | 5.7 | Variants of Joint-Scan Architecture and Future Work                        | 98  |

|   | 5.8 | Conclusion                                                                 | 99  |

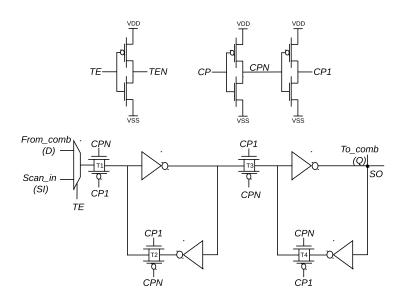

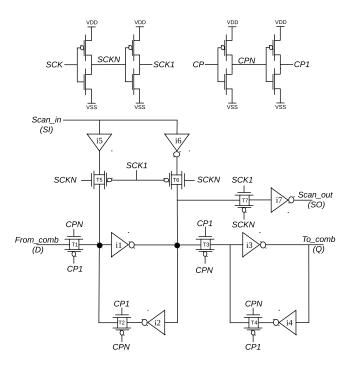

| 6 | Sca | an Flip-flop Design                                                        | 101 |

|   | 6.1 | Introduction                                                               | 101 |

|   | 6.2 | Preliminaries and Proposed Scan Flip-Flop                                  | 105 |

|   |     | 6.2.1 Proposed Scan Flip-Flop Design                                       | 106 |

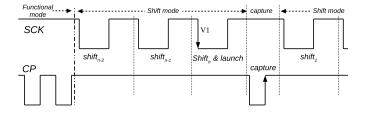

|   | 6.3 | Application of Test Vectors                                                | 109 |

|   |     | 6.3.1 Stuck-at-fault test                                                  | 109 |

|   |     | 6.3.2 Launch-on-capture test                                               | 111 |

|   |     | 6.3.3 Launch-on-shift test                                                 | 111 |

|   | 6.4 | The Proposed Scan Flip-flop as a Joint-scan Cell                           | 112 |

|   | 6.5 | Experimental Results                                                       | 114 |

|   | 6.6 | Conclusion                                                                 | 115 |

|   |     |                                                                            |     |

| 7 |     | rst Case Power Estimation                                                  | 117 |

|   | 7.1 | Introduction                                                               | 117 |

|   |     | 7.1.1 Power Estimation Requirement and Challenges                          | 117 |

|   |     | 7.1.2 Contribution                                                         | 121 |

|   |     | 7.1.3 Chapter Organization                                                 | 122 |

|   |     | 7.1.4 Previous Work on Power Estimation                                    | 122 |

|   | 7.2 | Background on Binary Integer Linear Program                                | 124 |

|   | 7.3 | Power Estimation Considering Zero-delay Model: Formulation of BILP Problem | 125 |

|   |     | 7.3.1 Input Output Constraints                                             | 126 |

|   |     | 7.3.2 Linearization Constraint                                             | 126 |

|   |     | 7.3.3 Toggle Constraints                                                   | 127 |

|   |     | 7.3.4 Objective Function                                                   | 127 |

|   |     | 7.3.5 Example                                                              | 128 |

|   | 7.4 | Evaluation on ISCAS-85 Circuits                                            | 130 |

|   | 7.5 | Summary of Zero-Delay ILP Methodology                                      | 133 |

|   | 7.6 | Level-Accurate Power Estimation: Methodology                               | 133 |

|   |     | 7.6.1 Leveling of the Circuit                                              | 133 |

|   |     | 7.6.2 Power Estimation Methodology                                         | 134 |

|   | 7.7 | Formulation of Level-BILP                                                  | 135 |

|   |     | 7.7.1 Computation of Maximum Peak Activity                                 | 137 |

|   | 7.8 | Evaluation on ISCAS-85 Circuits for Level-accurate BILP                    | 137 |

|   | 7.9 | Conclusion and Future Work                                                 | 139 |

| 8 | Cor | nclusion and Future Work                                                   | 140 |

| č | 8.1 | Contributions                                                              | 141 |

|   | 8.2 | Future Work                                                                | 144 |

|   | -   |                                                                            |     |

| Α | Exp | perimental Setup and Tools                                                 | 147 |

# List of Tables

| 3.1  | Scan patterns and Original scan order                                          | 41  |

|------|--------------------------------------------------------------------------------|-----|

| 3.2  | Computed TVW and RVW                                                           | 42  |

| 3.3  | Specification of ITC-99 (b04 to b10) and ISCAS-89 Benchmark Circuits           | 49  |

| 3.4  | Experimental results for peak power minimization                               | 50  |

| 4.1  | Demonstration of basic idea                                                    | 55  |

| 4.2  | C-X and X-C pair indicator bit array                                           | 57  |

| 4.3  | Experimental Results on ISCAS-89 Ckts                                          | 66  |

| 5.1  | Joint-scan Modes of operation                                                  | 75  |

| 5.2  | Circuit specification of S-ISCAS-89 benchmark                                  | 80  |

| 5.3  | JScan: P-random and P-serial size in #SFF                                      | 81  |

| 5.4  | Peak and Average Power of JScan in comparison with MSS[77]                     | 81  |

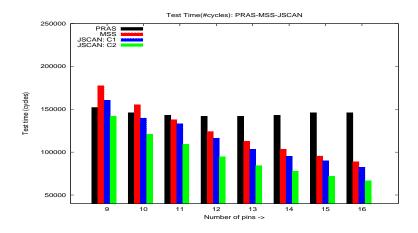

| 5.5  | Test time in contrast with PRAS[10] and MSS[77]                                | 83  |

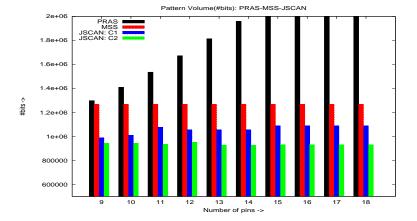

| 5.6  | Pattern volume in contrast with PRAS[10] and MSS[77]                           | 84  |

| 5.7  | Routing wire length of JScan, PRAS, and MSS                                    | 85  |

| 5.8  | Variation in loading/unloading time                                            | 88  |

| 5.9  | Circuit specification of S-ISCAS89 benchmark                                   | 95  |

| 5.10 |                                                                                | 96  |

| 5.11 | Test time of 2M-JScan in contrast with JScan[110], PRAS[10] and MSS[77]        | 97  |

| 5.12 | Test data volume of 2M-JScan in contrast with JScan[110], PRAS[10] and MSS[77] | 98  |

| 5.13 | Possible Variants of Joint-scan                                                | 98  |

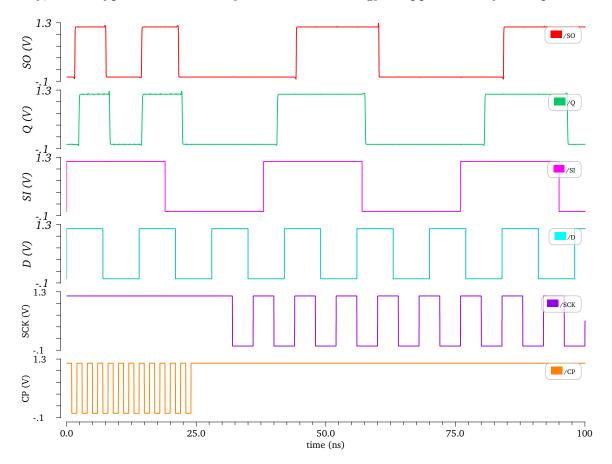

| 6.1  | Post Layout Timing Simulation Results at $500MHz$                              | 114 |

| 7.1  | Properties of ISCAS-85[47] Benchmark Circuits                                  | 131 |

| 7.2  | % of toggling nets as computed by CPLEX solver                                 | 132 |

| 7.3  | Summary of BILP as presented in Section-7.3                                    | 135 |

| 7.4  |                                                                                | 138 |

# List of Figures

| 1.1 | Dynamic and leakage power phenomena in CMOS inverter                                           | 3   |

|-----|------------------------------------------------------------------------------------------------|-----|

| 1.2 | Basic test procedure                                                                           | 9   |

| 1.3 | VLSI design flow [119]                                                                         | 10  |

| 1.4 | Block diagram of basic serial scan architecture                                                | 12  |

| 1.5 | Random access scan architecture                                                                | 13  |

| 1.6 | The power dissipation phenomena during shift cycle of scan test, Shft-i indicates the $i^{th}$ |     |

|     | shift cycle. 1 - 0 or 0 - 1 changes in $i^{th}$ and $i + 1^{st}$ cycle in corresponding sff    |     |

|     | indicates the switching.                                                                       | 15  |

| 1.7 | Power dissipation during last shift cycle for stuck-at and LOS test                            | 16  |

| 1.8 | Capture power dissipation (two toggles), Hamming distance between stimuli and response         | 16  |

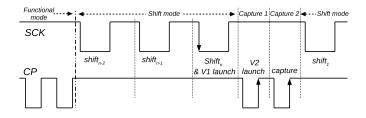

| 3.1 | Timing digram for at-speed scan testing                                                        | 38  |

| 3.2 | Basic principle of scan reordering                                                             | 39  |

| 3.3 | A complete vector-weighted graph                                                               | 41  |

| 3.4 | Hamiltonian cycle from Algorithm Part-1                                                        | 45  |

| 4.1 | A complete weighted graph constructed from Table-4.1                                           | 59  |

| 4.2 | A complete directed weighted graph constructed from Table-4.1                                  | 64  |

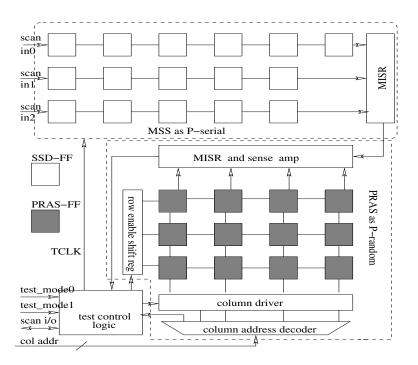

| 5.1 | The Proposed Joint-scan Architecture (the JScan)                                               | 73  |

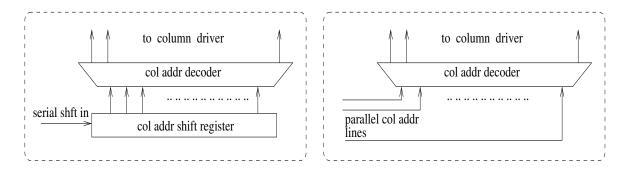

| 5.2 | Serial address shift register for PRAS using only one address pin                              | 73  |

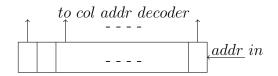

| 5.3 | State transition machine for mode control: where, $Q_j$ is Joint-scan mode, $Q_r$ is Random    |     |

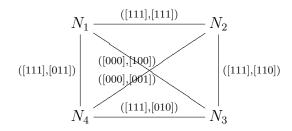

|     | mode, $Q_s$ is Serial mode, and $Q_f$ is functional mode                                       | 76  |

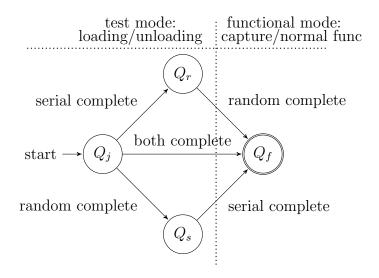

| 5.4 | Two configuration of JScan with respect to column address application                          | 82  |

| 5.5 | Test time behaviour for s-s15850 circuit over number of pins                                   | 83  |

| 5.6 | Patten volume variation for s-s15850 circuit over number of pins                               | 84  |

| 5.7 | Proposed scan Architecture (the 2M-JScan)                                                      | 87  |

| 5.8 | Two states controller: $Q_t$ for load/unload and launch of test, $Q_f$ for response capture    |     |

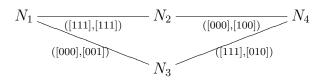

|     | and normal function                                                                            | 91  |

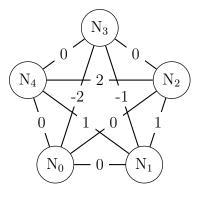

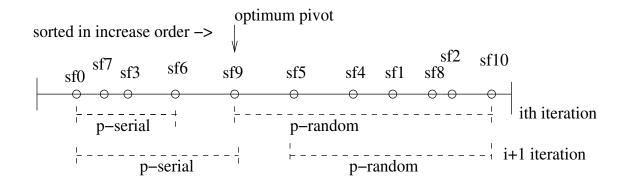

| 5.9 | Graphical demonstration of 1D clustering algorithm                                             | 94  |

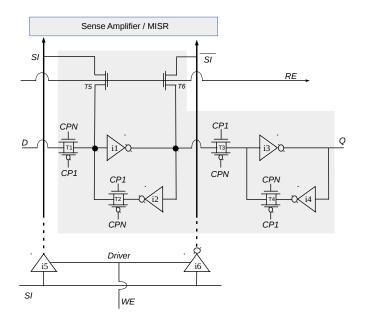

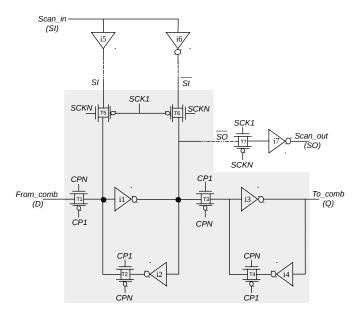

| 6.1 |                                                                                                | 103 |

| 6.2 |                                                                                                | 105 |

| 6.3 |                                                                                                | 107 |

| 6.4 | ·                                                                                              | 110 |

| 6.5 |                                                                                                | 111 |

| 6.6 |                                                                                                | 112 |

| 6.7 |                                                                                                | 113 |

| 6.8 | Post layout timing waveform at 500MHz                                                          | 115 |

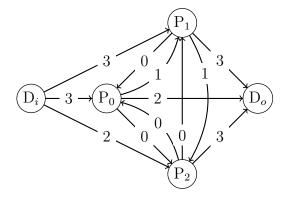

| 7.1 | Demonstration circuit for ILP formulation with zero-delay model                                | 128 |

### LIST OF FIGURES

| 7.2   | Group of gates leveled based on the circuit depth | 134     |

|-------|---------------------------------------------------|---------|

| • • 4 | Group of gates revered based on the chedit depth  | <br>101 |

## Chapter 1

## Introduction and Motivation

The thesis primarily concentrated on two problems: 1) power issues in System-on-Chips (SoCs) during test and 2) worst case power estimation problem. The severity of scan test power issue is discussed with respect to modern SoC designs. The need and challenges of estimating worst case power is also discussed. This chapter introduces the problem of interest and gives a back ground on power dissipation in VLSI circuit and scan architecture.

### **1.1** Introduction

Moore's prediction has triggered a lot of changes in VLSI technology [53, 74]. The down scaling of device size has brought up number of innovations and along with that a set of challenges. Designs are getting complex with multiple number of functions being integrated in a single chip. Realizing such complex design is itself a challenging task. Three parameters have been at forefront of the design consideration. Performance and area have been driving the design from last few decades or so. Recently the power has gained utmost important as one of the critical design parameters. Low power design has become now a mandatory practice for modern designs across all the application domains [20, 35]. Testing being a mandatory phase of VLSI design flow (at least for critical application areas), it has witnessed a set of challenges due to the power consumption during test

process, particularly in scan based testing[21, 43]. The power consumption in general is measured in terms of three power metrics: 1) Energy, 2) Average power and 3) Peak power

Among these three, the average and peak power causes critical issues particularly during test. The average power causes thermal related issues where as the peak power causes timing related issues. How are these problems so different that they need special attention during testing? Why is the power aware design not suffice to tackle these problems? How and why the power consumed during test operation is considerably large compared to the functional power? All these questions are natural to be asked. The test researchers have investigated these questions and pin pointed the problems which requires research effort to come up with appropriate solutions. Section-1.2 and 1.3 discusses the problems in detail. First part, Chapter-3, Chapter-4, Chapter-5, and Chapter-6 of this thesis address these problems. Second part, Chapter-7,addresses the worst case power estimation problem.

Estimation of worst case power plays an important role in fixing crucial design parameters related to power distribution network and power dissipation in general[124]. For test, the worst case power estimation render a help in understanding the upper limit on power which further can be used to determine the safe power zone for the design under test[114]. Therefore, the problem have attracted a good amount efforts to fix the challenges in power estimation. There are two related challenges associated with the power estimation: 1) maintaining accuracy, and 2) consuming minimum possible computation time. Two directions have been explored, one is dynamic power estimation and the other is static power estimation. We have explored the dynamic power estimation with an objective of maintaining accuracy with reasonable amount of computational time. Section-1.4 gives a detail understanding of the problem and related definitions.

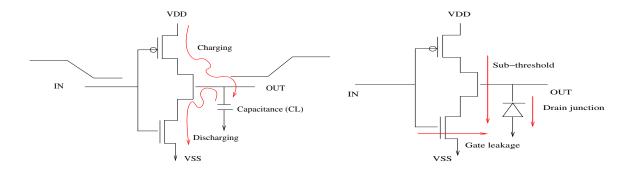

(a) Dynamic power dissipation in CMOS inverter

(b) Leakage power dissipation in CMOS inverter

Figure 1.1: Dynamic and leakage power phenomena in CMOS inverter

## 1.2 Power Dissipation in VLSI Circuit

Power dissipation in digital CMOS circuit is caused by four sources [81]:

- The *leakage current*, which is primarily determined by the fabrication technology, consists of two components: 1) reverse bias current in the parasitic diodes formed between source and drain diffusions and the bulk region in a MOS transistor, and 2) the sub-threshold current that arises from the inversion charge that exists at the gate voltages below the threshold voltage.

- The standby current, which is the DC current drawn continuously from  $V_{DD}$  to ground.

- The *short-circuit* (rush-through) current, which is due to the DC path between the supply rails during output transitions

- The *capacitance current*, which flows to charge and discharge capacitive loads  $(C_L)$  during logic changes.

The above sources of power dissipation are explained briefly in the following sections.

### **1.2.1** Dynamic Power Dissipation

The *dynamic power* is defined as the sum of *capacitive* and *short-circuit* power dissipations.

Each time the capacitor  $C_L$  gets charged through the PMOS transistors as shown in Figure-1.1(a), it's voltage rises from 0 to  $V_{DD}$ , and a certain amount of energy is drawn from the power supply. Part of this energy is dissipated in PMOS device, while the remainder is stored on the load capacitor. During the high-to-low transition, this capacitor is discharged, and the stored energy is dissipated in the NMOS transistor.

The energy  $E_{VDD}$ , taken from the supply during the transition, as well as the energy  $E_C$ , stored on capacitor at the end of the transition, can be derived by integrating the instantaneous power over the period of interest. Equation 1.1 and 1.2 show the energy drawn from  $V_{DD}$  and the actual energy stored in  $C_L$  respectively. For these equations it is assumed that the NMOS and PMOS devices are never on simultaneously.

$$E_{VDD} = \int_0^\infty i_{VDD}(t) V_{DD} dt = V_{DD} \int_0^\infty C_L \frac{dv_{out}}{dt} dt = C_L V_{DD} \int_0^{V_{DD}} dv_{out} = C_L V_{DD}^2$$

(1.1)

and

$$E_{C} = \int_{0}^{\infty} i_{VDD}(t) v_{out} dt = \int_{0}^{\infty} C_{L} \frac{dv_{out}}{dt} v_{out} dt = C_{L} \int_{0}^{V_{DD}} v_{out} dv_{out} = \frac{C_{L} V_{DD}^{2}}{2} \quad (1.2)$$

From above equations it can be observed that the energy stored at  $C_L$ ,  $E_C$  is half the energy supplied at  $V_{DD}$ ,  $E_{VDD}$ . This means that only half of the energy supplied by the power source is stored on  $C_L$ . The other half has been dissipated by the PMOS transistor. During the discharge phase the charge is removed from the capacitor, and its energy is dissipated in the NMOS transistor. In summary, each switching cycle (consisting of an low-to-high and high-to-low transition) takes a fixed amount of energy, equal to  $C_L V_{DD}^2$ . In order to compute the power consumption, we have to take into account how often the device is switched. If the gate is switched on and off  $f_{0\to 1}$  times per second, the power (dynamic) consumption is given by

$$P_{dyn} = C_L V_{DD}^2 f_{0 \to 1} \tag{1.3}$$

For a complex circuit, the equation for dynamic power, Equation 1.3, can be rewritten as

$$P_{dyn} = C_L V_{DD}^2 P_{0 \to 1} f \tag{1.4}$$

where f is the maximum possible event rate of the inputs (which is often the clock rate) and  $P_{0\to 1}$  the probability that a clock event results in a  $0 \to 1$  event at the output of the gate [86].

**Power Dissipation due to Direct Path Current:** The direct-path power is dissipated when both PMOS and NMOS transistor are conducting the current. This power is directly proportional to the switching activity similar to the capacitive power dissipation [86].

During testing the dynamic power is the primary concern. Reason being, the circuit has to be activated during the test operations. The activity that takes place during test are much more higher than the normal functional activity. Invariably all the experiment carried out till date reports that peak and average test power are around 30% and 6% more than the functional power[27, 57, 122]. However since the test process does not play any role distinctly in either increasing or decreasing the static power, it is not a critical issue for test.

### 1.2.2 Static Dissipation

The term *static power* (or steady-state power) dissipation refers to the sum of leakage and standby dissipations. The static power dissipation is expressed by the relation

$$P_{stat} = I_{stat} V_{DD} \tag{1.5}$$

where  $I_{stat}$  is the current that flows between the supply rails in the absence of switching activity.

Ideally, the static current of the CMOS inverter is equal to zero, as the PMOS and NMOS are never on simultaneously in steady-state operation. However, there is a leakage current flowing through the reverse-biased diode junctions of the transistor, located between the source and drain of the substrate. This contribution is, in general, very small and can be ignored.

An emerging source of leakage current is the sub-threshold current of the transistor, in Figure-1.1(b) this is shown as **sub-threshold** from PMOS to NMOS. The sub-threshold current increases as the threshold voltage approaches towards zero volt and the larger the static power consumption [86].

The emerging DSM (deep sub micron) technology has brought the concern for static power dissipation. The static power dissipation is now becoming a major concern for devices at 0.1 micron or below [58].

Though during test the leakage power is not a major concern the knowledge about the leakage power dissipation has to be considered while designing a design-for-test (DFT) circuitry. Nevertheless, there are few efforts been made to consider the leakage during test of VLSI circuitry[60].

#### **1.2.3** Metrics to Measure Power

**Energy:** Definition: The total switching activities generated during the period of test application. Energy affects the battery lifetime during power up or periodic self-test of battery-operated devices[39].

Average power: Definition: Average power is the total dissipation of power over a given time period. The ratio of energy to test time gives the average power. Elevated average power increases the thermal load that must be vented away from the device under test to prevent structural damage (hot spots) to the silicon, bonding wires, or package[83, 86]. **Instantaneous power:** Definition: Instantaneous power is the amount of power consumed at any given instant. Usually, it is defined as the power consumed right after the application of a synchronizing clock signal. Elevated instantaneous power might overload the power distribution systems of the silicon or package, causing brown-out<sup>1</sup>[83, 86].

**Peak power:** Definition: The highest power value at any given instant. Peak power determines the components thermal and electrical limits and system packaging requirements. If peak power exceeds a certain limit, designers can no longer guarantee that the entire circuit will function correctly. In fact, the time window for defining peak power is related to the chips thermal capacity, and forcing this window to one clock period is sometimes just a simplifying assumption. For example, consider a circuit that has a peak power consumption during only one cycle but consumes power within the chips thermal capacity for all other cycles. In this case, the circuit is not damaged, because the energy consumed will not be enough to elevate the temperature over the chips thermal capacity limit (unless the peak power consumption is far higher than normal). To damage the chip, high (not only highest) power consumption must last for several cycles [39, 81]. The peak power during test is a serious concern to avoid false test. Due to IR-drop effect the timing test fall in risk of false test[101].

Weighted Tansition Metric (WTM): The weighted transition metric is an abstraction level power model to approximate the power dissipation with scan chain activity. It is a common practice to approximate the circuit power dissipation with the scan chain activity in test. It has been established experimentally that the switching activity that takes place in each of the flip-flop is linearly correlated with the whole circuit activities[102].

In this thesis the main focus has been on to minimize peak and average dynamic power dissipation during test and to estimate the worst case peak and average dynamic

<sup>&</sup>lt;sup>1</sup>A phenomena that arises due to excessive drop in power supply voltage, this leads to unexpected reseting or rebooting of the device

power dissipation. We have used the WTM method to compute the peak and average switching activity. The WTM method is time efficient and it gives an value which is proportional to the actual circuit power[102].

### 1.3 Testing of VLSI Circuit

Following the Moore's law, the number of transistors in an IC has doubled every 18 months. In the 1980s, the term "VLSI" was used for chips having more than 100,000 transistor and that has continued to be used over time to refer to chip with millions of transistors. In 1986, the first megabits random access memory(RAM) contained more than 1 million transistors was fabricated. Microprocessors produced in 1994 contained more than 3 million transistors. VLSI devices with many millions of transistor are commonly used in the modern computers and electronic devices. This is a direct result of the down scaling of transistor size, referred as **feature size**. The reduction in feature size has also resulted in increased operating frequencies; for example, in 1971, the first microprocessors runs a clock frequency of 108 KHz, while current commercially available microprocessors commonly run at several gigahertz, currently highest being the 5 GHz in IBM Power PC.

The reduction in feature size increases the probability that a manufacturing defect in the IC will result in a faulty chip. A very small defect can easily result in a faulty transistor or interconnecting wire when the feature size is less than 100 nm. Furthermore, it takes only one faulty transistor or wire to make the entire chip fail to function properly or at the required operating frequency. Yet, defects created during the manufacturing process are unavoidable, and, as a result, some number of ICs is expected to be faulty; therefore, testing is required to guarantee fault-free products, regardless of whether the product is VLSI device or an electronic system composed of many VLSI devices. It is also necessary to test components at various stages during the manufacturing process. There is general agreement with the **rule of ten**, which says that the cost of detecting a faulty IC increases by an order of magnitude as we move through each stage of manufacturing, from device level to board level to system level and finally to system operation in the field.

Electronics testing includes IC testing, PCB testing, and system testing at the various manufacturing stages and, in some cases, during system operation. Testing is used not only to find the fault free devices, PCBs, and system but also to improve production yield at the various stages of manufacturing by analyzing the cause of defects when faults are encountered. In some systems, periodic testing is performed to ensure fault-free system operation and to initiate repair procedures when faults are detected. Hence, VLSI testing is important to designers, product engineers, test engineers, managers, manufacturers, and end-users.

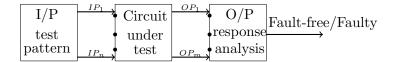

### 1.3.1 VLSI Design and Test Flow

Testing of a VLSI circuit typically consist of applying a set of test vector at the input of the circuit while the response at the circuit output are analyzed. Circuit that gives the wrong response is considered to be the faulty chip where as the circuit with correct response is considered as the fault free circuit. The Figure 1.2 illustrates the basic test procedure. The input test patterns are generated either by automatic test pattern generator (ATPG) or by random process. The response at output are compared with the predetermined response, if the response are correct for all the test then the circuit under test is declared as fault-free circuit otherwise the circuit is faulty.

Figure 1.2: Basic test procedure

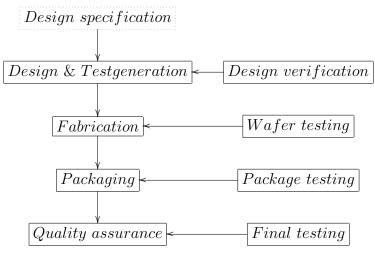

Testing plays an important role in VLSI design flow. The design has to be tested and verified after each design phase, hence the testing is performed at each phase of design flow. VLSI design flow consist of mainly following phases: 1. Design specification 2. Design 3. Fabrication 4. Packaging 5. Quality assurance. In Figure 1.3 the overall design flow is illustrate with corresponding test requirement. The figure show that the testing in some form is needed in each phase of design flow. The first phase of design is to specify the design requirement. Once the specification is documented the next phase is to design and synthesize the circuit to generate net-list for further processing. At this stage of design the functionality of the circuit has to be verified (modern formal verification technique are used in general) against the given design specification.

Once the design is verified with zero design bugs the next phase is to perform the automatic test pattern generation (ATPG) for test. Once the pattern generation is completed the net-list will go for fabrication. In between these two steps are placement and routing. Once the fabrication is completed the ICs are tested to determine the defective devices. The chip that passes the wafer test is then extracted and packaged. To eliminate some of the chip with defective package a testing is performed again. Finally the chip which passes both wafer test and package test are tested for quality assurance. This final testing includes the important parameter like input/output timing, voltage, and current. In addition to above described testing, chip is also tested in high temperature which is known as burn-in test which accelerated the test by stressing the device.

Figure 1.3: VLSI design flow [119]

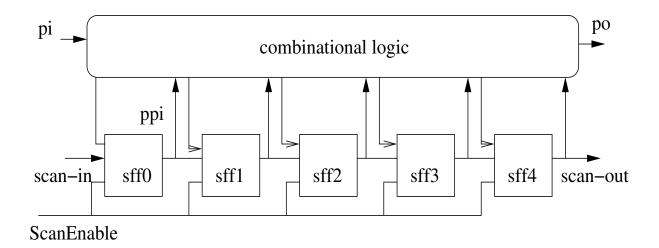

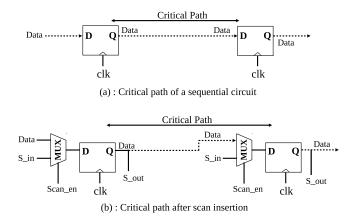

### **1.3.2** Scan Architecture and Scan Testing

Scan based testing is one of the widely used design-for-test (DFT) technology. The motivation behind the scan design based approach is to improve the testability of a circuit by improving the controllability and observability. In scan design the sequential elements, the flip-flops, are converted in to scan flip-flop and these are connected as serial shift register to form a scan chain as shown in Figure-1.4. Now, the test pattern for the given sequential circuit can be generated using combinational automatic test pattern generation (ATPG). The standard serial scan design operates in two modes [119]:

| Normal functional mode | Test mode        |

|------------------------|------------------|

| Functional operation   | Shift operation  |

| Response capture       | Launch operation |

In normal mode, all the test related signals are disabled and the circuit is operated in functional mode. In shift mode, scan test vector are shifted in to the scan chain and the test response are shifted out simultaneously. In launch mode, the shifted in test vector are applied to the combinational block. The response are captured while circuit is in normal functional mode.

#### Serial Scan Architecture:

Among the many varieties of scan architectures, the *full serial scan design*(loosely known as simply "full scan design"), *partial serial scan design* (or just partial scan design), and *random access scan design* (*RAS*) are the basic scan designs.

In full-scan architecture all the sequential cells are used as scan cells. The full-scan architecture can be implemented using *multiplexed scan D flip-flop (MSDFF), clocked-scan cells, LSSD (Level sensitive scan design) scan cells* and the recently proposed mixed-mode scan flip-flop (detail is given in Chapter-6). Full-scan design provides the advantage of achieving highest possible fault coverage for a given ATPG algorithm compared to any other variation of its. The main disadvantage of full scan design is longer test application

Figure 1.4: Block diagram of basic serial scan architecture

time and excessive toggling in scan cells as it requires serial shift operation. Some of the alternative design, some what better in test application time and power dissipation, are partial scan design and random access scan (RAS).

Unlike full-scan design where all the sequential cells are used as scan cells, partialscan design requires only a subset of the sequential cells to be used as scan cells in scan chain. It can also be implemented using *multiplexed D flip-flop*, *clocked-scan cells*, *and LSSD (Level sensitive scan design) scan cells*. The test pattern for partial-scan design can either be generated by combinational ATPG or by sequential ATPG.

### **Random Access Scan Architecture:**

Full-scan and partial-scan design are based on serial shift operation. The serial shift operation creates a lot of switching in scan cells which causes the excessive power dissipation. To avoid excessive power dissipation an alternative scan architecture was proposed by Ando in 1980 called random access scan (RAS). The basic idea in RAS is to access only one scan flip-flop at a time without disturbing or switching other scan flip-flops. Thus, RAS reduces the power drastically. The architecture of RAS is similar to the RAM (random access memory), to write a test data into a scan flip-flop, first the flip-flop has to be enabled by row and column address then the data has to be written. Similarly for

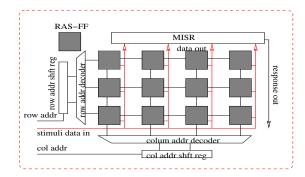

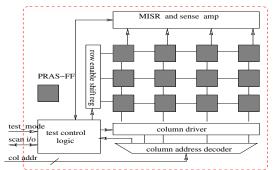

(a) Basic random access scan architecture (RAS)

(b) Progressive random access scan architecture (PRAS)

Figure 1.5: Random access scan architecture

reading the response. Two most commonly referred RAS architectures, the simplest random access scan and progressive random access scan, are shown in Figure-1.5. Chapter-5 elaborate the detail functions of RAS architecture and its advantages and disadvantages.

### Scan Testing(Fault Models and Test Procedures)

**Stuck-at fault Testing:** The stuck-at fault testing is performed to test the stuck-at faults. This type of testing can be categorized into two types: internal testing and external testing. In case of internal testing the test related operation is performed using BIST (Built-In Self-Test) whereas in case of external testing ATPG and ATE (Automatic Test Equipment) are used.

The stuck-at testing for scan design (circuit with scan chain) consist of four basic phases: *Test generation* carried out by ATPG, *test application, response capture* and *response comparison*, all are performed by ATE. The test application step involves the shifting in and launching of test pattern. During shift operation the SE (Scan Enable) signal is kept high so that the circuit can operate at scan mode. The shift operation is performed at slow clock rate generally half the functional clock. This slow shifting is performed to guarantee the average power consumption below the specified limit. Once the test patterns are shifted in, the primary input patters are applied and the SE signal is disabled so that the circuit can now operate in normal mode. In the normal mode operation the responses from the combinational circuit are captured in scan flip flop. The capture operation of stuck-at fault testing is performed at slow clock rate. Once the responses are captured they are shifted out while shifting in another test pattern. The shifted out responses are compared with the previously generated golden responses by ATE for circuit to be declared as faulty or fault free.

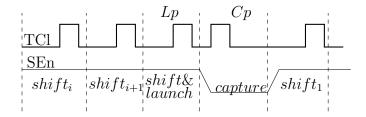

Skewed-load Delay Testing: Unlike the stuck-at fault testing, the delay testing requires a test vector pair  $\langle V_1, V_2 \rangle$  to be applied to test a set of delay faults. The first vector  $V_1$  of the pair is used to set the circuit to an initial state and the second vector  $V_2$  is used to launch the transition. The second vector  $V_2$  of the delay test pair is one bit shift over the first vector  $V_1$  in the pair. The capture cycle for this test application is now divided into two pulse: launch and capture pulse. In launch pulse the transitions are launched by the application of  $V_2$ . The SE signal is now disabled and the capture operation is performed at functional clock speed [98]. Once the responses are captured they are shifted out while shifting in new test pattern. Finally the shifted out responses are compared with the golden responses. This method is also referred to as Launch-on-Shift (LOS) test.

One of the difficulty in skewed-load scan methodology is timing critical consideration of SE signal [68]. The power related problem that arises during the at-speed testing is discussed in Section 3.

**Broad-side Delay Testing:** A broad-side delay testing is a form of a scan-based delay testing, where the first vector  $V_1$  of the pair  $\langle V_1, V_2 \rangle$  is applied to the scan chain to initialize the chain and the test vector  $V_2$  is applied to launch the transitions. The vector  $V_2$  of the pair is the combinational circuits response to the first vector  $V_1$ . This form of delay testing is called as broad-side since the second vector of the delay test pair is provided in a broad-side fashion, namely through the logic [99]. The broad-side test is

Figure 1.6: The power dissipation phenomena during shift cycle of scan test, Shft-i indicates the  $i^{th}$  shift cycle. 1 - 0 or 0 - 1 changes in  $i^{th}$  and  $i + 1^{st}$  cycle in corresponding sff indicates the switching.

advantageous over the the skewed-load test because in this case the signal SE is no more a timing critical due to an additional dead cycle which allow SE to settle [68]. This method of applying the test is also referred to as Launch-on-Capture (LOC) test.

### **1.3.3** Shift and Capture Power

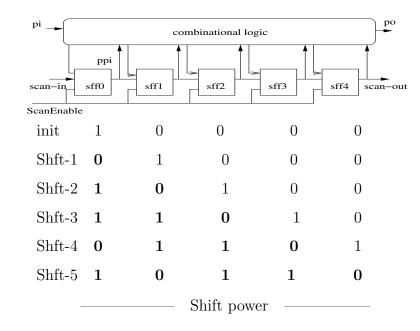

The scan testing involves shifts of test stimuli, a launch of stimuli, and a capture of response as discussed in Section 1.3.2. The shift operation shift-in and shift-out the test patterns and responses simultaneously. While shifting in and out the test patterns and responses the scan cells may changes their data in each shift clock cycles. The continuous changes of data in scan cells result in a large number of switching in combinational part of the design. This excessive switching causes the proportionate amount of dynamic power dissipation. The power dissipated during the scan operation can be called as "scan power". The scan power can be classified into two classes based on the scan period: 1) shift power and 2) capture power. Further, the shift power can be classified in 1) the

| scan chain $\rightarrow$ | sff0     | sff1         | sff2             | sff3            | sff4            |

|--------------------------|----------|--------------|------------------|-----------------|-----------------|

|                          |          |              |                  |                 |                 |

| second-last shift        | 0        | 1            | 1                | 0               | 1               |

| last shift               | 1        | 0            | 1                | 1               | 0               |

| Launch cycle (the        | e last s | hift) power  | dissipation(fo   | ur toggles) ir  | n stuck-at test |

| $V_1$                    | 1        | 0            | 1                | 1               | 0               |

| $V_2$                    | 0        | 1            | 0                | 1               | 1               |

| $V_2$ -launch cycle (    | the las  | t shift) pow | er dissipation   | (four toggles   | s) in LOS test  |

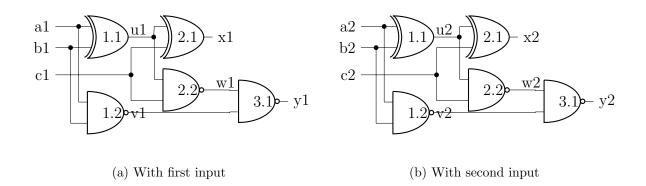

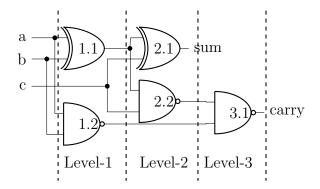

| Figure 1.7: Power        | dissip   | ation during | g last shift cyc | cle for stuck-a | at and LOS test |