## Architecting High Performance, Energy Efficient & Secured Multi-Core Systems

SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIRMENTS

OF THE DEGREE OF

Doctor of Philosophy

by

Nirmal Kumar Boran

(Roll No. 154050006)

Supervisors: **Prof Bernard Menezes Prof. Virendra Singh**

Department of Computer Science and Engineering Indian Institute of Technology Bombay Mumbai – 400076

AUGUST 2021

©Nirmal Kumar Boran AUGUST 2021 All rights reserved

Dedicated to

my gurus, my family, and friends

## Thesis Approval for Ph.D.

The thesis entitled Architecting High Performance, Energy Efficient & Secured Multi-Core Systems is approved for the degree of Doctor of Philosophy.

Co-supervisor Supervisor Co-supervisor Chairman

Date:

Place:

Examiners

## **Declaration**

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the Institute and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

(Signature)

Nirmal Kumar Boran 154050006

Date: 30-08-2021

# Acknowledgements

It gives me immense pleasure to express my sincere thanks and gratitude to all those who have kindly helped me in carrying out this research work. I express my deepest gratitude to my advisors Prof. Virendra Singh & Prof Bernard Menezes. There guidance has instilled a sense of doing independent research in me. I will remain indebted to them for his guidance in all spheres of life.

## Publications

#### Included in Thesis

#### Peer reviewed conferences

- Nirmal Kumar Boran, Dinesh Kumar Yadav, and Rishabh Iyer, "Classification based scheduling in Heterogeneous ISA Architectures", VDAT -2020, (pp. 1-6) IEEE, https://ieeexplore.ieee.org/document/9190559

- Nirmal Kumar Boran, Dinesh Kumar Yadav, and Rishabh Iyer, "Performance Modelling and Dynamic Scheduling on Heterogeneous-ISA Multi-core Architectures ", VDAT -2019 (pp. 702-715), Springer, https://link.springer.com/ chapter/10.1007/978-981-32-9767-8\_58. Best paper award,

- Nirmal Kumar Boran, Rameshwar Prasad Meghwal, Kuldeep Sharma, Binod Kumar, and Virendra Singh. "Performance modelling of heterogeneous ISA multicore architectures." In 2016 IEEE East-West Design & Test Symposium (EWDTS), pp. 1-4. IEEE, 2016, https://ieeexplore.ieee.org/document/7807641

- Nirmal Kumar Boran, Kenrick Pinto, and Virendra Singh, "On Disabling Prefetcher to Amplify Cache Side Channels", VDAT 2021, 2021

- Nirmal Kumar Boran, Pranil Joshi, and Virendra Singh, "PASS-P: Performance And Security Sensitive Dynamic Cache Partitioning", *DATE 2022* [To be submitted]

#### Journal publications

- 6. Nirmal Kumar Boran, Shubhankit Rathore, Meet Udeshi, and Virendra Singh, "Fine-Grained Scheduling in Heterogeneous-ISA Architectures", *IEEE Computer* architecture letter, 2021, Volume: 20, Issue: 1, pp. 9 - 12, https://ieeexplore. ieee.org/document/9294082

- Nirmal Kumar Boran, Meet Udeshi, Shubhankit Rathore, and Virendra Singh, "HIDC- Heterogeneous ISA Dynamic Core architecture, *Transactions on Comput*ers [Submitted]

## Abstract

Multi-core architectures have the ability to enhance system's throughput, however single threaded programs' execution can not be improved by multi-core architectures. According to Amdahl's law, the performance of an application can be significantly hampered by the limited performance of a single threaded program. Given the ever increasing demand for improved computational capabilities, heterogeneous-ISA multi-core architectures have emerged as a promising alternative to improve single-threaded performance. Such architectures comprise of multiple cores that differ not just in micro-architectural parameters but also in their Instruction Set Architectures (ISAs). These architectures extract previously latent performance gains by executing different phases of the program on the core (and ISA) best suited to it, as opposed to executing the entire program on a single ISA. In such a computing paradigm, maximum performance can be extracted when we ensure that at every point in the program's execution, the program runs on the core best suited to it. If a program is divided into multiple phases, then scheduling of each phase has to be done at run time. While there have been prior works which have looked into heterogeneous ISA multi-core architectures, none of these works have addressed the problem of run time scheduling. To the best of our knowledge, we are the first one in looking into dynamic scheduling in heterogeneous ISA architectures. We have performed scheduling at both coarse-grained and fine-grained levels. In addition to this we also provide a low overhead migration framework which further improves the performance of heterogeneous ISAs. We achieve a speed up of 35% speed up with respect to state-of-art in coarse-grained scheduling. In fine-grained scheduling, we achieve speed up of 22 % on top of state-of-art coarse-grained scheduling.

For single threaded program, only one core of heterogeneous ISA multi-cores is active during the entire execution. The rest of the cores do not contribute anything to the performance of the single threaded program. On top of this, the idle cores keep dissipating static power leading to an overall increase in the power consumption of system. Hence, for single threaded programs having multiple cores leads to under utilization of resources. Also on affinity change within a program from one ISA to other, the program needs to be migrated to the other core which causes large migration overheads. To alleviate the issue of power consumption and migration overhead, we propose Heterogeneous-ISA dynamic core (HIDC) architecture. HIDC integrates support for multiple ISAs into a single dynamic core. HIDC is capable of dynamically changing its working ISA, while the program is under execution. Integrating multiple ISAs on the same core not only improves the energy efficiency but also significantly improves the performance of a single-threaded program. Since, HIDC is a single heterogeneous core, unlike multi-core heterogeneous systems, the migration overheads are reduced. The migration overhead is reduced  $100 \times$ with respect to state-of-art. We gain a speed up of 30~% with respect to state-of-art. The energy consumption is also reduced by 15% for HIDC architectures. With respect to state-of-art [99], multi-threaded programs achieve a performance gain of 16.2% in HIDC architectures.

In multi-core architectures the last level cache is shared. Though HIDC supports multiple ISAs in single core, however to improve the throughput, multiple HIDC can be used in a chip. Shared caches are vulnerable to side channel attacks. In this work, we show a side channel attack that can be mounted by disabling the prefetchers in multi-core systems. In addition to this, we also reveal the vulnerability in the utility based cache partitioning protocol. To mitigate side channel attacks, we propose PASS-P (Performance And Security Sensitive Protocol) to improve robustness against side-channel attacks. We are proposing a new cache replacement technique to overcome the performance concerns. The proposed work enhances the hardware security of the last level cache. With PASS-P, a performance gain of 7.2% relative to static partitioning is achieved, which is less then by just 0.35% relative to UCP[81].

Overall in this thesis, we investigate three important aspects in multi-core systems:

- 1. Improving Single-thread performance of the system.

- 2. Improving energy efficiency of the system.

- 3. Providing better hardware security.

# Keywords

Multi-core, Single-threaded program, Heterogeneous ISA, Dynamic migration, Dynamic scheduling, Scheduling technique, Coarsegrained scheduling, Fine-grained scheduling, Linear regression neural network, General regression neural network, Perceptron, Migration overhead, Dynamic core, Side-channel attacks, Primeprobe attack, Flush-reload attack, Cache partitioning, Static partitioning, Prefetchers, Stride prefetchers

# Notations and Abbreviations

| UCP     | : | Utility based Cache Partitioning                | HIDC                 | : | Heterogeneous ISA Dynamic Core     |

|---------|---|-------------------------------------------------|----------------------|---|------------------------------------|

| ISA     | : | Instruction Set Architecture                    | $\operatorname{CMP}$ | : | Chip Multiprocessor                |

| LRNN    | : | Linear Regression Neural Network                | ARF                  | : | Architectural register file        |

| GRNN    | : | General Regression Neural Network               | PRF                  | : | Physical register file             |

| HISACMP | : | Heterogeneous ISA Chip Multi Processor          | TLP                  | : | Thread level parallelism           |

| PASS-P  | : | Performance And Security Sensitive Partitioning | ILP                  | : | Instruction level parallelism      |

| DC      | : | Dynamic core                                    | HeMC                 | : | Heterogeneous multi-cores          |

| HLL     | : | High level language                             | HoMC                 | : | Homogeneous Multi-cores            |

| RISC    | : | Reduced Instruction Set Computer                | ROP                  | : | Return oriented programs           |

| CISC    | : | Complex Instruction Set Computer                | AES                  | : | Advanced Encryption Standard       |

| IQ      | : | Instruction Queue                               | RSA                  | : | Rivest, Shamir, Adleman            |

| ROB     | : | Reorder buffer                                  | MSHR                 | : | Miss Status handle registers       |

| LQ      | : | Load Queue                                      | SIMD                 | : | Single instruction multi data      |

| SQ      | : | Store Queue                                     | $\mathbf{PC}$        | : | Program counter                    |

| DCP     | : | Dynamic cache partitioning                      | SecDCP               | : | Secured Dynamic cache partitioning |

|         |   |                                                 |                      |   |                                    |

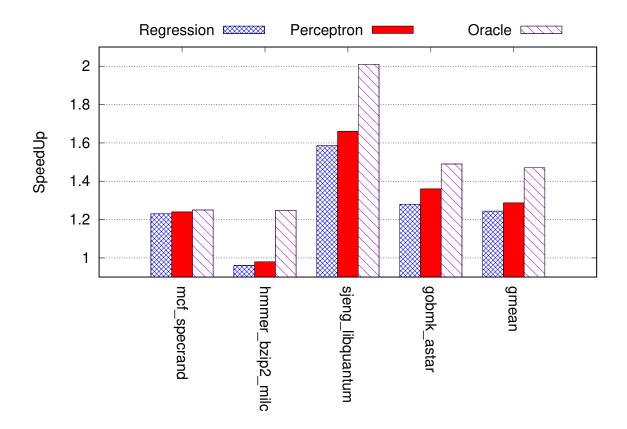

# Contents

| A        | cknov  | wledge  | ments                                                               | iii      |

|----------|--------|---------|---------------------------------------------------------------------|----------|

| P        | ublica | ations  |                                                                     | iv       |

| A        | bstra  | .ct     |                                                                     | vi       |

| K        | eywo   | rds     |                                                                     | ix       |

| N        | otati  | ons an  | d Abbreviations                                                     | x        |

| 1        | Intr   | oducti  | on                                                                  | <b>1</b> |

|          | 1.1    | Single- | threaded performance                                                | 2        |

|          |        | 1.1.1   | Coarse grained scheduling                                           | 4        |

|          |        | 1.1.2   | Finer-grained scheduling                                            | 6        |

|          | 1.2    | 00      | y efficient heterogeneous ISA dynamic core                          | 7        |

|          | 1.3    |         | ty in multi-core architectures                                      | 9        |

|          |        | 1.3.1   | Disabling prefetchers to attack side-channel attack                 | 10       |

|          |        | 1.3.2   | PASS-P: Performance and security sensitive partitioning protocol    | 10       |

|          | 1.4    |         | bution of the thesis                                                | 11       |

|          | 1.5    | Overvi  | iew of thesis                                                       | 12       |

| <b>2</b> | Pre    | vious V | Work                                                                | 13       |

|          | 2.1    | Multi-  | core architectures                                                  | 13       |

|          |        | 2.1.1   | Single ISA homogeneous multi-core architectures                     | 14       |

|          |        | 2.1.2   | Single ISA heterogeneous multi-core architectures                   | 16       |

|          |        | 2.1.3   | Heterogeneous-ISA multi-core architectures                          | 17       |

|          |        | 2.1.4   | Performance modelling and scheduling in heterogeneous architectures | 18       |

|          |        | 2.1.5   | Migration techniques in multi-core architectures                    | 20       |

|          |        | 2.1.6   | Dynamic core architectures                                          | 21       |

|          |        | 2.1.7   | Return oriented attacks                                             | 22       |

|          | 2.2    | Securi  | ty                                                                  | 22       |

|          |        | 2.2.1   | Different security attacks                                          | 23       |

|          |        | 2.2.2   | Mitigation of side channel attacks                                  | 24       |

|          |        | 2.2.3   | Prefetchers                                                         | 25       |

| 3 | Per | formance Modelling and Scheduling                                                                          | <b>27</b> |

|---|-----|------------------------------------------------------------------------------------------------------------|-----------|

|   | 3.1 | Performance estimation                                                                                     | 28        |

|   |     | 3.1.1 Execution time stack model                                                                           | 28        |

|   |     | 3.1.2 Inter ISA instruction count estimation                                                               | 29        |

|   |     | 3.1.3 Inter-ISAs miss events estimation model                                                              | 29        |

|   |     | 3.1.4 Inter-ISA queue full event count estimation                                                          | 31        |

|   |     | 3.1.5 Inter-ISA's core execution time estimation                                                           | 32        |

|   |     | 3.1.6 Results and analysis                                                                                 | 32        |

|   | 3.2 | Modified performance estimation                                                                            | 35        |

|   |     | 3.2.1 Extracting relevant parameters                                                                       | 36        |

|   |     | 3.2.2 Linear regression model                                                                              | 37        |

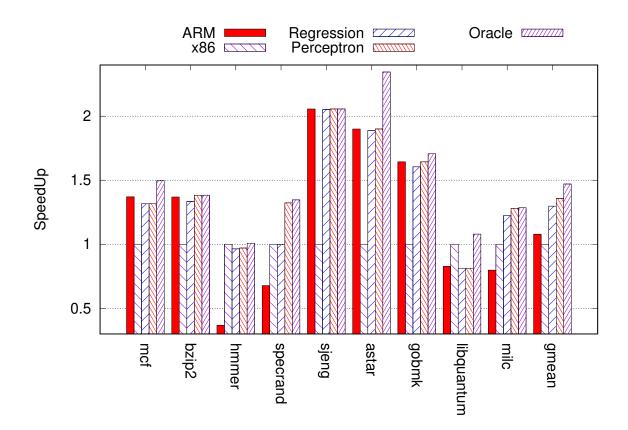

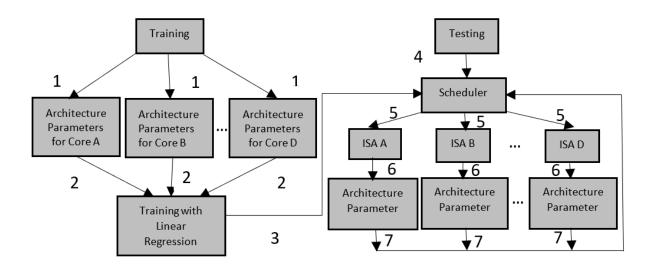

|   |     | 3.2.3 Scheduling                                                                                           | 38        |

|   |     | 3.2.4 Evaluation $\ldots$ | 40        |

|   |     | $3.2.5$ Methodology $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                         | 40        |

|   |     | 3.2.6 Results and analysis                                                                                 | 40        |

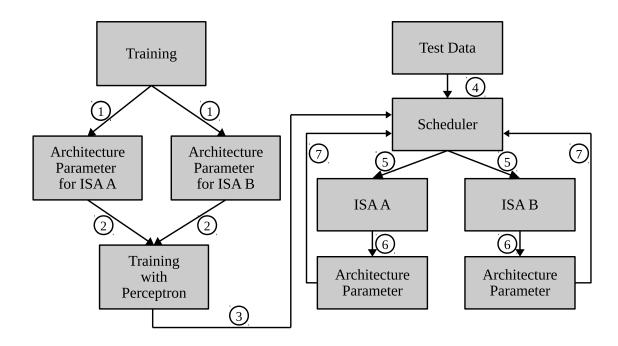

|   | 3.3 | Classification based scheduler                                                                             | 46        |

|   |     | 3.3.1 Scheduling model                                                                                     | 46        |

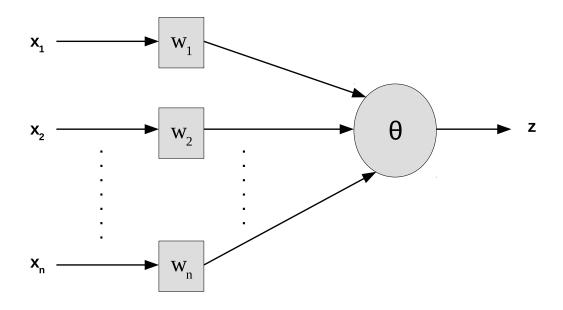

|   |     | 3.3.2 Perceptron classifier                                                                                | 46        |

|   |     | 3.3.3 Evaluation setup                                                                                     | 48        |

|   |     | 3.3.4 Results and analysis                                                                                 | 48        |

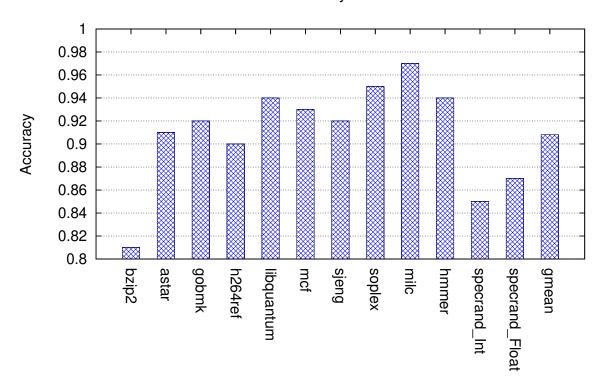

|   |     | 3.3.5 Perceptron classifier accuracy                                                                       | 49        |

|   |     | 3.3.6 Performance gain                                                                                     | 50        |

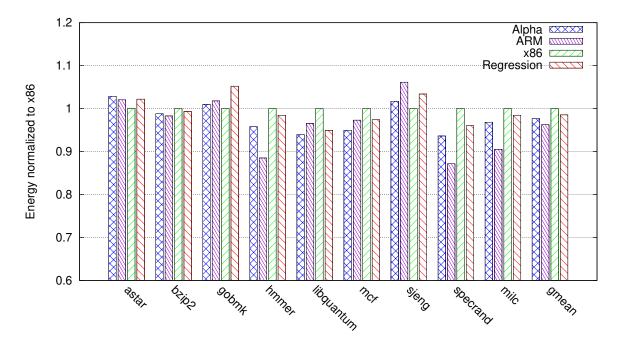

|   |     | 3.3.7 Energy efficiency results                                                                            | 51        |

|   |     | 3.3.8 Hardware overhead                                                                                    | 52        |

|   | 3.4 | Conclusion                                                                                                 | 53        |

| 4 | Fin | e Grained Scheduling                                                                                       | 54        |

|   | 4.1 | Motivation                                                                                                 | 55        |

|   | 4.2 | Fine-grained scheduling                                                                                    | 58        |

|   | 4.3 | Heuristics based scheduling approach                                                                       | 60        |

|   | 4.4 | Results and analysis                                                                                       | 63        |

|   |     | 4.4.1 Migration overhead                                                                                   | 63        |

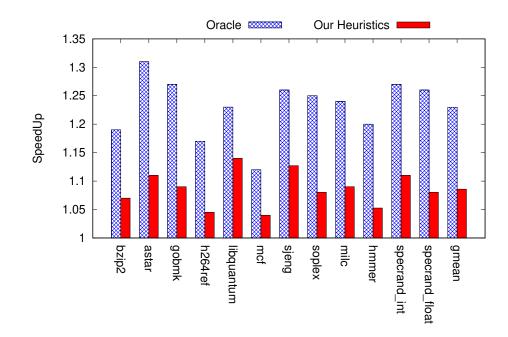

|   |     | 4.4.2 Performance results                                                                                  | 64        |

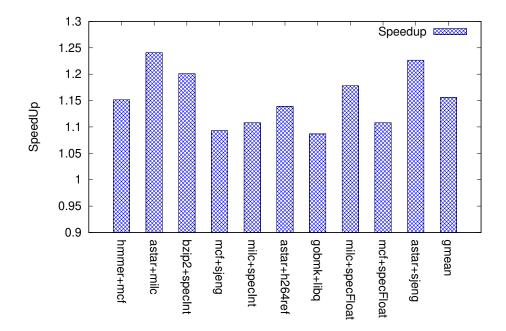

|   |     | 4.4.3 Performance results for multi-workload                                                               | 65        |

|   |     | 4.4.4 Hardware overhead                                                                                    | 66        |

|   | 4.5 | Security analysis                                                                                          | 67        |

|   | 4.6 | Conclusion                                                                                                 | 67        |

| 5 | нп  | OC Architecture                                                                                            | 68        |

| - | 5.1 | HIDC architecture                                                                                          | 70        |

|   | 5.2 | Scheduling                                                                                                 | 73        |

|   |     | 5.2.1 Extraction of micro-architectural parameters                                                         | 74        |

|   |     | 5.2.2 Scheduling model                                                                                     | 74        |

|   | 5.3 | Procedure for migration                                                                                    | 76        |

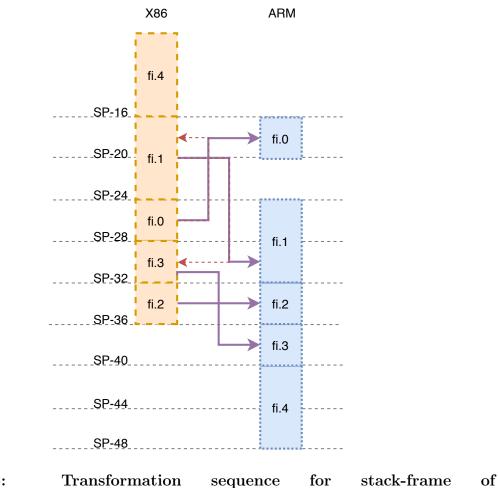

|   |            | 5.3.1   | Inplace stack transformation                                                                                                  |

|---|------------|---------|-------------------------------------------------------------------------------------------------------------------------------|

|   |            | 5.3.2   | Migration overhead reduction                                                                                                  |

|   | 5.4        | Hardw   | are implementation                                                                                                            |

|   | 5.5        | Result  | s and analysis                                                                                                                |

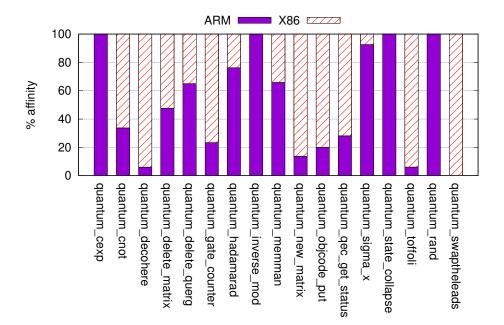

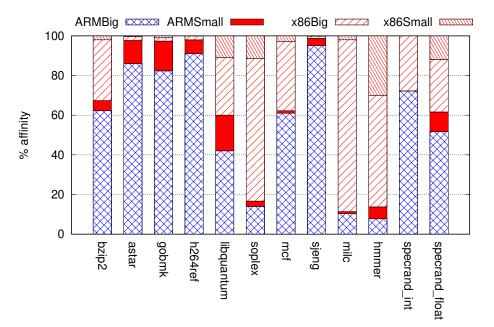

|   |            | 5.5.1   | Program's affinity towards different ISAs                                                                                     |

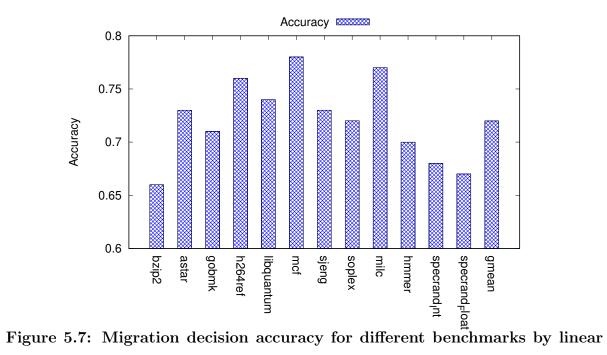

|   |            | 5.5.2   | Dynamic scheduling                                                                                                            |

|   |            | 5.5.3   | Migration overhead                                                                                                            |

|   |            | 5.5.4   | Performance and energy results for HIDC                                                                                       |

|   |            | 5.5.5   | Performance results for fine-grained scheduling                                                                               |

|   |            | 5.5.6   | Performance results for multi-workload                                                                                        |

|   |            | 5.5.7   | Area overhead                                                                                                                 |

|   | 5.6        | Conclu  | $sion \ldots \ldots$ |

|   |            |         |                                                                                                                               |

| 6 |            |         | Ilti-Core Architecture 95                                                                                                     |

|   | 6.1        | Prefete | chers are also vulnerable                                                                                                     |

|   |            | 6.1.1   | Attack vectors                                                                                                                |

|   |            | 6.1.2   | Attack methodology                                                                                                            |

|   |            | 6.1.3   | Results and analysis                                                                                                          |

|   | 6.2        | Cache   | partitioning                                                                                                                  |

|   |            | 6.2.1   | Vulnerability in dynamic partitioning                                                                                         |

|   |            | 6.2.2   | Threat model                                                                                                                  |

|   |            | 6.2.3   | Proposed mitigation technique: PASS-P                                                                                         |

|   |            | 6.2.4   | Security through Invalidation                                                                                                 |

|   |            | 6.2.5   | Reallocation policy for PASS-P                                                                                                |

|   |            | 6.2.6   | Results and analysis                                                                                                          |

|   | 6.3        | Conclu  | $sion \dots \dots$      |

| 7 | Con        | alusior | and Future Scope 120                                                                                                          |

| 1 | 7.1        |         | ary 120                                                                                                                       |

|   | 7.1<br>7.2 |         |                                                                                                                               |

|   | 7.2<br>7.3 |         |                                                                                                                               |

|   | 6.1        | ruture  | scope                                                                                                                         |

# List of Tables

| 3.1 | Core's configuration for modelling                          | 32  |

|-----|-------------------------------------------------------------|-----|

| 3.2 | Core configurations for LRNN based scheduler                | 41  |

| 3.3 | Core configurations for classification based scheduling     | 48  |

| 4.1 | Core configurations for fine-grained scheduling             | 62  |

| 5.1 | Micro-architectural parameters used for migration decision  | 75  |

| 5.2 | Memory System                                               | 76  |

| 5.3 | Stack slots and location mapping for BZ2_bzDecompressStream | 85  |

| 5.4 | Core configurations for HIDC                                | 88  |

| 6.1 | Simulation setup for prefetchers                            | 100 |

| 6.2 | Core configurations                                         | 116 |

# List of Figures

| 1.1 $1.2$ | Execution time of different phases of benchmark astar Execution time when the program is run on ARM, x86 and execution time when each phase is run on the core most suited to it ("Accurate mig") and least suited to it ("Inaccurate mig")       | 3<br>5 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

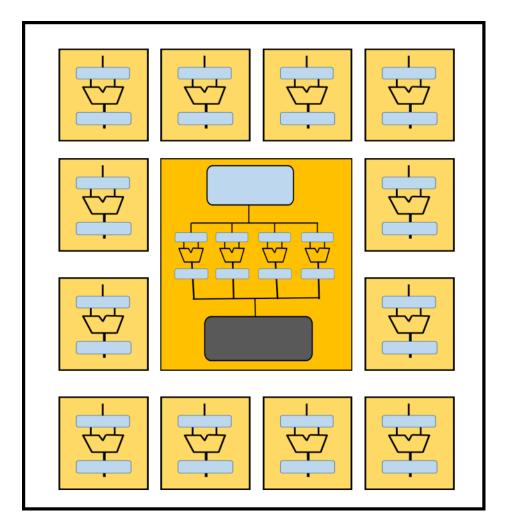

| 2.1       | Symmetric multi-core with 16 one-base core equivalent cores                                                                                                                                                                                       | 14     |

| 2.2       | Symmetric multi-core with four four-BCE cores                                                                                                                                                                                                     | 15     |

| 2.3       | Asymmetric multi-core with one four-BCE core and 12 one-BCE cores                                                                                                                                                                                 | 17     |

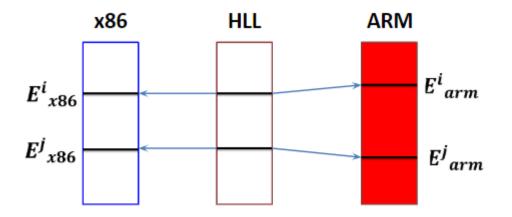

| 2.4       | Equivalence points                                                                                                                                                                                                                                | 20     |

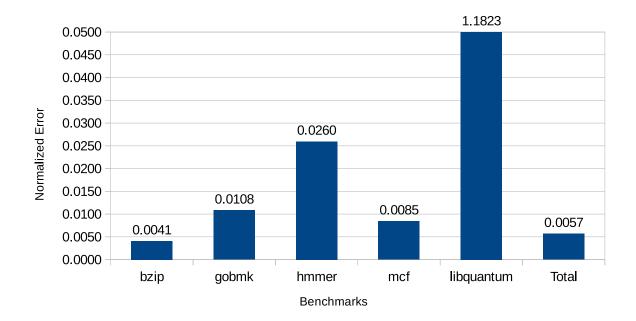

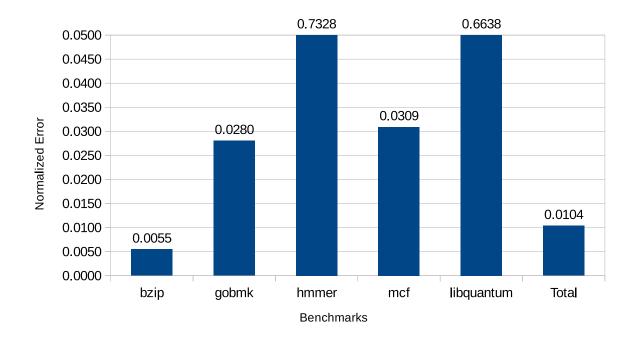

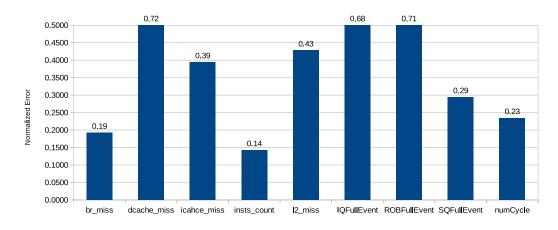

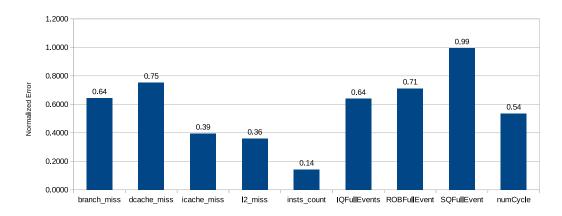

| 3.1       | ARM execution time stack model error                                                                                                                                                                                                              | 33     |

| 3.2       | X86 execution time stack model error                                                                                                                                                                                                              | 34     |

| 3.3       | Error in estimation from ARM to X86                                                                                                                                                                                                               | 35     |

| 3.4       | Error in estimation from X86 to ARM                                                                                                                                                                                                               | 35     |

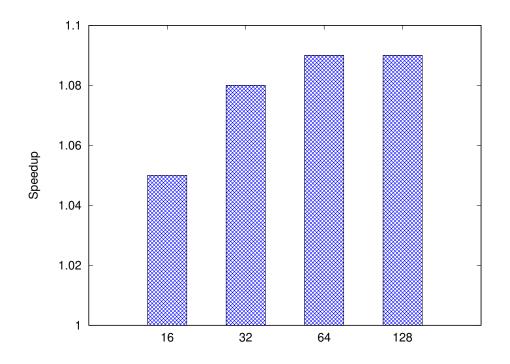

| 3.5       | Speedup on basis of small chunk of phase                                                                                                                                                                                                          | 39     |

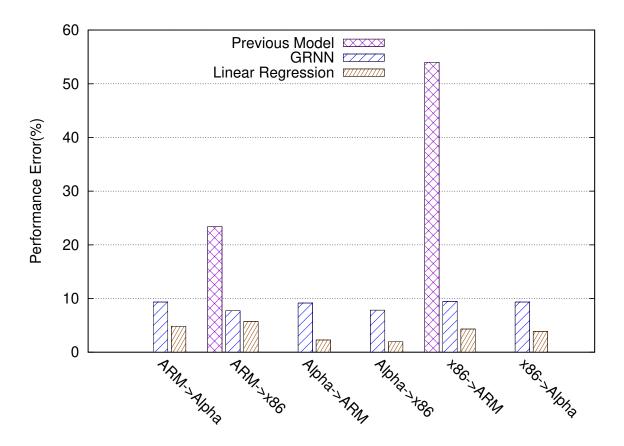

| 3.6       | Root mean squared error of performance modelling of Previous Model [12], GRNN and Linear Regression. $ISA_1 \longrightarrow ISA_2$ denotes estimation of performance for the core with $ISA_2$ while running the program on the core with $ISA_1$ | 42     |

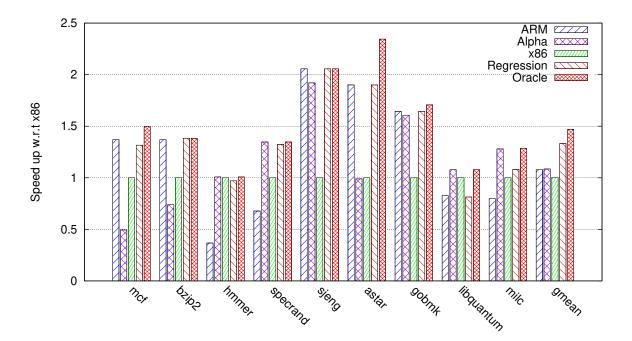

| 3.7       | Average speedup of different benchmarks when entire program is sched-<br>uled on ARM, Alpha or x86 and compared with HeIMC architecture with<br>regression and oracle based scheduling                                                            | 43     |

| 3.8       | Speedup w.r.t x86 of SPEC CPU2006 benchmarks when our system faces<br>programs it has not been trained on. Here the x-axis labels represents<br>benchmarks used only for testing while remaining benchmarks were used                             | 44     |

| 2.0       | for training.                                                                                                                                                                                                                                     |        |

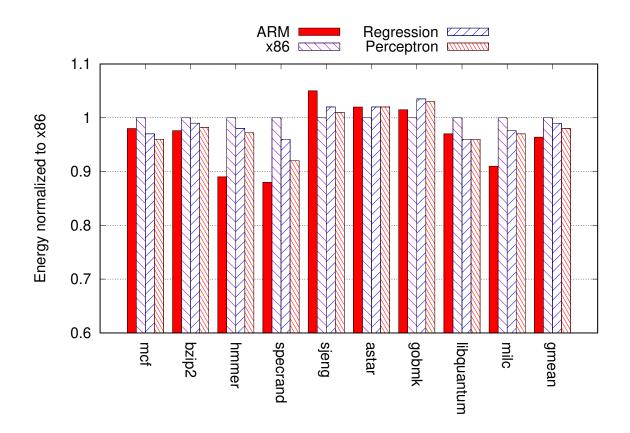

| 3.9       | Energy comparison                                                                                                                                                                                                                                 | 45     |

|           | Perceptron model                                                                                                                                                                                                                                  | 47     |

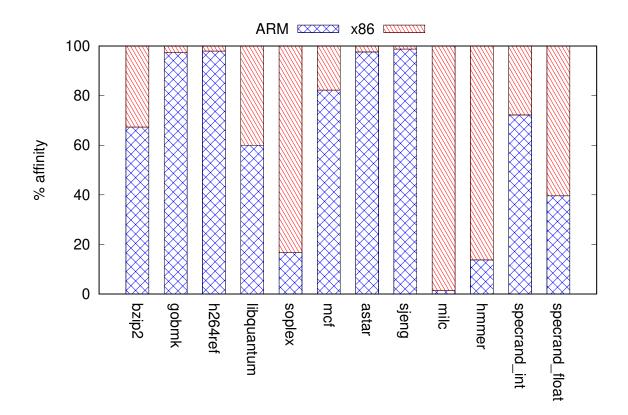

|           | Percentage ISA affinity for SPEC2006 benchmarks                                                                                                                                                                                                   | 49     |

| 3.12      | Migration decision accuracy for different benchmarks by perceptron sched-                                                                                                                                                                         | 50     |

| 0.10      |                                                                                                                                                                                                                                                   | 50     |

|           | Speedup when scheduling is done using perceptron                                                                                                                                                                                                  | 51     |

|           | Speedup when training and testing is done on different data sets                                                                                                                                                                                  | 52     |

| 3.15      | Energy when scheduled using perceptron                                                                                                                                                                                                            | 53     |

#### LIST OF FIGURES

| 4.1   | Execution time of different phases of benchmark <i>sjeng</i>                | 54         |

|-------|-----------------------------------------------------------------------------|------------|

| 4.2   | Execution time with different scheduling algorithms of benchmark sjeng.     | 55         |

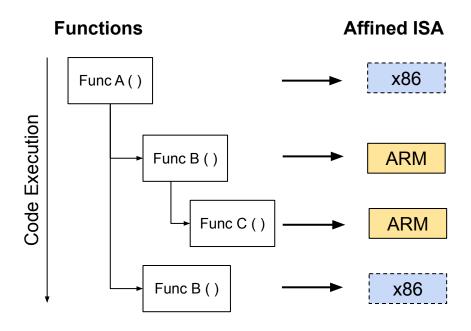

| 4.3   | libquantum function affinity                                                | 56         |

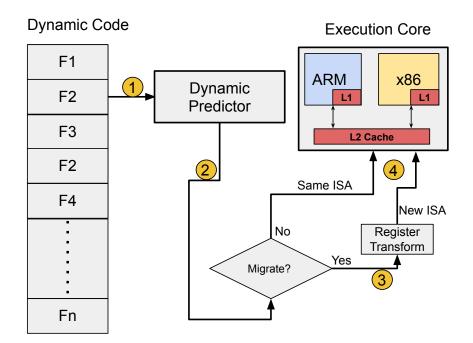

| 4.4   | Function scheduling flow chart                                              | 57         |

| 4.5   | Function order                                                              | 58         |

| 4.6   | Execution flow for example in fig 4.6                                       | 59         |

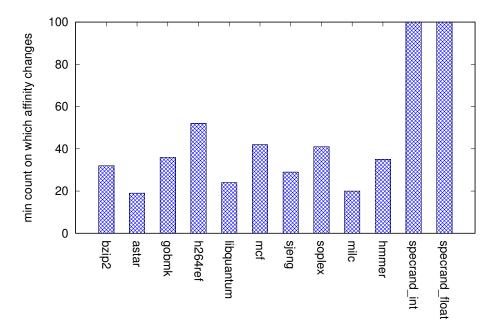

| 4.7   | Minimum count on which affinity changes                                     | 60         |

| 4.8   | Speedup on different size of Affinity table                                 | 61         |

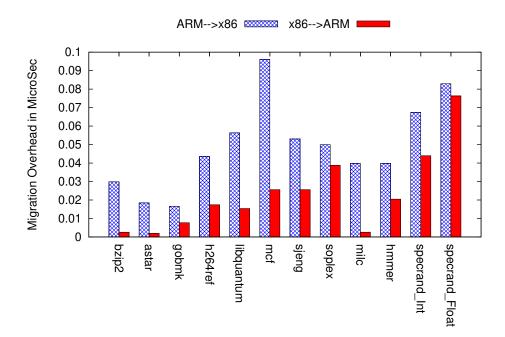

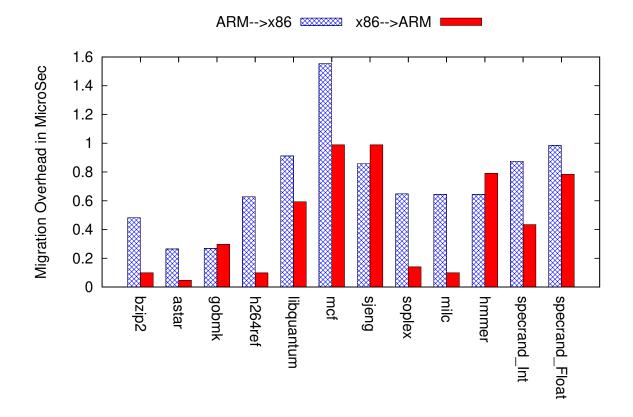

| 4.9   | Migration overhead for function-wise execution                              | 63         |

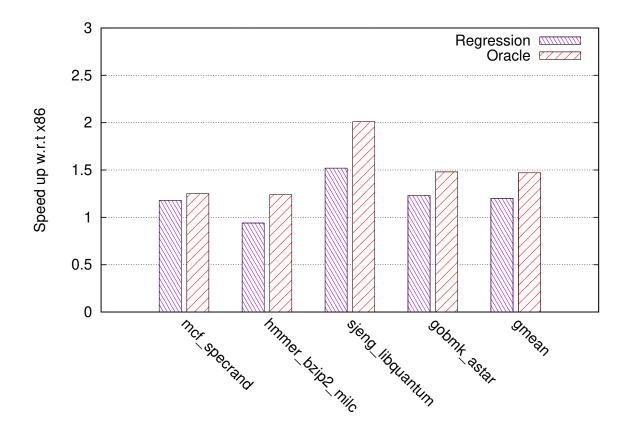

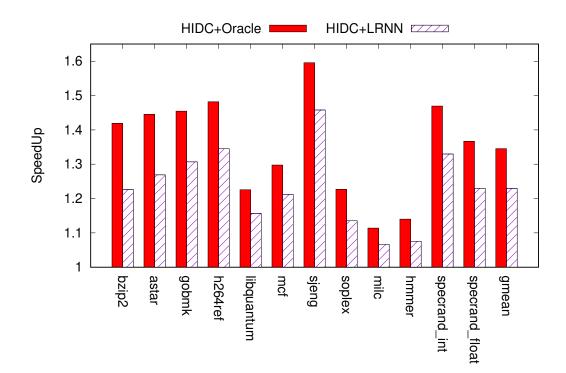

| 4.10  | Speedup of function-wise migration with respect to heterogeneous-ISA        | <u> </u>   |

| 4 1 1 | architecture                                                                | 64         |

| 4.11  |                                                                             | 0 <b>F</b> |

| 1.10  | architecture for multi-workloads                                            | 65         |

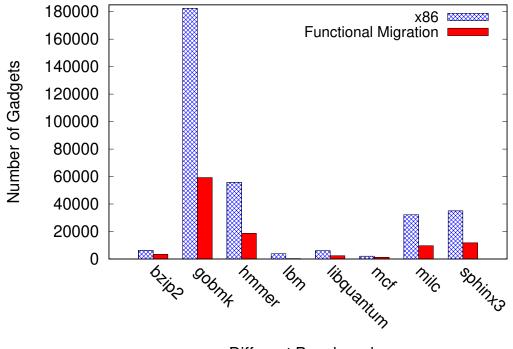

| 4.12  | Number of gadgets in different benchmarks                                   | 66         |

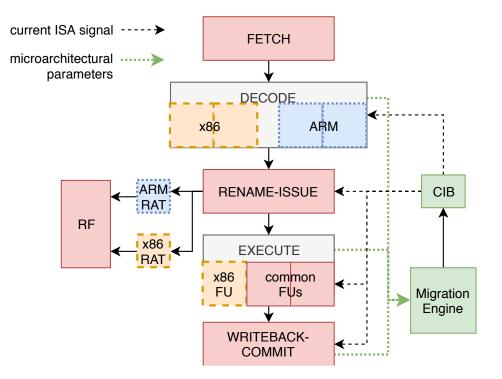

| 5.1   | High level architecture of HIDC pipeline                                    | 71         |

| 5.2   | Speedup on basis of small chunk of phase                                    | 73         |

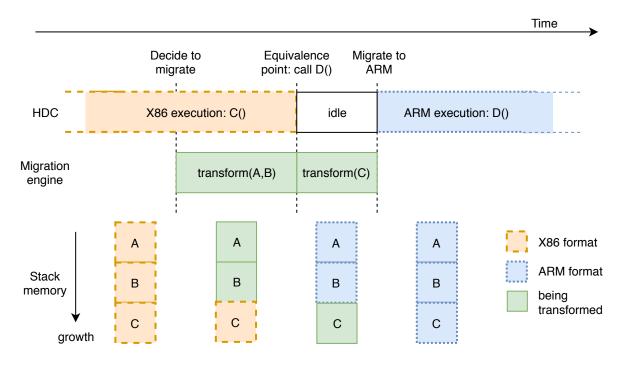

| 5.4   | Simultaneous Transformation                                                 | 83         |

| 5.5   | Transformation sequence for stack-frame of BZ2_bzDecompressStream           | 84         |

| 5.6   | Percentage ISA affinity for SPEC2006 benchmarks                             | 87         |

| 5.7   | Migration decision accuracy for different benchmarks by linear regression   |            |

|       | scheduler                                                                   | 87         |

| 5.8   | Migration overhead for simultaneous transformation                          | 89         |

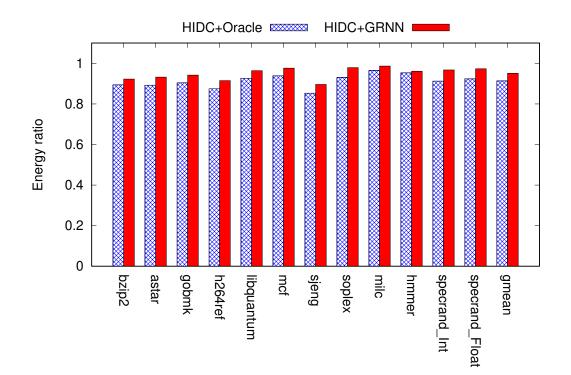

| 5.10  | Energy consumption ratios of HIDC architecture for benchmarks relative      |            |

|       | to HISACMP                                                                  | 91         |

| 5.11  | Performance per Joule of HIDC for SPEC2006 benchmarks                       | 92         |

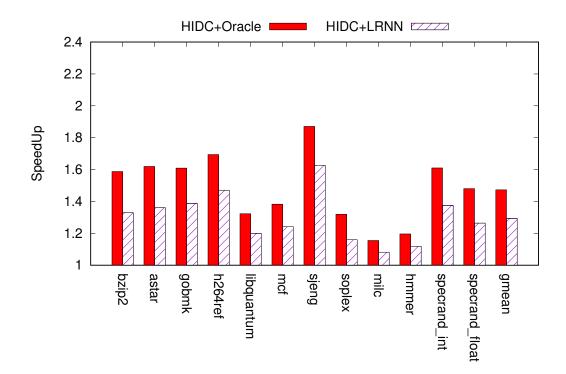

| 5.12  | Performance of HIDC with fine-grained scheduling relative to coarse-grained |            |

|       | scheduling                                                                  | 93         |

| 5.13  | Performance of multi workload benchmarks                                    | 94         |

| 6.1   | Attack methodology                                                          | 97         |

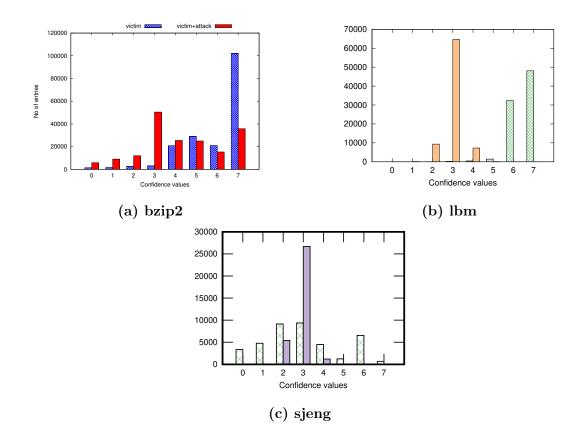

| 6.2   | Confidence distribution in different cryptographic benchmarks               | 101        |

| 6.3   | Confidence distribution in non-cyrptographic benchmarks                     | 102        |

| 6.4   | Different phases of RSA                                                     | 103        |

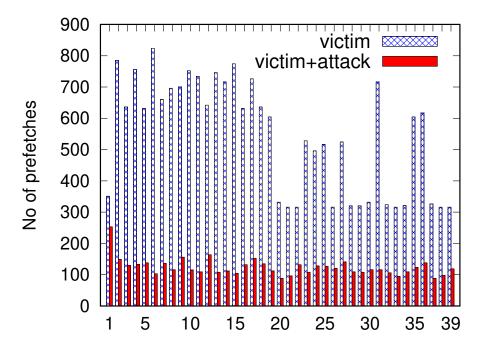

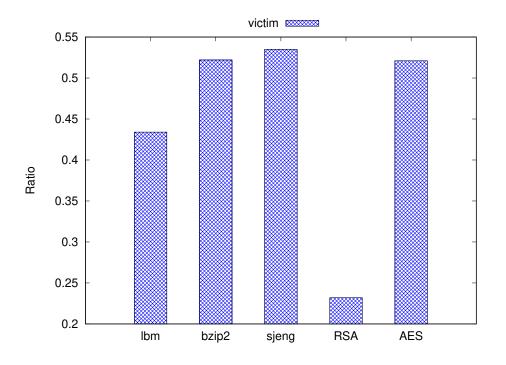

| 6.5   | Ratio of total prefetches                                                   | 104        |

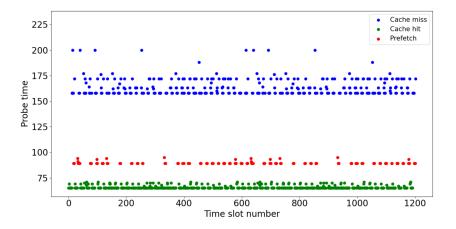

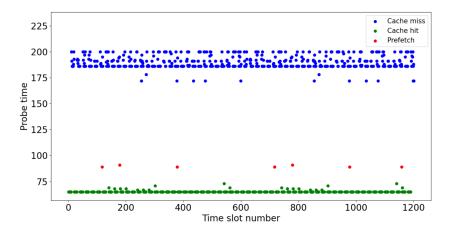

| 6.6   | Probe time measurement before attack                                        | 105        |

| 6.7   | Probe time measurement after attack                                         | 105        |

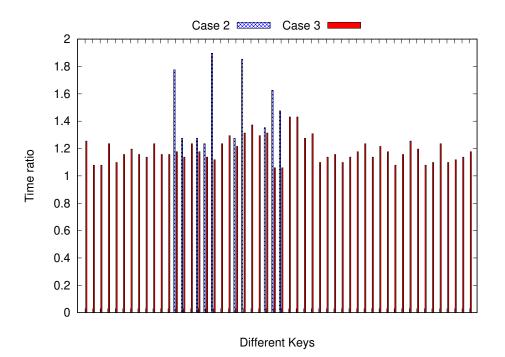

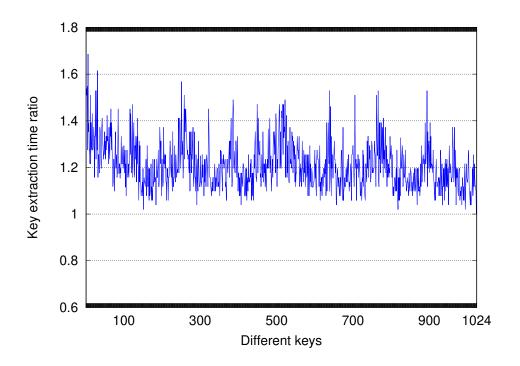

| 6.8   | Ratio of key extraction times for different conditions                      | 106        |

| 6.9   | Ratio of key extraction times for a system with prefetcher+proposed at-     | 105        |

| 0.10  | tack compared to without prefetcher                                         | 107        |

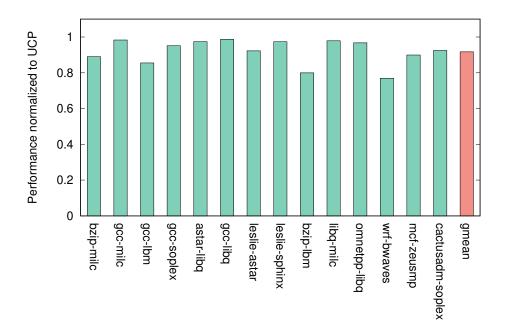

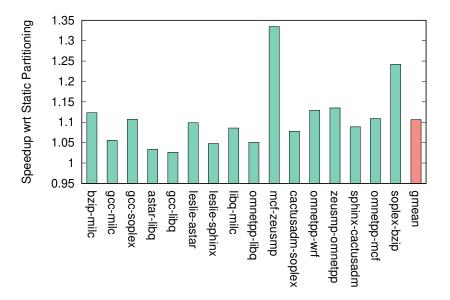

| 6.10  | Speedup of static partitioning scheme normalized to UCP for memory-         |            |

|       | intensive benchmark pairs (for Configuration 1 of Table 6.2).               | 108        |

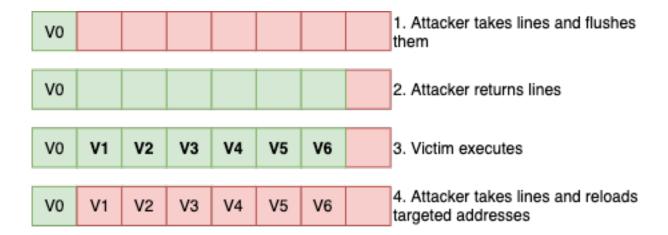

|       | Mechanism for Flush+Reload attack                                           | 110        |

| 6.12  | Mechanism for Prime+Probe attack                                            | 110        |

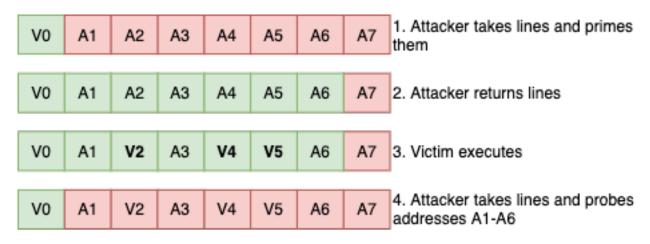

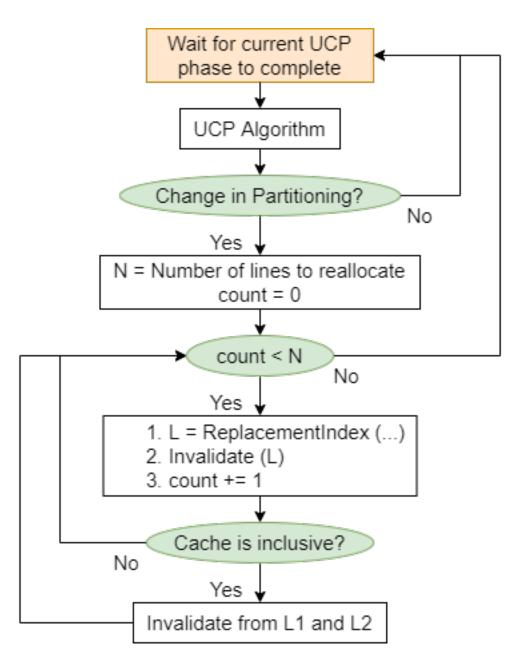

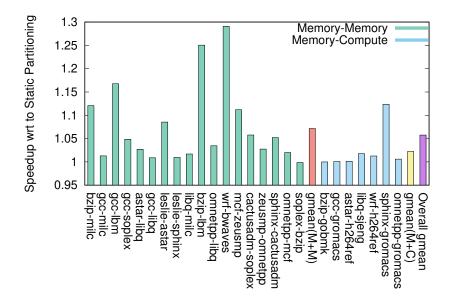

| 6.13 | Flow Diagram of PASS-P's reallocation Policy                                 | 114 |

|------|------------------------------------------------------------------------------|-----|

| 6.14 | Geometric means of speedups of PASS-P for memory-intensive benchmark         |     |

|      | pairs with respect to static partitioning for different values of $f$ . (For |     |

|      | Configuration 1 in Table 1)                                                  | 115 |

| 6.15 | Comparison of Speedup of PASS-P $(f=0.75)$ normalized to Speedup of          |     |

|      | Static partitioning for different benchmark pairs for Configuration 1 of     |     |

|      | Table 6.2                                                                    | 116 |

| 6.16 | Comparison of Speedup of PASS-P $(f=0.75)$ normalized to Speedup of          |     |

|      | Static partitioning for different benchmark pairs for Configuration 2 of     |     |

|      | Table 6.2                                                                    | 117 |

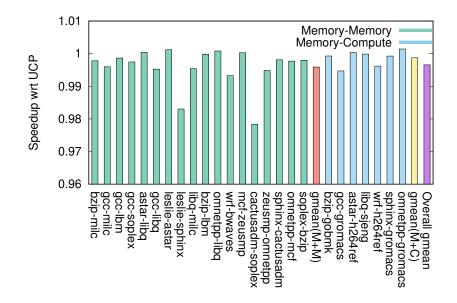

| 6.17 | Comparison of Speedup of PASS-P $(f = 0.75)$ normalized to Speedup of        |     |

|      | UCP for different benchmark pairs for Configuration 1 of Table 6.2           | 118 |

## Chapter 1

# Introduction

The past decades have witnessed very competitive dynamism in the advancements occurring in the field of microprocessor technology. Technological advancements and research have been focused on enhancing processor performance along with improving energy efficiency. Still, the demands for high-performance computing and energy efficiency are increasing rapidly nowadays with the increase in the amount of computations required in various applications.

During last century, since the invention of processors, researchers could achieve approximately 50% performance gain every year. This was achieved due to both technology improvements and micro-architectural innovations. The focus in the past few decades was mainly on making the core faster. "The faster, the better" was the tagline during this time. By the end of the century, power dissipation reached the limit of the air-cooled systems. Also, power density became equivalent to the power density of the hot plate. Hence the frequency of the system could not be increased further due to power density constraints, ending Dennard scaling. Therefore, the performance could be improved until saturation of the frequency scaling. This limitation is generally referred as power wall.

As the designers hit the power wall [76], to cater the need of current applications, the designers had to shift to multi-core architectures as making the core faster was not feasible. Multi-core systems have multiple cores on a chip. These systems can execute multiple threads simultaneously. Thus, multi-core architectures exploit threadlevel parallelism (TLP), enhancing system throughput. This led to change in the tagline from "The faster, the better" to "The more, the better".

Since single-threaded applications employ only one core and the remaining cores are not utilized. Therefore, in multi-core systems, throughput of the system is limited by single-threaded performance [5]. Many applications such as python interpreter, LAME: the open-source audio encode, Gem5, recursive programs mostly run as single-threaded application. So improving the *performance of single-threaded programs* is the area of prime interest. As the number of cores increases, the energy consumption of the system also increases. Therefore, the energy efficiency of a system still remains a problem.

Multi-core architectures share different resources among the cores to provide better energy efficiency. This may enable information leakage. Therefore, hardware security also become another concern in multi-core architectures. Thus, in this thesis, we focus on the following three main factors.

- 1. Single-threaded performance

- 2. Energy efficiency

- 3. Hardware security

### 1.1 Single-threaded performance

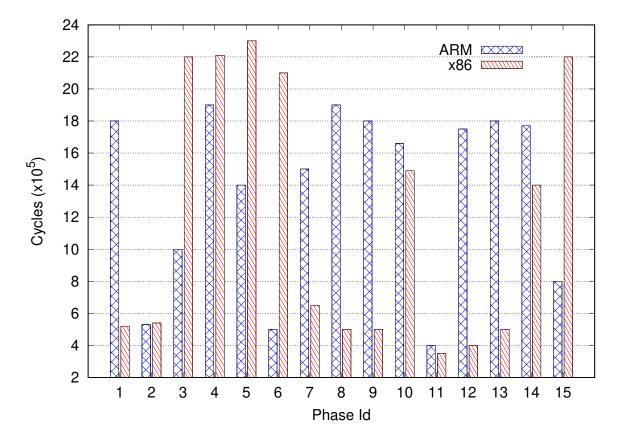

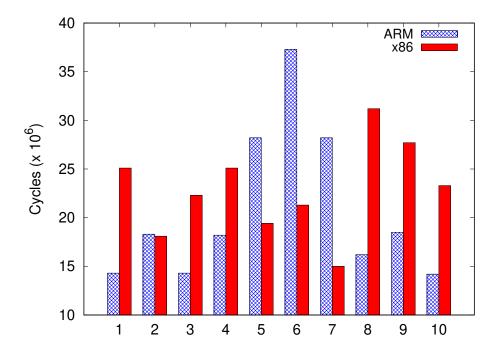

In multi-core architectures, various innovations have been done to improve the singlethreaded performance (for a single core), such as branch predictions, prefetcher, value predictions, cache replacement policies etc. Venkat et al. [99] proposed that a singlethreaded application's performance can be further increased when the affinity of a program towards an ISA is exploited. They found that the affinity of a program towards an ISA arises due to multiple factors such as code density, register pressure, dynamic instruction count, floating point and SIMD (Single instruction multiple data) support. To demonstrate the ISA affinity exhibited by programs and the proposed benefits of exploiting the same for single-threaded performance, we divide the 'astar' benchmark from SPEC CPU2006 [39] into 15 phases (phase length is 10 million instructions) and execute it on ARM (RISC) and x86 (CISC) cores. Different phases have an affinity towards different ISAs. Figure 1.1 shows the execution time of each phase on both cores. The results show that by only changing the ISA, there is sufficient variability across each phase's execution time. Further, neither core is dominant throughout, with x86 performing considerably better on phases 1, 7-14 and ARM performing considerably better on phases 2-6 and 15. Clearly, running the entire program solely on any one of these cores does not lead to optimal performance.

Figure 1.1: Execution time of different phases of benchmark astar

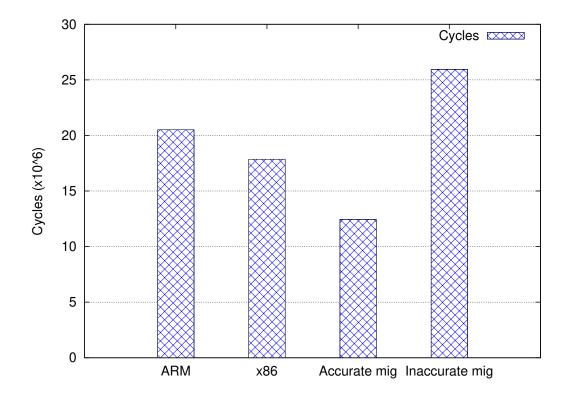

Figure 1.2 shows the latent performance benefits that can be extracted by Heterogeneous ISA multi-core architectures (accurate-migrations). When running each phase of the program on the core (and ISA) it is most suited to, the program's performance can increase by up to 39%. On the other hand, if the scheduling is flawed and mispredicts where to execute each phase of the program, it can lead to unacceptable performance deterioration of up to 26%. Clearly, maximum performance benefits are achieved only when the program is migrated across the cores at the right time. Venkat et al.[99], worked on showing the feasibility of prospective gains; however, the focus was NOT given on *how* to achieve that. Naturally, this requires a prediction and scheduling mechanism, which decides when this migration is supposed to occur. The best affine core for each phase of a program can be predicted using some mathematical models. Given the need for an accurate cross-ISA performance modelling technique, we have solved this problem at a coarse-grained and fine-grained level. We have done all the studies on two commonly used ISAs: RISC type ARM and CISC type x86. However, the proposed work can be used as it is on any number of ISAs on a chip. All the experiments are done on SPEC CPU2006 [39] benchmarks. Please be noted that we have done the scheduling at two different levels coarse-grained, and fine-grained levels. These are discussed in sections 1.1.1 and 1.1.2.

#### 1.1.1 Coarse grained scheduling

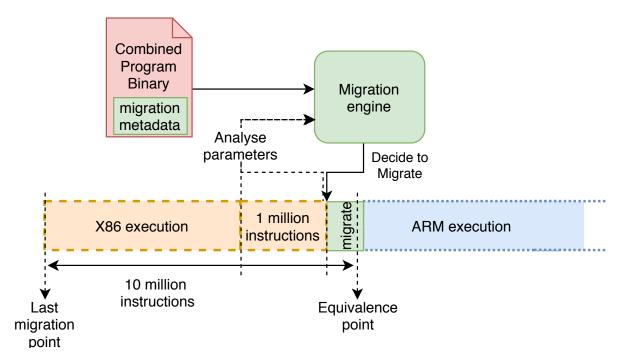

In coarse-grained scheduling, a phase of 100 million consecutive instructions is taken into consideration for scheduling purpose. The affinity of each phase is predicted, and the program is scheduled on that ISA. The migration decision is taken on the equivalence point (a point where the memory state is the same across the executable of both ISAs) [28]. If there is a need for migration, then the program's context switching takes place from one core to another core.

Since the program runs on only one of the ISA, we know the execution time and behaviour of the program on the ISA it is running. However, we do not have idea of the program's behaviour on the ISA on which it is not running. Hence, to take the scheduling decision, we need to estimate the program's behaviour on other ISA as well. To achieve this, we propose the following two scheduling techniques to execute the application on affined ISA based on the micro-architectural parameters.

Figure 1.2: Execution time when the program is run on ARM, x86 and execution time when each phase is run on the core most suited to it ("Accurate mig") and least suited to it ("Inaccurate mig")

- 1. Performance based scheduler

- 2. Classification based scheduler

#### 1. Performance based scheduler

In this work, the scheduler is designed based on the performance estimation of the cores. *Performance estimation is defined as estimating a program's execution time on a core on which it is not running.* Once the performance estimation is done, the scheduling of the application is done on the ISA, which has a lesser execution time after considering migration overhead.

For performance estimation, we trained different models which learn the relationship among various micro-architectural parameters of target ISA (ISA on which program is not running) and source ISA (ISA on which program is running). We also model the relationship between micro-architectural parameters and corresponding execution time for both ISAs. All these models are trained offline. Using these trained models, the system estimates the execution time of target ISA at run-time by first predicting the micro-architecture parameters of the target ISA from the source ISA's.

Based on this predicted execution time, the affinity of the phase is decided by the scheduler. The scheduling decision is taken after considering the migration overhead due to context switching. The accuracy of proposed scheduler is 82.9%, which translated to a performance benefit of 29.6% relative to state-of-art.

#### 2. Classification based scheduling

As our interest lies in obtaining a dynamic mapping of the program phase to an ISA core, we approached the scheduling problem as a classification problem in the second proposal of scheduling. We achieve a performance gain of 35.7% relative to x86 ISA, which is 6.1% more than the state-of-art i.e. performance based schedulers [13].

In all the coarse-grained scheduling mechanisms, affinity is identified for a phase of 100 million dynamic instructions.

#### 1.1.2 Finer-grained scheduling

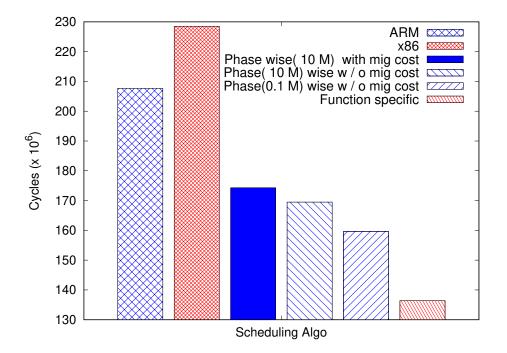

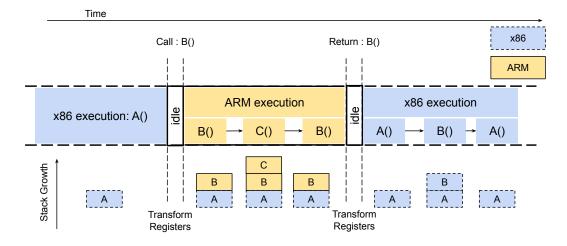

For long phases, the heterogeneity can not be exploited effectively, as the program behaviour within a phase varies. This work shows that shorter phases can give better performance if we reduce migration overhead (which is up to 100 µs in existing schemes [28], [99]). To exploit the program's heterogeneity more effectively, we introduce a finegrained function-wise scheduling technique, in which every function is proposed to be scheduled to its most affined ISA. Function-based scheduling reduces migration overhead as only function arguments have to be transformed from one ISA format to the other in this scheduling technique. This avoids a complete stack transformation which was required in previous proposals [28], [99]. We have reduced the migration overhead to a range of  $\{0.05 \,\mu s - 0.15 \,\mu s\}$ , that is three orders of magnitude less compared to previous proposals [28], [99]. With reduced migration overhead and making the scheduling decision on function levels, a performance gain of 65% relative to x86 can be achieved. We have proposed a heuristics for finding the affinity of a function at run-time. The performance gain with the proposed heuristics is 34.8% relative to x86. The proposed fine grained function wise scheduling achieved 22.9% in comparison to the state-of-art [15]. We have also shown that with the help of this scheduling algorithm, performance increases for the multi-threaded programs by 15.8% compared to state-of-art [99].

Now that we have looked into improving the performance of single-threaded applications using three different techniques. In the next section, an energy efficient architecture is proposed.

### 1.2 Energy efficient heterogeneous ISA dynamic core

The Demand for high-performance computing is increasing rapidly with the increasing use of big data applications. Architects have proposed chip multiprocessors (CMPs) consisting of multiple cores to achieve high throughput. Multi-core architectures were able to increase the performance of multi-threaded programs. However, a single-threaded program's performance is still a bottleneck. Researchers have shown that only 60-80% of the code can be parallelized, and the remaining 20-40% is single-threaded code. Hence, single-threaded performance is still a major bottleneck to enhance performance of the core.

To enhance single-threaded performance along with multi-thread performance, dynamic cores are proposed [59], [43], [79] in multi-core systems. These cores change their architecture dynamically to adapt to the program requirement. However, all the cores in such architectures support a single ISA. Heterogeneous ISA architectures emerged as a good alternative to enhance single-threaded performance (and multi-threaded programs as well). If any program is divided into multiple parts and each part is scheduled on most affined ISA, the significant performance gain is achieved. For any single-threaded program, only one core is active in these architectures. Due to this following are the limitations in these architectures.

- 1. The resources of idle cores are not utilized optimally.

- 2. All idle cores dissipate static power continuously.

- 3. On affinity change of a program, the context switching is done from one core to other core. This leads to larger context switching (migration) overhead and leads to reduction in performance.

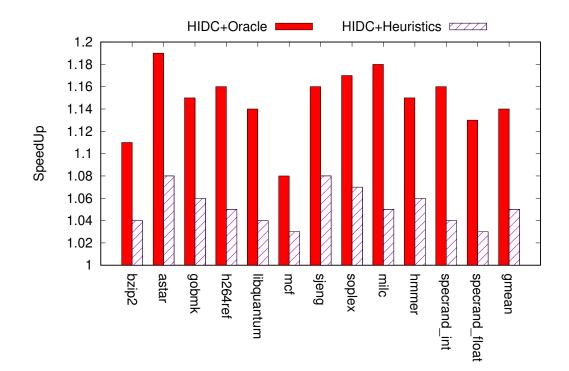

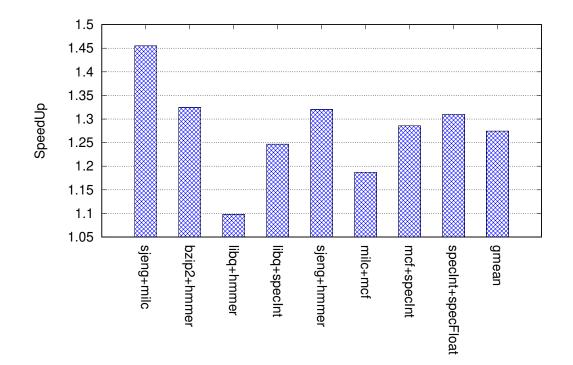

To overcome these limitations, under peak power-constrained model we propose an architecture called HIDC (Heterogeneous ISA Dynamic Core architecture). This architecture has a single core that supports multiple ISAs. This core changes its ISA support and architecture dynamically. Since the core is capable of supporting multiple ISAs, it contains the union of functionalities of multiple ISAs, which it supports. We studied four configurations (big x86, big ARM, small x86, small ARM). Bigger configurations are taken to improve the performance of the system. Smaller configurations are taken to improve the system's energy efficiency further. In the proposed architecture, all the level of caches are shared among all the ISAs, hence the migration cost is reduced. The scheduling is done at the coarse-grained and fine-grained level. We have reduced the migration overhead for coarse-grained level scheduling significantly with a "simultaneous migration mechanism". The migration cost is reduced by  $100 \times$  times compared to state-of-art [99]. On coarse-grained scheduling, we achieve a performance gain of 30.8% relative to state-of-art heterogeneous ISA architectures [99]. Since we could reduce the static power dissipation in HIDC, the energy consumption is reduced by 15.4% relative to [99]. These architectures give energy efficiency (Performance to energy ratio) of such architectures up to 54%. For fine-grained level scheduling, the performance gain of 5.2% is achieved on top of coarse-grained scheduling. Multi-threaded programs achieve a performance gain of 16.2% relative to state-of-art [99].

HIDC architectures help not only in improving the energy efficiency but also gives higher performance. Given that we have looked into performance and energy-efficient architectures in Section 1.1 and Section 1.2 respectively. In the next section, we discuss hardware security in the context of multi-core architectures.

### **1.3** Security in multi-core architectures

In all the multi-core architectures generally last level cache (LLC) is shared between the cores. This causes a security vulnerability in the form of side-channel attacks. Side channel attacks look at the unintended hardware footprints of the victim program to infer information. The different modes in which an attack can be mounted are referred to as 'channels'. These channels include analysis of execution time, memory accesses, power consumption and electromagnetic radiation of the hardware resources being used by the victim program. The attacker can infer the victim's memory access patterns by monitoring the cache lines in the shared cache. This is done by forcing collisions with the victim and making accesses to that alias with the same lines. This is possible as all the cores can access shared libraries. Since the memory access patterns in most security protocols are dependent on the private key, leaking information about these patterns may compromise the key. In any multi-core system, scopes of side-channel attacks always exit when multiple processes are running on different cores. Flush+Reload [107] and Prime+Probe [58] are common side-channel attacks that use differential cache access timing-analysis on lines modified by the victim process. By the timing-analysis on victim's cache lines, the attacker can deduce the addresses accessed by the victim.

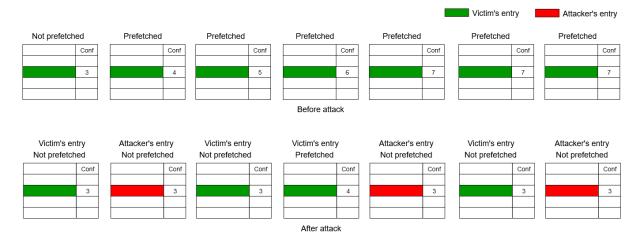

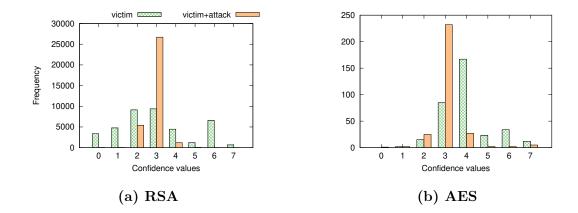

Researchers have proposed various mitigation methods for side-channel attacks. Prefetchers are claimed [94], [101] to be mitigate the side-channel attacks. They have shown that prefetcher works adversely for the attacker in timing-based side-channel attacks. However, we show the feasibility of attack even in the presence of prefetchers by disabling them. Another source for the attack in multi-core architectures is partitioning the cache dynamically. The last level cache of multi-cores is dynamically partitioned for performance enhancement. In this thesis, we will show that dynamic partitioning also increases the vulnerability in multi-core architectures.

#### **1.3.1** Disabling prefetchers to attack side-channel attack

A key feature in side-channel attacks is their susceptibility to noise. Data fetched into the cache but not used by the victim, will be observed as noise. A source of noise for an attacker is hardware prefetchers. Since the prefetcher brings data into the cache, it interferes adversely with the side-channel. Only the cache accesses corresponding to the victim are of interest to the attacker. However, the attacker will observe data fudged by the prefetcher and cannot distinguish them from accesses made by the victim. The true source of the access (whether it is due to victim or prefetcher) cannot be deciphered. Thus, in addition to boosting performance, prefetchers act as good mitigators of cache side channels. In this proposal, we claim that hardware prefetching can be circumvented when performing an attack. We present an attack that is successfully capable of disabling the prefetcher and opening up cache-side channel vulnerabilities. In the presence of a prefetcher, we extracted the private key with only 21% increment in the time taken compared to a noiseless system having no prefetcher.

Thus, prefechers can not be relied upon for mitigation of side-channel attacks. The shared cache is main reason for these attacks. Hence, we propose a defensive mechanism which is based on cache-partitioning protocols.

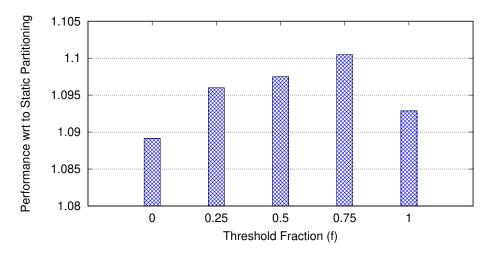

## 1.3.2 PASS-P: Performance and security sensitive partitioning protocol

Cache partitioning protocols were proposed to avoid interference between multiple threads. One of the cache partitioning mechanism is static cache partitioning [74], which avoids side-channel attacks also. It partitions the cache statically. In such partitioning, no sharing of resources is allowed, so side-channel attacks are mitigated. However, since the partitioning is done statically and processes may need more or less number of lines than allocated, this partitioning comes with performance degradation.

In shared last level cache, to improve the performance, utility-cache based partitioning (UCP) [81] was proposed. In this mechanism, the cache is dynamically partitioned on

the basis of the utility of cache for each application. This improves the performance by 8% over static partitioning. However, we show in this work that UCP is vulnerable to side-channel attacks.

To overcome the security and performance concerns in multi-core architectures, we propose PASS-P (Performance And Security Sensitive Partitioning) mechanism, which gives better security (similar to static partitioning) and performance almost equal to utility-based cache partitioning. We propose to invalidate all the cache lines which are re-allocated among the processes. We are also proposing a modified cache replacement algorithm that reduces the number of write-backs in systems. This helps in improving performance. The proposed work helps in enhancing the hardware security of the last level cache. With PASS-P, we are able to achieve a performance gain of 7.2% relative to static partitioning, which is less then by just 0.35% relative to UCP.

## 1.4 Contribution of the thesis

In this thesis we are targeting the performance, energy and security aspects of processor. Heterogeneous ISA architectures are utilized for performance improvement. IN these architectures, no one explored the scheduling of a program among different ISAs at run time previously. We have proposed to schedule a program at two different levels: coarse-grained and fine-grained. However, we observe that for single threaded programs, only one of the core is active and remaining cores dissipate power unnecessarily. To overcome this, we propose a new architecture HIDC. HIDC has a dynamic core and it supports multiples ISAs. The migration overhead is reduced in these architectures along with energy consumption. To see the security concerns of multi-core architecture, we first show the feasibility of attack in presence of prefetchers and then propose a new mitigation methodology called PASS\_P which is better in terms of security as well as performance.

## 1.5 Overview of thesis

The rest of thesis is organized as follows. Chapter 2 gives background on multi-core architectures. It discusses dynamic core architectures, scheduling in multi-core architectures. Heterogeneous ISA multi-core architectures have also been detailed. It also briefs about return oriented programming (ROP) attacks. This chapter also discusses on side-channel attacks and mitigation methods for these attacks.

Chapter 3 discusses the proposed scheduling methods in heterogeneous ISA architectures at coarse-grained level. A phase length of 100 million dynamic instruction count has been taken into consideration in this chapter. This has been done by performance estimation method and classification based scheduling mechanism. Migration overhead by [99] has been used in this work. Creation of fat binary by [54] has been used for creating similar fat binary which supports multiple ISAs.

Chapter 4 explains the scheduling in heterogeneous ISA architectures at finer level. We have proposed to the scheduling on each function. We also show that the migration overhead is reduced by 1000 x times in this work. We have also shown this mechanism better in ROP attacks.

Chapter 5 details a new architecture heterogeneous ISA dynamic core (HIDC) with one core for multiple ISAs. It also outlines the changes which need to be done to make HIDC core. We have also discussed a method to reduce the migration overhead in heterogeneous ISAs.

Chapter 6 discusses the potential side channel attacks in multi-core and hence in heterogeneous ISA architectures. This chapter also discusses that prefetchers can not be taken as mitigators in multi-core architectures. We have also shown the attack feasibility in widely used utility based cache partitioning mechanism. We have detailed a security mechanism called PASS-P for access based side channel attacks.

Chapter 7 concludes the thesis with possible future research directions.

## Chapter 2

# **Previous Work**

This chapter details the background information related to the thesis. Section 2.1 discusses the multi-core architectures and scheduling in it. Section 2.2 talks about security in multi-core architectures.

## 2.1 Multi-core architectures

Due to saturation of frequency scaling, improving performance of single-threaded workloads required addition of more and more resources to the core which was infeasible due to the limited power budget. The focus thus shifted from uni-core to multi-core architectures to dynamically migrate workloads between them [99]. Multi-core architectures are classified into homogeneous, heterogeneous, and dynamic cores. The focus of heterogeneous multi-cores (HeMC) [51] [52] architectures has been on exploiting Thread-Level Parallelism (TLP) & Instruction Level Parallelism(ILP), whereas Homogeneous multicore (HoMC) architectures [91] only focus on TLP. Few proposals on Dynamic core (DC) architectures like Core Fusion [43] focus on improving energy efficiency by dynamically changing core configurations based on requirement.

Computing power demand has been increasing in computers. Moore's law suggests that increased computation in single core machine have problems in terms of thermal constraints, power dissipation etc. Multi-core architectures can exploit the thread level parallelism. Multi-core architectures have less complex system and hence these architectures provide solutions to these problems. Multi-core architectures turned to be very useful in multimedia applications, high graphic games, embedded systems. A plethora of literature is available regarding multi-core architecture. We attempt to divide this section into three categories. First one is multi-core architectures which is further divided into homogeneous cores with same ISA, heterogeneous cores with same ISA and heterogeneous-ISA multi-core architectures. Second one explores performance modelling in heterogeneous architectures.

#### 2.1.1 Single ISA homogeneous multi-core architectures

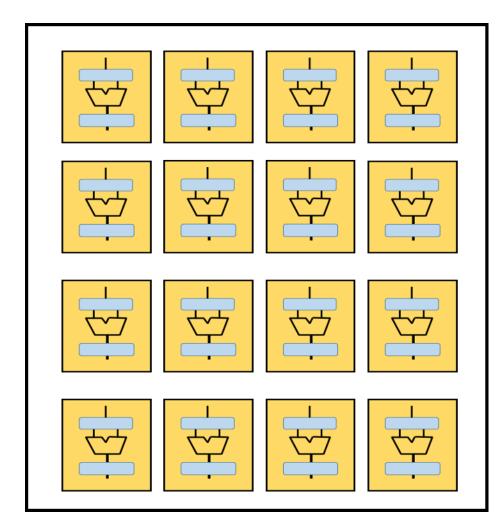

Figure 2.1: Symmetric multi-core with 16 BCE[40].

Figure 2.2: Symmetric multi-core with four cores and each core having four-Base core equivalent[40].

In this type of architectures same core is replicated multiple times on die. Architecture and capability of each single core is same. These architectures are also known as CMPs. [35], [66] have highlighted the benefits of multi-core systems. Hammend et al. [66] discuss the differences and benefits of having multi-core over SMT (Simultaneous Multi threading) architectures. Interconnect delays are more in SMT architectures. Gorder et al. [35] have shown that multi-core architectures not only help games but the researchers as well. They discuss of benefits of multi threaded program with each thread is potentially doing same task. Figures 2.1 and 2.2 show different homogeneous multi-core. Figure 2.1 shows a homogeneous multi-core. It has 16 baseline cores in it. Each baseline core is known as base core equivalent (BCE) [40]. Similarly Figure 2.2 has four core with each core having four BCE. Since, in such architectures, all the cores are identical therefore these are not best in terms of power benefits. [51], [52] have proposed heterogeneous multi-core architectures for power benefits which is discussed in the next section.

#### 2.1.2 Single ISA heterogeneous multi-core architectures

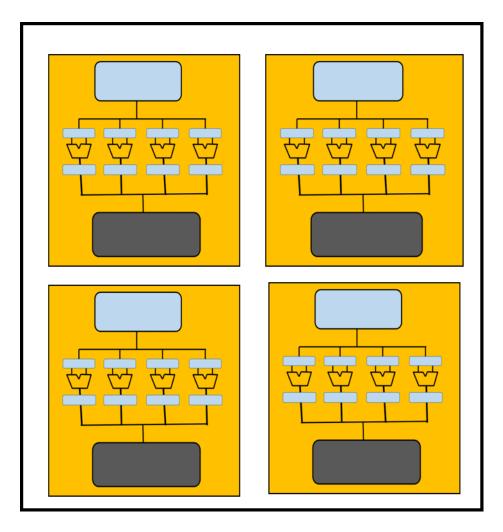

Prior work have shown that multi-core architectures have capability to enhance the program's performance. Various proposals [43], [79], [51], [52], [22], [10], [37], [40], [53], [60], and [72], [90] have been proposed related to the heterogeneity present in the core and ISA. Kumar et al. [51] [52] have shown that single ISA heterogeneous multi-core architectures can greatly enhance power reduction as compared to chip wide voltage/frequency scaling. Figure 2.3 shows heterogeneous multi-core with 13 cores, 12 cores are one BCE and thirteenth core is with four-BCE. This paradigm was widely adopted in commercial designs, most eminently in ARM's big.LITTLE architecture. Yoshimura et al. [108] proposed an SMT processor named OROCHI, where they are having two different pipeline for ARM and VLIW architectures. Ipek et al. proposed core fusion [43] architecture for improving single-threaded program's performance at times by morphing small cores into a big core. This work was further enhanced by Mihai et al. in the Bahurupi [79] architecture which changes the core's structure dynamically to extract maximum TLP and ILP by coalition of two or more simple homogeneous cores. The Bahurupi core increases the performance of single-threaded and multi-threaded applications. This architecture saves area compared to traditional small, big core combination. Lukefahr et al. [59] proposed an improvement on multi-core architectures by using heterogeneous cores that share resources. This sharing of resources enables dynamic migration at much smaller intervals between the heterogeneous cores. These cores however still shared the same ISA, differing only in their micro-architectural implementation. To improve performance and energy efficiency there has been another work DynaMOS [72] where they execute the program on performance efficient big core very first time. The traces of program is memorized and then the memorized trace is executed on In Order core to

Figure 2.3: Asymmetric multi-core with thirteen cores, one four-Base Core Equivalent core and 12 one-Base Core Equivalent cores [40].

save energy. Bahurupi architecture [79] also improves performance and energy efficiency. Finally, to increase the energy efficiency further, DynamicCore (DC) architectures [43] attempt to modify the micro-architectural parameters of cores on-the-fly, morphing from a single big core into many small cores(or vice-versa) depending upon the program.

# 2.1.3 Heterogeneous-ISA multi-core architectures

Since the beginning of microprocessor era, a lot of novel ideas have been put forward for improving the performance of single threaded workloads. Several studies [22], [10] have analyzed the role played by ISA in CISC and RISC processors and showed similar results both in terms of energy efficiency and performance. Lee et al. [55] investigated a subset of instructions in ARM ISA to find complex instructions which could be removed from the ISA without significantly reducing the performance. The reduced ISA has shown great reduction in logical complexity of the hardware. To improve the singlethreaded performance, Venkat et al. [99] have observed that most of these CMPs are inefficient as they are unaware about the opportunities of performance improvement by exploiting application's affinity towards a particular ISA. Venkat et al. [99] showed that ISA diversity plays an important role in performance enhancement of heterogeneous ISA and outlined the benefits of such a system in terms of both performance and energy efficiency. The authors have shown that although ISAs seem to have converged over time (RISC ISA has added complex operations and CISC ISA internally translates to RISC micro-ops), these ISAs are different in some key factors. These factors are code density, dynamic instruction count, register pressure, native floating-point arithmetic vs emulation, decode logic and instruction complexity, and SIMD support. Due to such differences in the ISA, it has been shown that different applications have an affinity towards different ISAs and running an application on its affined ISA can improve its performance. Heterogeneity in ISAs in a processor was first introduced by Devuyst et al. [28]. In their proposal, they present that significant performance gain can be achieved if every phase of program runs on its most affine ISA. In our work like Venkat et al. [99], we try to couple Heterogeneous ISAs with heterogeneous hardware.

# 2.1.4 Performance modelling and scheduling in heterogeneous architectures

To gain maximum benefits from multi-core architectures, an efficient scheduling algorithm is required which predicts the best affine ISA for every phase (phase is defined as 'n' continuous instructions of program) in a program at run-time. Several scheduling methods [95], [97], [4], [64], [62], [63], [67], [86], [3] have been proposed in single-ISA multi-core architectures. The first work on performance modelling in multi-core architectures was by Kumar et al. [52] who used a sampling-based technique to predict migration of programs on different cores. In this approach, they would run a small section of the code on all available cores and run the remainder of the code on the core that performed best for the small section. This leads to poor resource utilization. This naturally was not scalable and also performed poorly due to dynamic changes in program nature. To overcome this problem, the parameter cycles per instruction (CPI) was also tried to model by various researchers Craeynest et al. [96] used MLP(Memory level parallelism) and ILP parameters and introduced a regression based performance impact estimator. This was used further by Lukefahr et al. [59] and Pricopi et al. [80]. However, all these [27], [61] techniques while being especially suited for the homogeneous-ISA paradigm, provide suboptimal performance in the heterogeneous-ISA paradigm. In composite core [59] work, a thread switches in between two micro-engines, where one micro-engine is more aggressive while the other one is more energy efficient. Only one of the microengines remains active at any point in time allowing dynamic switching between the micro-engines so as to attain the best performance. The switching occurs on the basis of the past execution history. Venkat et al. [99] have migrated the thread from one core to another using SimPoint [78] metadata and profiling information from oracle experiments. Barbalace et al. [6] consider the behavior of the application to be unchanging throughout the program. They have calculated the cost (data transfer and migration) offline and found the migration points on the basis of this cost. Execution affinity towards different ISAs is also considered using the mincut algorithm. One another work on estimating performance of single ISA heterogeneous multi-core architecture is [16].

Craeynest et al. [96] introduced a regression-based performance impact estimator that used ILP and MLP (Memory level parallelism) as parameters to predict migration. While techniques work well for Heterogeneous multi-core architectures, they do not make accurate predictions for Heterogeneous ISA multi-core architectures. This is because they are simply not designed to take into account factors that determine performance variation across ISAs, such as code density, register pressure and instruction mix since these factors are identical across cores of the same ISA. To the best of our knowledge, we are proposing the first work attempting the estimation of the performance on one ISA by executing it on the other. This estimation is the basis of performance modelling of heterogeneous ISAs.

In order to exploit full advantage offered by diversity of ISA, it is essential that the running program is freely able to migrate between different cores. Literature has shown this to be a difficult problem [28],[99].

#### 2.1.5 Migration techniques in multi-core architectures

Once the most affine ISA is determined, the program state has to be migrated with minimum overhead. The Tui system [89] discusses the migration strategy in heterogeneous-ISA systems. In that work, the authors propose to transform the runtime state of program to state of program of required ISA. Some other proposals [7], [70] have explored the optimal state of program which required to be copied during migration.

# Figure 2.4: The memory state is consistent across different ISAs at Equivalence Points.

Following these approaches, Devusyt et al. [28] described the memory layout of a program executing on two different ISAs. They have shown that dynamic migration from one ISA to another one is possible at minimal performance cost. They observed that most of the memory arrangement could be shared for different ISAs without significantly

affecting the performance of any of ISA. They showed that by making a few modifications to the compiler back end, it is possible to have relatively frequent equivalence points in a program where the memory image of the program would be almost similar across different ISAs as shown in Figure 2.4. This resulted into a great reduction in migration overhead, making heterogeneous-ISA multi-core architectures feasible. A new migration scheme with binary translation was devised by Venkat et al. [99] where the program migrates to the new ISA immediately and the previous ISA's instructions are binary translated to the new ISA until an equivalence point is reached. From equivalence point onward, it starts executing using the new ISA's instructions. The program's memory state needs to be transformed from one ISA format to the other during migration. This transformation leads to significant migration overhead, which limits the granularity of migration.

In the proposed work, we are proposing to migrate only on equivalence points to save the cost of binary translation. In the scheduling mechanisms proposed in chapter 3, we are following to migrate in a similar approach by [99]. In chapter 4 and 5, we are proposing new techniques to reduce the migration overhead.

### 2.1.6 Dynamic core architectures

To increase the energy and performance efficiency further, dynamic core architectures [43] have been proposed, where a single big core is morphed into many small cores (or vice-versa) looking the behaviour of the program. In the proposal [72], authors proposed to remember the trace and then changing the behaviour dynamically of the core either as small or big at run time. Ipek et al. [43] have proposed that energy can be saved if smaller cores are morphed into big cores and vice versa based on the program's behaviour. Mihai et al. [79] have also proposed to make the core dynamic based on ILP and MLP. Another work in this direction was proposed by Padmanabha et al.[72] where they run the program on Big core first time and remember the traces. On the second run of the same program, the core is changed to the smaller core. The traces are run on small core, and hence energy can be saved.

#### 2.1.7 Return oriented attacks

Buffer overflow vulnerabilities have been exploited by injecting malicious codes. To prevent this, modern processors have Executable Space Protection [98], [92] where only one of the operation can be performed on a memory page either writing or execution. Both operations can not be done on a memory page. Hence code reuse attacks have been proposed where the attacker uses the existing code only to mount an attack. Return oriented programming is a type of return-into-libc attacks. Return oriented programming was introduced by Hovav Shacham [88], [83]. In Return-oriented Programming short code snippets are chained together in the program. These short code snippets are called gadgets. Gadgets are chosen with a characteristics that gadgets end with a return or an indirect jump instruction. The stack is overflowed with sequence of return addresses which are very carefully constructed [100]. Once any gadget is executed and the instruction pointer reaches to return instruction, the next gadget is exploited with the help of stack pointer. These attacks have been proven to be turing complete [17], for multiple ISAs. Several variants of return oriented programming have been proposed in literature [11], [20], [44], [23], [18], [18], [41], [87], [84].

Several control flow techniques [1], [24], [25], [75], [109], [110] have been proposed in literature to mitigate these attacks. In such techniques the execution of any program is pre defined by control flow graphs. However, implementing a control flow integrity at run-time is a difficult job. Also some backdoor attacks [30], [33], [34], [19], [26] have been proposed which can by pass these techniques and hence making the system vulnerable. We will show in Chapter 4 that our proposed mechanism reduces the probability of such attacks significantly.

# 2.2 Security

All these multi-core architectures with shared last level cache are vulnerable towards side channel attacks. Hence, this section is detailed about security aspect of multi-core architectures.

#### 2.2.1 Different security attacks