## Security and Testability Issues in Modern VLSI Chips

Submitted in partial fulfilment of the requirments of the Degree of

Doctor of Philosophy

by

Satyadev Ahlawat

(Roll No. 144076004)

Supervisor:

Prof. Virendra Singh

Department of Electrical Engineering Indian Institute of Technology Bombay  ${\rm Mumbai-400076}$

September 2018

©Satyadev Ahlawat September 2018 All rights reserved

## **Publications**

#### Included in Thesis

#### Journal publications

- Satyadev Ahlawat, Jaynarayan Tudu, Anzhela Matrosova, and Virendra Singh, A High Performance Scan Flip-Flop Design for Serial and Mixed Mode Scan Test, IEEE Transactions on Device and Materials Reliability (TDMR), 2018, Volume: 18, Issue: 2, pp. 1 - 11, http://doi.org/10.1109/TDMR.2018.2835414

- Jaynarayan Tudu, Satyadev Ahlawat, and Virendra Singh, Architectural Framework for Configurable Joint-scan DFT Architecture, Journal of Electronic Testing: Theory and Applications (JETTA), 2018 [under review]

#### Peer reviewed conferences

- Satyadev Ahlawat, Darshit Vaghani, Naveen Bazard, and Virendra Singh, "Using MISR as Countermeasure Against Scan-based Side Channel Attacks", Proceedings in 16th IEEE East-West Design and Test Symposium (EWDTS) 2018, Kazan, Russia, September 14 17, 2018.

- Darshit Vaghani, Satyadev Ahlawat, Jaynarayan Tudu, Masahiro Fujita, and Virendra Singh, "On Securing Scan Design Through Test Vector Encryption", Proceedings in 51st IEEE International Symposium on Circuits and Systems (ISCAS) 2018, Florence, Italy, May 27 - 30, 2018, pp. 1 - 5, https://doi.org/10.1109/ ISCAS.2018.8351212

- Satyadev Ahlawat, Darshit Vaghani, Jaynarayan Tudu, and Virendra Singh,

"On Securing Scan Design from Scan-Based Side-Channel Attacks", Proceedings

in 26th IEEE Asian Test Symposium (ATS) 2017, Taipei, Taiwan, November 27 30, 2017, pp. 58 63, https://doi.org/10.1109/ATS.2017.23

- 6. Satyadev Ahlawat, Darshit Vaghani, and Virendra Singh, "Preventing scan-based side-channel attacks through key masking", Proceedings in 30th IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT) 2017, Cambridge, UK, October 23 25, 2017, pp. 1 4, https://doi.org/10.1109/DFT.2017.8244434

- 7. Satyadev Ahlawat, Darshit Vaghani, Jaynarayan Tudu, and Ashok Suhag, "A Cost Effective Technique for Diagnosis of Scan Chain Fault", *Proceedings in 21st International Symposium on VLSI Design and Test (VDAT) 2017*, Roorkee, India, June 29th July 2nd, Communications in Computer and Information Science (CCIS), volume 711, Springer, Singapore, pp. 191 204, https://doi.org/10.1007/978-981-10-7470-7\_20

- Satyadev Ahlawat, Darshit Vaghani, Rohini Gulve, and Virendra Singh, "A low cost technique for scan chain diagnosis", Proceedings in 50th IEEE International Symposium on Circuits and Systems (ISCAS) 2017, Baltimore, MD, USA, May 28 31, 2017, pp. 1 4, https://doi.org/10.1109/ISCAS.2017.8050440

- 9. Satyadev Ahlawat, Darshit Vaghani, and Virendra Singh, "An efficient test technique to prevent scan-based side-channel attacks", *Proceedings in 22nd IEEE European Test Symposium (ETS)*, 2016, Limassol, Cyprus, May 22 26, 2017, pp. 1 2, https://doi.org/10.1109/ETS.2017.7968241.

- 10. Satyadev Ahlawat and Jaynarayan T. Tudu, "On minimization of test power through modified scan flip-flop", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT), 2016, Guwahati, India, May 24 27, 2016, pp. 1 6, https://doi.org/10.1109/ISVDAT.2016.8064878

- 11. Satyadev Ahlawat, Darshit Vaghani, Rohini Gulve, and Virendra Singh, "Enabling LOS delay test with slow scan enable", *Proceedings in 14th IEEE East-West Design & Test Symposium (EWDTS)*, 2016, Yerevan, Armenia, October 14 17, 2016, pp. 1 4, https://doi.org/10.1109/EWDTS.2016.7807648

- 12. Satyadev Ahlawat, Jaynarayan Tudu, Anzhela Matrosova, and Virendra Singh, "A High Performance Scan Flip-Flop Design for Serial and Mixed Mode Scan Test", Proceedings in 22nd IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS) 2016, Catalunya, Spain, July 04 06, 2016, pp. 233 238, https://doi.org/10.1109/IOLTS.2016.7604709

- 13. **Satyadev Ahlawat**, Jaynarayan Tudu, Anzhela Matrosova, and Virendra Singh, "A New Scan Flip Flop Design to Eliminate Performance Penalty of Scan", *Proceedings in 24th IEEE Asian Test Symposium (ATS) 2015*, Mumbai, India, November 22 25, 2015, pp. 25 30, https://doi.org/10.1109/ATS.2015.12

#### Other Contributions

- 14. Nihar Hage, Satyadev Ahlawat, and Virendra Singh, "In-situ Monitoring for Slack Time Violation Without Performance Penalty", Proceedings in 51st IEEE International Symposium on Circuits and Systems (ISCAS) 2018, Florence, Italy, May 27 30, 2018, pp. 1 5, https://doi.org/10.1109/ISCAS.2018.8351000

- 15. Jaynarayan T. Tudu and Satyadev Ahlawat, "Guided shifting of test pattern to minimize test time in serial scan", Proceedings in 20th International Symposium on VLSI Design and Test (VDAT), 2016, Guwahati, India, May 24 27, 2016, pp. 1 6, https://doi.org/10.1109/ISVDAT.2016.8064851

### Abstract

The advancements in semiconductor fabrication process has made it possible to built electronic systems with unimaginable functional complexity. This has led to the development of highly complex systems like autonomous vehicles, personnel healthcare, deep neural networks, virtual reality, smart homes and cities, and many more emerging IoT (Internet-of-Things) based applications. Many of these new applications are very critical from reliability and security point of view.

The reliability requirement of such systems has made the testing of these systems very challenging. In applications like automobiles or autonomous vehicles, manned space mission, defence etc., where human life is at stake, the system reliability is of utmost importance. For such systems the DPPM (defective parts per million) requirement is ideally zero. To ensure shipment of such highly reliable systems the test requirements are becoming very stringent. Moreover, these modern day IoT based systems not only have complex functionality they also do continuous communication with other systems in their surrounding. This has put system security along with reliability in forefront of the design challenges in designing such systems.

The problem further escalates because security and testability have orthogonal objectives. To achieve high testability, the internal state information of a chip must be as visible as possible to the test engineer. On the other hand, from security point of view the sensitive information embedded in a chip must not be accessible to the outside world. This thesis investigates the conflicting requirements of security and testability in modern day complex *VLSI* chips. We introduce techniques which can test these security sensitive chips in a secure manner.

The scan-based DfT (Design-for-Test) architecture is the only economically viable test technique available today which can effectively test the modern day highly complex chips, and fulfill the stringent quality requirements. Because of the testability and diagnostic requirements scan design has become the de-facto DfT technique and is therefore employed in almost every chip. The scan architecture is generally operated by a test engineer to perform scan test operation, however, a malicious user can exploit the scan architecture to observe the sensitive data stored on-chip in a security or cryptographic chip.

The thesis first addresses security issues in scan test. We have proposed a set of techniques which can effectively secures the scan design against all the known scan-based side-channel attacks. The proposed techniques are based on test protocol countermeasures such as encryption key masking, test restriction, and test data encryption. The proposed techniques not only thwart scan attacks but also preserves the test capability of scan architecture. Moreover, the proposed secure scan design techniques are very efficient in terms of design cost.

Next, this thesis also addresses the testability issues like test data volume, test time, and test power which scan inherits because of its serial nature. With ever increasing circuit complexities these parameters are growing exponentially and needs attention as the test cost constitute almost half of the total chip cost. In this thesis, we propose a composite scan architecture which aims to combine both, the serial scan and random access scan, to harness the best out of each. The proposed architecture minimizes test time, test data volume, and test power all together. Further, we carry out a foundational study for its feasibility and to compare its advantage over the existing multiple serial scan architecture and random access scan architecture.

Finally, the thesis delve into some other scan issues like scan performance overhead, unnecessary combinational switching power during scan shift, scan chain diagnosis, and launch-off-shift based delay test with slow scan enable signal. To tackle these issues, we have proposed solutions based on efficient circuit level design of scan cell.

## Keywords

VLSI Testing, Design-for-Test, Serial Scan, Random Access Scan, Multiple Serial Scan, Joint-scan, Test Power, Test Data Volume, Power Aware Test, Scan Attack, Secure Scan design, Scan Cell, and Scan Chain Diagnosis

## Notation and Abbreviations

$C_L$  : Load Capacitance MSDFF : Multiplexed Scan D Flip-flop

$I_{DDQ}$  : Quiescent Current MSS : Multiple serial scan  $L_p$  : Launch Pulse MT-Fill : Minimum Transition Fill

VDD : Drain Supply Voltage NMOS : N-type MOS

2M-JScan : 2-Mode Joint-scan P-random : Partial Random Access Scan

4M-JScan 4-Mode Joint-scan P-serial Partial Serial Scan AES Advanced Encryption Standard PCB Printed Circuit Board ATEAutomatic Test Equipment PDF Path Delay Fault ATPG Automatic Test Pattern Generation PIPrimary Input BIST P-type MOS Built-In Self-Test PMOS C-X РО Primary Output Care - Don't care bit pair CBR Care Bit Ratio PPI Pseudo Primary Input

CMOS : Complementary MOS PPO : Pseudo Primary Output

CP : Clock Signal/Pulse PRAS : Progressive Random Access Scan

CUT : Circuit Under Test PRAS-FF : Progressive Random Access Scan Flip-Flop

DfT : Design-for-Test SAF : Stuck-at-Fault

${\rm DSM} \qquad : \quad {\rm Deep \; Sub\text{-}micron} \qquad \qquad {\rm SDF} \qquad : \quad {\rm Segment \; Delay \; Fault}$

LBIST : Logic Built in Self Test SO : Scan Output

LFSR : Linear Feedback Shift Register SoC : System On Chip

LOC : Launch off Capture TCL : Test Control Logic

LOS : Launch off Shift TCl/TCLK : Test Clock

${\it LSSD} \qquad : \quad {\it Level Sensitive Scan Design} \qquad \qquad {\it TDF} \qquad : \quad {\it Transition Delay Fault}$

MBIST : Memory Built in Self Test TE : Test Enable

MISR : Multiple Input Signature Register VLSI : Very Large Scale Integration MOS : Metal Oxide Seminconductor X-C : Don't care - care bit pair

${\it MOSFET} \quad : \quad {\it MOS Field Effect Transistor} \qquad \qquad {\it X-Fill} \qquad \qquad : \quad {\it Don't Care Fill}$

## Contents

| Publications |                                              |         | i                                  |    |

|--------------|----------------------------------------------|---------|------------------------------------|----|

| Al           | Abstract Keywords Notation and Abbreviations |         |                                    |    |

| K            |                                              |         |                                    |    |

| N            |                                              |         |                                    |    |

| 1            | Intr                                         | oducti  | on to VLSI Test                    | 1  |

|              | 1.1                                          | VLSI '  | Testing                            | 2  |

|              |                                              | 1.1.1   | Functional vs Structural Testing   | 3  |

|              |                                              | 1.1.2   | Fault Models                       | 5  |

|              |                                              | 1.1.3   | Sequential Circuit Testing         | 10 |

|              | 1.2                                          | Design  | for Testability                    | 12 |

|              |                                              | 1.2.1   | Scan Architecture and Scan Testing | 13 |

|              |                                              | 1.2.2   | Scan based Testing                 | 16 |

|              |                                              | 1.2.3   | Issues in Scan Test                | 18 |

|              | 1.3                                          | Scope   | of Thesis                          | 19 |

|              |                                              | 1.3.1   | Thesis Organization                | 20 |

| 2            | Mot                                          | tivatio | n and the State-of-the-art         | 21 |

|              | 2.1                                          | Securi  | ty Issues in Scan Test             | 21 |

|              |                                              | 2.1.1   | AES and Scan-based Attack          | 23 |

|              |                                              | 2.1.2   | The State-of-the-art               | 28 |

|              | 2.2                                          | Testab  | bility Issues in Scan              | 31 |

|              |                                              | 2.2.1   | Test Time and Test Data Volume     | 33 |

|              |                                              | 2.2.2   | Test Power                         | 37 |

|              |                                              | 2.2.3   | Scan Chain Diagnosis               | 40 |

|              |                                              | 2.2.4   | Test Performance Overhead          | 41 |

|              | 2.3                                          | Conclu  | ısion                              | 42 |

| 3            | Sec                                          | ure Sca | an DfT Architecture                | 44 |

|              | 3.1                                          | Securi  | ng Scan through Key Masking        | 45 |

|              |                                              | 3.1.1   | Proposed Key Masking Technique     | 46 |

|              |                                              | 3.1.2   | Security and Testability Analysis  | 53 |

**CONTENTS** ix

|   | 3.2 | Securi        | ing Scan through Test Restriction                              | 54        |

|---|-----|---------------|----------------------------------------------------------------|-----------|

|   |     | 3.2.1         | Test Authorization using LFSR                                  | 55        |

|   |     | 3.2.2         | Test Authorization Logic                                       | 55        |

|   |     | 3.2.3         | Security and Testability Analysis                              | 31        |

|   |     | 3.2.4         | Test Authorization using MISR                                  | 3         |

|   |     | 3.2.5         | Test Authorization Logic                                       | 3         |

|   |     | 3.2.6         | Security and Testability Analysis                              | 57        |

|   |     | 3.2.7         | Securing Scan through Plain-text Restriction                   | 39        |

|   |     | 3.2.8         | Test control Logic                                             | 70        |

|   |     | 3.2.9         | Security and Testability Analysis                              | 72        |

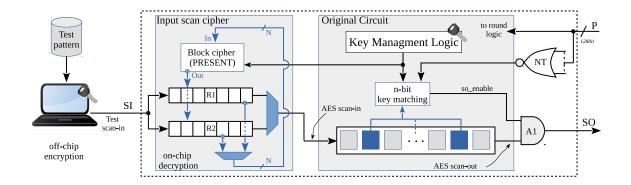

|   | 3.3 | Securi        | ing Scan through Test Data Encryption                          | 73        |

|   |     | 3.3.1         | Securing Scan through Test Vector Encryption                   | 74        |

|   |     | 3.3.2         |                                                                | 75        |

|   |     | 3.3.3         | Security and Testability Analysis                              | 78        |

|   |     | 3.3.4         |                                                                | 30        |

|   |     | 3.3.5         | Functional and Test Mode Operation                             | 31        |

|   |     | 3.3.6         | Security, Testability, and Design cost Analysis                | 34        |

|   | 3.4 | Concl         |                                                                | 35        |

| 4 | т   |               | The st. As all the stores                                      | 37        |

| 4 | 4.1 |               |                                                                | ) 1<br>38 |

|   | 4.1 | 4.1.1         |                                                                | 39        |

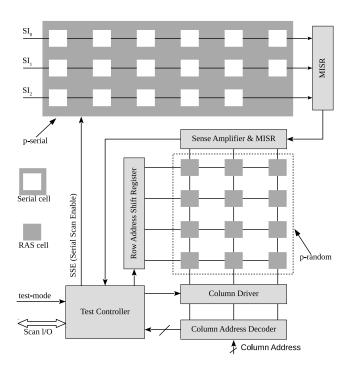

|   | 4.2 |               |                                                                | 90        |

|   | 4.2 | 4.2.1         |                                                                | 90<br>90  |

|   |     | 4.2.1         |                                                                | 90<br>92  |

|   |     | 4.2.3         |                                                                | 92<br>93  |

|   | 4.3 |               |                                                                | )4        |

|   | 4.5 | 4.3.1         |                                                                | 95        |

|   |     | 4.3.1         |                                                                | 90<br>97  |

|   |     | 4.3.3         | •                                                              | 98        |

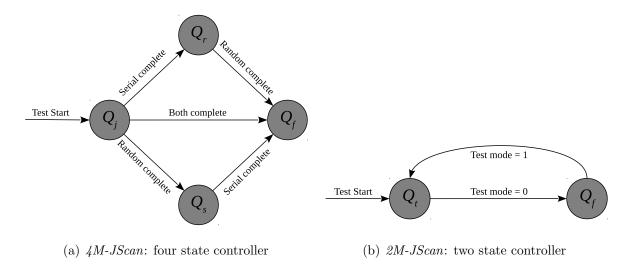

|   |     | 4.3.4         | Test Control Mechanism                                         |           |

|   |     | 4.3.4         |                                                                |           |

|   |     | 4.3.6         | Functionality                                                  |           |

|   |     | 4.3.7         | Computation of Test Parameters                                 |           |

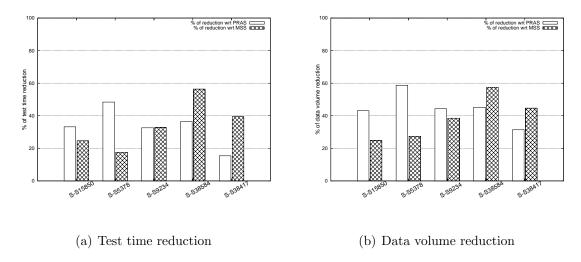

|   | 4.4 |               | imental Result and Discussion                                  |           |

|   | 7.7 | 4.4.1         | Analysis on Different Possible Configurations                  |           |

|   |     | 4.4.2         | Configurations by Different <i>P-random</i> Addressing         |           |

|   |     | 4.4.3         | Alteration in Dimension of <i>P-Serial</i> and <i>P-random</i> |           |

|   |     | 4.4.4         | Diagnosis, Delay Test and Debugging                            |           |

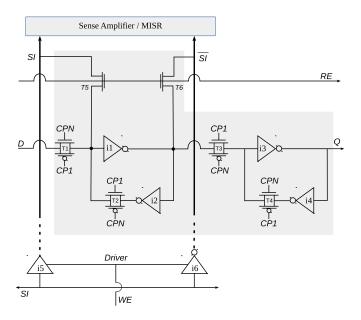

|   | 4.5 |               | Cell Design for <i>Joint-scan</i> Architecture                 |           |

|   | 4.0 | 4.5.1         | Conventional Scan Cell                                         |           |

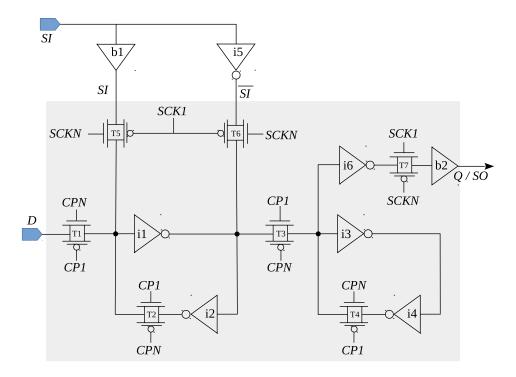

|   |     | 4.5.1 $4.5.2$ | Proposed Scan Cell Design                                      |           |

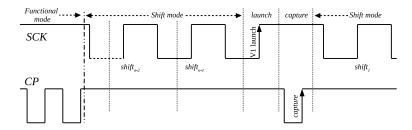

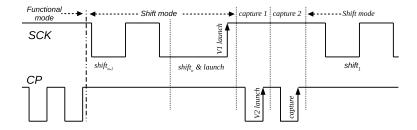

|   |     | 4.5.3         | Application of Test Vectors                                    |           |

|   |     | 4.5.3         | Post Layout Simulation Results                                 |           |

|   |     | T.U.T         | TOOK Dayout outhander results                                  | J 🛨       |

CONTENTS

|   | 4.6       | JScan Implementation using Proposed Scan Cell             | 127       |

|---|-----------|-----------------------------------------------------------|-----------|

|   |           | 4.6.1 Proposed Scan Cell as a RAS Cell                    | 128       |

|   |           | 4.6.2 Implementation, Experimental Results and Discussion | 129       |

|   | 4.7       | Conclusion                                                | 133       |

| 5 | Sen       | n Chain Diagnosis                                         | 134       |

| J | 5.1       |                                                           | 134       |

|   | 0.1       |                                                           | 134 $137$ |

|   |           |                                                           | 139       |

|   | 5.2       |                                                           | 140       |

|   | 5.3       |                                                           | 147       |

|   | 5.4       |                                                           | 150       |

|   | 5.4 $5.5$ | •                                                         | 151       |

|   | 0.0       | Conclusion                                                | 101       |

| 6 | Sca       | an Flip-flop Design                                       | 152       |

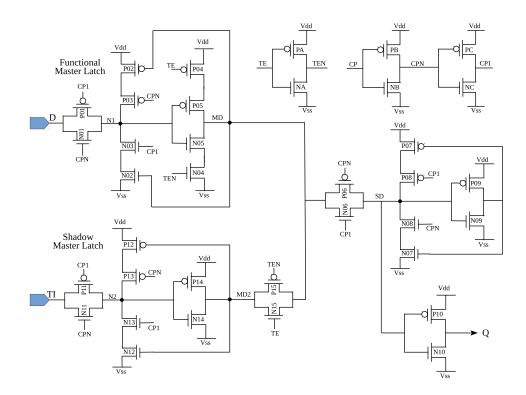

|   | 6.1       | Elimination of Performance Penalty of Scan                | 153       |

|   |           | 6.1.1 Preliminaries and Proposed Scan Cell                | 154       |

|   |           | 6.1.2 Test Quality Considerations                         | 159       |

|   |           | 6.1.3 Experimental Results                                | 161       |

|   | 6.2       | Scan Cell Design for Test Power Minimization              | 162       |

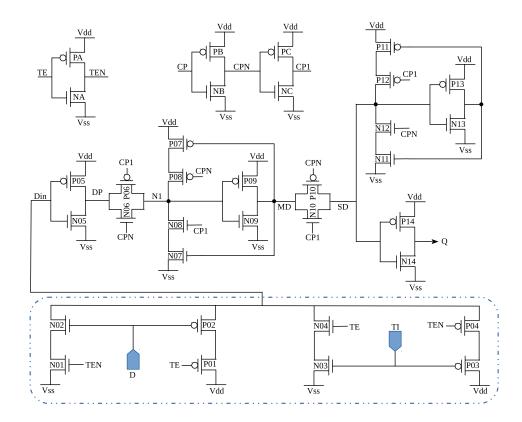

|   |           | 6.2.1 Schematic Design of Proposed Scan Cell              | 164       |

|   |           | 6.2.2 Test Quality Consideration                          | 168       |

|   |           | 6.2.3 Experimental Results                                | 171       |

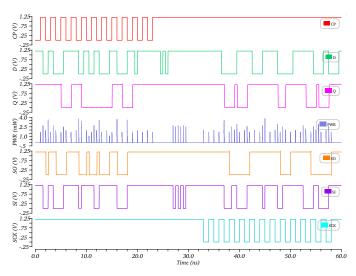

|   | 6.3       | Enabling LOS Test with Slow Scan Enable                   | 173       |

|   |           | 6.3.1 Introduction                                        | 173       |

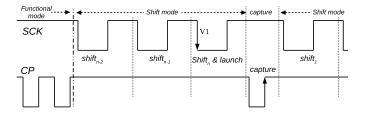

|   |           | 6.3.2 Proposed Scan Flip-Flop Design                      | 176       |

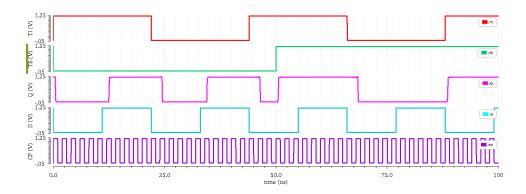

|   |           | 6.3.3 Application of Test Vectors                         | 178       |

|   |           | 6.3.4 Experimental Results                                | 181       |

|   | 6.4       | Conclusion                                                | 181       |

| 7 | Cor       | nclusion and Future Scope                                 | 183       |

|   | 7.1       | • • • • • • • • • • • • • • • • • • •                     | 184       |

|   | 7.2       |                                                           | 187       |

|   |           |                                                           | 187       |

|   |           |                                                           | 188       |

|   |           | 7.2.3 Scan Cell Design                                    | 188       |

## List of Tables

| 3.1  | Test time and area overhead comparison                           | 63  |

|------|------------------------------------------------------------------|-----|

| 3.2  | Test time and design overhead                                    | 69  |

| 3.3  | Fault coverage and design overhead                               | 73  |

| 3.4  | Area overhead comparison                                         | 80  |

| 4.1  | Variation in loading/unloading (l/u) time                        | 98  |

| 4.2  | Circuit specification of S-ISCAS89 benchmark                     | 105 |

| 4.3  | Peak and Average Power in comparison with MSS                    | 106 |

| 4.4  | Test time in contrast with JScan [210], PRAS [23] and MSS        | 107 |

| 4.5  | Test data volume in contrast with JScan [210], PRAS [23] and MSS | 108 |

| 4.6  | Four possible configurations of <i>Joint-scan</i>                | 110 |

| 4.7  | Layout Area and Leakage Power                                    | 124 |

| 4.8  |                                                                  | 126 |

| 4.9  | Routing wire length (WL) in JScan, PRAS, and MSS                 | 130 |

| 4.10 |                                                                  | 131 |

| 5.1  | Scan chain state in different diagnosis phases                   | 140 |

| 5.2  |                                                                  | 146 |

| 5.3  |                                                                  | 148 |

| 5.4  |                                                                  | 149 |

| 5.5  |                                                                  | 151 |

| 6.1  | Post Layout Simulation Results at $500MHz$                       | 161 |

| 6.2  |                                                                  | 172 |

| 6.3  | Post Layout Timing Simulation Results at $500MHz$                | 181 |

# List of Figures

| 1.1<br>1.2<br>1.3 | Basic VLSI test principle                                                                               | 3<br>11<br>14 |

|-------------------|---------------------------------------------------------------------------------------------------------|---------------|

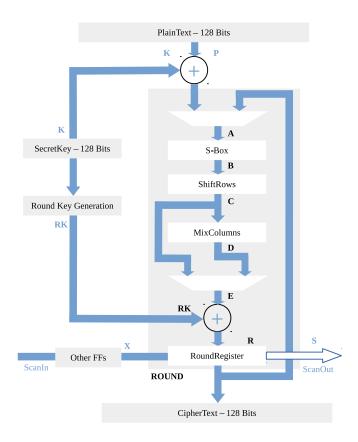

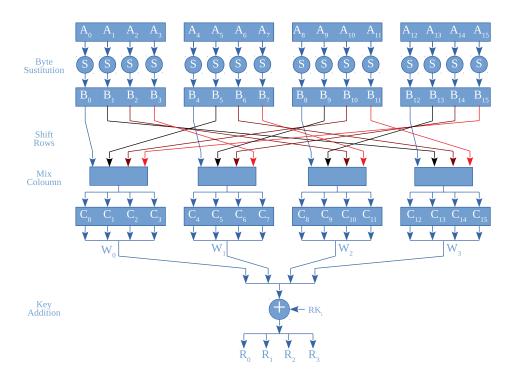

| 2.1<br>2.2        | Schematic diagram of an $AES$ cipher along with scan design Internal structure of an $AES$ cipher [151] | 24<br>26      |

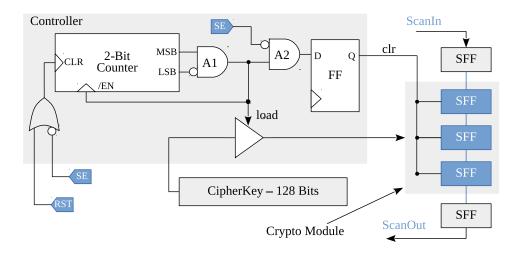

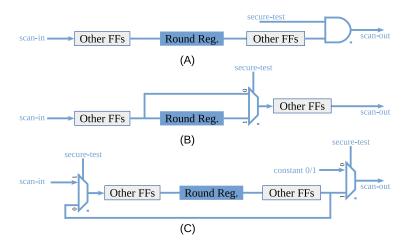

| 3.1               | A secure scan test controller proposed in [52]                                                          | 45            |

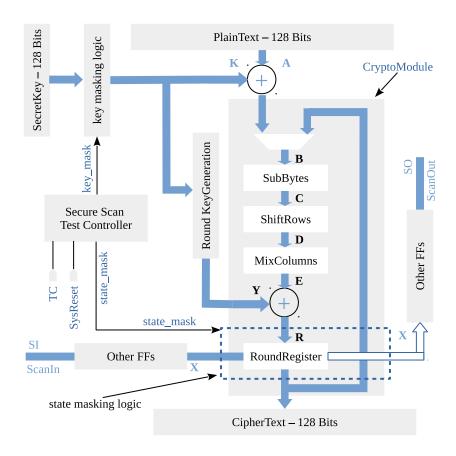

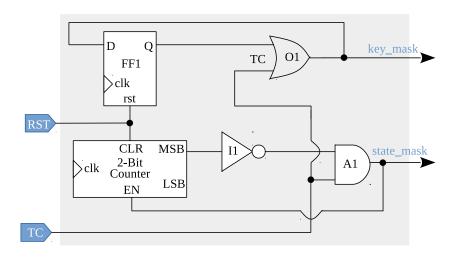

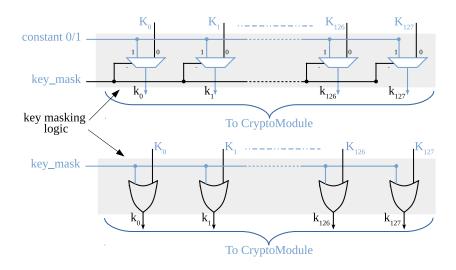

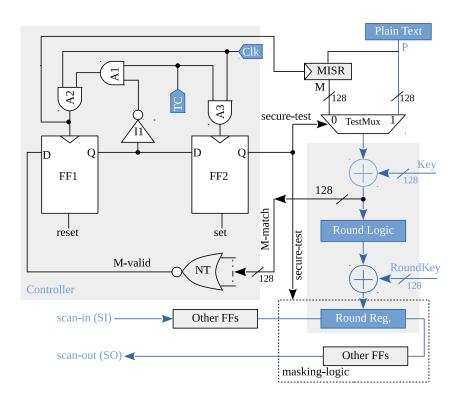

| 3.2               | Proposed secure scan test technique schematic [12]                                                      | 48            |

| 3.3               | Secure scan test controller schematic [12]                                                              | 49            |

| 3.4               | Encryption key masking logic schematic                                                                  | 50            |

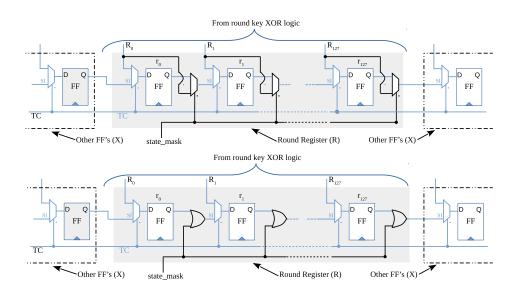

| 3.5               | Round register state masking logic schematic                                                            | 51            |

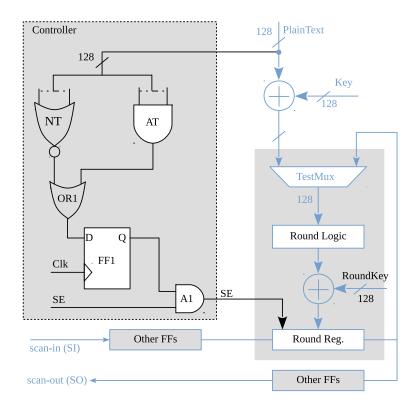

| 3.6               | Proposed secure scan test technique schematic [13]                                                      | 56            |

| 3.7               | Round register state masking logic schematic                                                            | 59            |

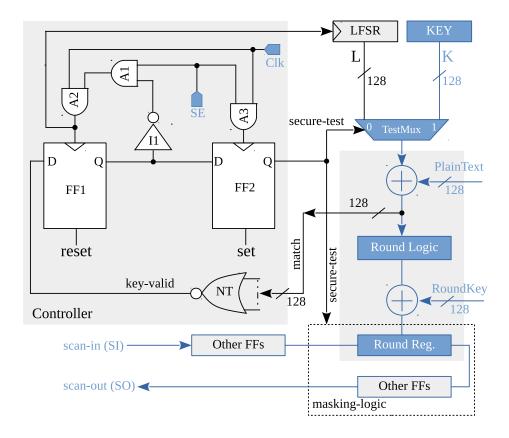

| 3.8               | Schematic design of the proposed secure scan test architecture                                          | 64            |

| 3.9               | Schematic diagram of the proposed secure scan design                                                    | 70            |

| 3.10              | Schematic design of the proposed technique                                                              | 75            |

| 3.11              | Schematic diagram of the proposed secure scan design                                                    | 81            |

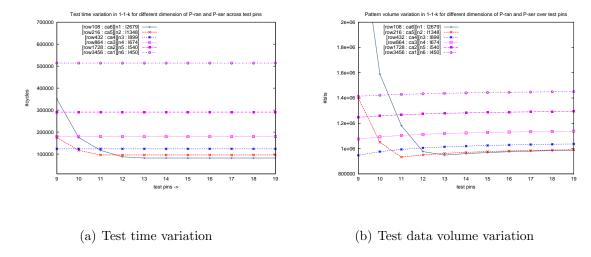

| 4.1               | Test time and data volume reduction by $4M$ - $JScan$ architecture [207]                                | 94            |

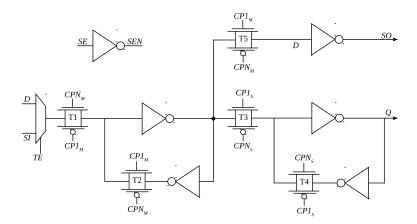

| 4.2               | Proposed two-mode Joint-scan Architecture (2M-JScan)                                                    | 96            |

| 4.3               | State transition machine of mode control in 4M-JScan and 2M-JScan                                       | 100           |

| 4.4               | Clustering of scan cells using $1D$ clustering algorithm                                                | 103           |

| 4.5               | Test time and data volume variation in MSS, PRAS, and JScan with                                        |               |

|                   | respect to increasing test pin count in $ss15850$ design                                                | 109           |

| 4.6               | Test time and data volume for different configurations in $1-1-p$                                       | 111           |

| 4.7               | Serial shifting of column address: from single line to $log_2c$ number of lines,                        |               |

|                   | where $c$ is number of columns in $P$ -random                                                           | 112           |

| 4.8               | Test time and data volume variation in $1-1-k$ configuration as the                                     |               |

|                   | change of <i>P-random</i> and <i>P-Serial</i> dimension                                                 | 113           |

| 4.9               | Conventional scan cell and performance overhead of scan design                                          | 116           |

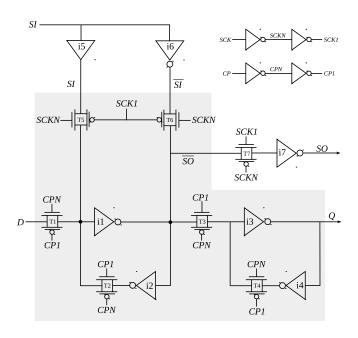

| 4.10              | Schematic design of the proposed scan flip-flop                                                         | 117           |

| 4.11              | Launch and capture in <i>stuck-at</i> test                                                              | 121           |

| 4.12              | Launch of $V_1$ , $V_2$ , and capture in $LOC$ test                                                     | 123           |

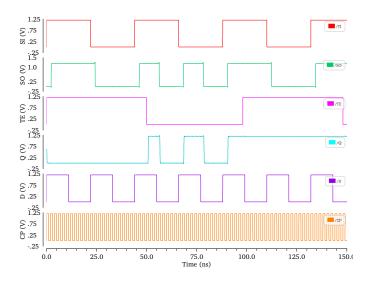

| 4.13 | Post layout timing waveform at $500MHz$                                      | 126 |

|------|------------------------------------------------------------------------------|-----|

| 4.14 | Progressive Random Access Scan $(PRAS)$ Cell [23]                            | 129 |

| 5.1  | Example Scan chain with a single $sa0$ fault                                 | 138 |

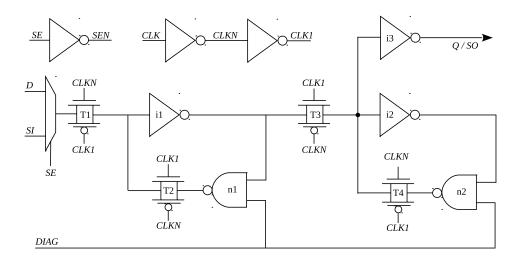

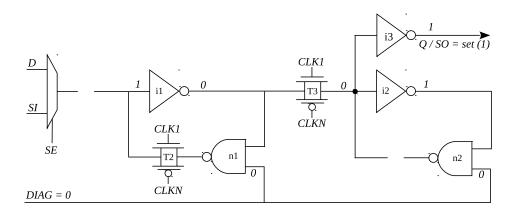

| 5.2  | Proposed scan cell design with set/reset circuitry                           | 142 |

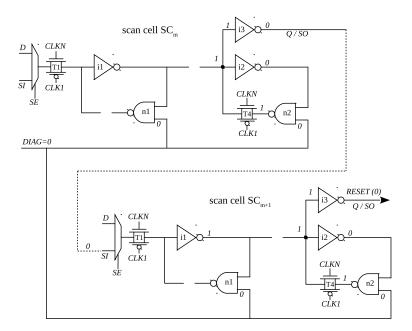

| 5.3  | Set operation in proposed scan cell                                          | 142 |

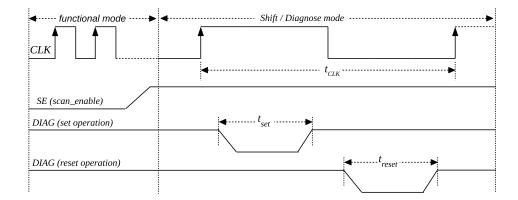

| 5.4  | Reset operation in proposed scan cell                                        | 143 |

| 5.5  | Timing requirement for <i>set/reset</i> operation                            | 145 |

| 5.6  |                                                                              | 149 |

| 6.1  | Transistor level implementation of the reference scan flip-flop [197, 245] . | 154 |

| 6.2  | Proposed Scan Flip-Flop Implementation                                       | 156 |

| 6.3  | Post layout timing diagrams at clock frequency of $500Mhz$                   | 160 |

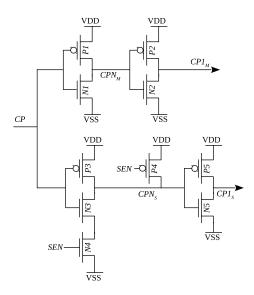

| 6.4  | Proposed scan flip-flop schematic design                                     | 165 |

| 6.5  | Circuit to generate locally derived clock signals                            | 166 |

| 6.6  | Timing requirements for scan enable in <i>stuck-at</i> and <i>LOC</i> test   | 169 |

| 6.7  | Post layout timing waveform at $500MHz$                                      | 171 |

| 6.8  | Proposed scan flip-flop design                                               | 176 |

| 6.9  | Timing requirements for scan enable in <i>stuck-at</i> and delay test        | 179 |

## Chapter 1

## Introduction to VLSI Test

The semiconductor fabrication process has made tremendous advancements in recent years. With ever decreasing feature size it has become possible to integrate billions of transistors on a single chip with transistor densities as high as 100 million transistors per square millimeter  $(MTr/mm^2)$  of chip area [100, 204]. The fabrication process for these present day integrated circuits (IC) has become extremely complex with more than 30 layers and over 1000 process steps [102]. At the heart of the IC fabrication lies the lithography process, which prints the patterns on the silicon wafer. Today's stateof-the-art fabrication lines are based on 193nm immersion lithography. Since 193nm light can not directly define a feature which is smaller than it's own size, hence complex optical techniques along with multiple patterning process are used to define features which the modern day chips require. This has significantly increased the total number of lithography steps required to fabricate a chip. It takes almost 80 lithography steps to fabricate today's most complex of chips [205]. Furthermore, the alignment of all the lithography steps is very crucial to correctly define the features. Also the design for manufacturability (DfM) rules has increased dramatically because of the printing challenges in currently used lithography technique. The explosion in design rules is mainly because of the huge difference between 193nm wavelength and the feature sizes needed to fabricate the modern day chips [39]. With ever decreasing feature sizes the design rules are increasing and becoming more restrictive in what are manufacturable

layout patterns. All these factors have led to a very little tolerance for variations in layout patterns. Also, with very small feature sizes the devices have become more vulnerable to process variations. A small perturbation in process parameters may cause significant variations in device parameters across dies and wafers. As a result, the probability of occurrence of manufacturing defects during fabrication process has increased.

A small defect may lead to a faulty transistor or faulty interconnect wire. The manufacturing defects can impact the chip in two ways: either the chip will fail to function at all or it will fail to function at target frequency. The former lead to yield loss while the latter causes decrease in revenue. Since there is always probability of a fabricated chip being faulty, testing of all the manufactured chips is necessary in order to segregate the faulty chips from the good ones. The faulty chips must be screened out before they are assembled into printed circuit boards, which in turn must be tested before integration into systems. This is because of the commonly agreed upon rule of ten which states that the cost of finding the faulty chip increases ten times as we move from one level of integration to another i.e., chip to PCB to system and finally to field operation [36, 59, 219].

### 1.1 VLSI Testing

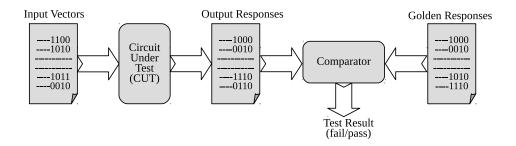

So, how do we test a chip? We apply a sequence of input patterns at the primary inputs of the chip and record the corresponding output responses at the primary outputs. These recorded output responses are compared with the predetermined responses also called golden responses. The golden responses are generated through circuit simulation. The input pattern which produces an erroneous output response in case there is fault present in the circuit is called a test pattern and the corresponding response a test response. The test patterns and test responses together are called test data. If the recorded test responses match with the golden responses (simulated correct responses) that means the fabricated circuit or chip is correct else the chip is flagged as faulty [36, 73]. The basic test principle is depicted in Figure 1.1.

Figure 1.1: Basic VLSI test principle

The testing of logic circuits consists two steps: 1.) generation of test patterns for the circuit under test (CUT), and 2.) application of test patterns to the CUT. The test development and application time decide the test quality and test cost which are interdependent. The test quality depends upon the thoroughness of the test, however, a large test set increases the test development and application time and hence test cost. Furthermore, a large test set also increases the time-to-market which may severely impact the financial success of the product in the market [202]. A good test is supposed to satisfy the following three requirements [36]:

- (i) It should detect all the possible defects

- (ii) Test development time must be economical

- (iii) Test application time must be economical

The first requirement ensures the quality of shipped products. The second and third requirement come from the test cost. Presently, the test cost constitute a large part of the overall product cost [39, 66, 97, 105, 166, 247]. The test cost for present day systems can go as high as 40% of the total product cost [219]. Hence, in order to produce quality products at economical price, a test set should fulfill all the above three requirements.

### 1.1.1 Functional vs Structural Testing

Historically, the testing of chips was done using functional test vectors. The functional testing is an extension of design verification which is used to verify the correctness of

the design [202]. The functional test uses verification vectors which are based on logical relationship between the inputs and outputs of a circuit. The quality of functional tests depends upon the thoroughness of the test vectors. Since, the functional test patterns are generated for verifying a specific functional scenario, hence may not detect all possible defects. However, the functional test guarantees detection of all possible defects if done exhaustively, i.e., all possible combinations of functional input vectors are exercised. The number of functional test vectors required to test a chip exhaustively depends upon the number of primary inputs and increases exponentially. The number of functional test vectors are given by  $2^N$ , where N is the number of primary inputs. Most of the practical ICs have more than hundreds of functional inputs which makes it impossible to test them using functional testing.

As the logic circuit size and functionality evolved over the years, the cost of functional test development and application became unviable [66, 202]. The functional test technique has been largely replaced by structural test technique in manufacturing test. A small set of functional test patterns are still used as top up patterns to structural patterns in structural testing. The structural testing, first proposed by Richard D. Eldred [70], is based on the specific structure of the circuit, i.e., type of gates, interconnects, and netlist. Unlike functional testing, the structural test pattern count increases linearly with circuit primary inputs [73]. One of the greatest advantage of structural testing over functional testing is that it allows to develop automatic test pattern generation (ATPG) algorithms [36]. These ATPG algorithms are based on fault models. A fault model is an abstract representation of physical defect at functional level. Since the real manufacturing defects can be so many, it is almost impossible to generate test vectors to detect all the physical defects. The fault models accurately reflects the logic level behavior of the defect, and also allows to generate the test vectors and fault simulate them in a computationally efficient way [219].

#### 1.1.2 Fault Models

Many fault models have been proposed over the years [1]. The behavior of all types of defects can not be modeled accurately by a single fault model and hence a combination of fault models is used for test vector generation and fault simulation [202]. The commonly used fault models across industry and academia are *stuck-at fault* [75] model, *delay fault* model, *transistor fault* [38, 216] model, and *bridging fault* [137] model.

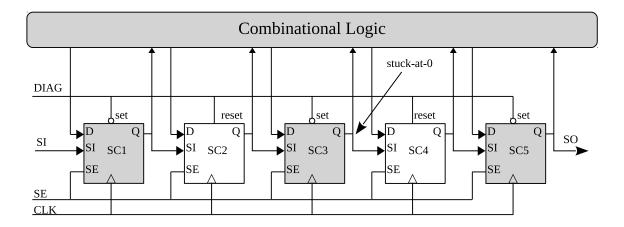

#### Stuck-at fault model

The stuck-at fault model is the most fundamental to structural testing of logic or digital circuit. The stuck-at fault model uses gate level fault modeling in which the faults are modeled only on the interconnects (or net) connecting the logic gates and the logic gates themselves are considered fault free. The interconnect can be subjected to two types of stuck-at faults: stuck-at-1 (s-a-1 or sa1), and stuck-at-0 (s-a-0 or sa0). While the s-a-1 fault permanently sets the faulty net to 1 (logic high), the s-a-0 fault permanently sets the faulty net to 0 (logic low).

Since a circuit can have multiple faults at a time, the total number of faults or stuck net combinations in a circuit with n lines or nets can be  $3^n - 1$ . This model is called multiple stuck-at fault model and is not used because even a moderate value on n will result in a large number of multiple stuck-at faults [36]. As a result, the common practice is to use single stuck-at fault model which is characterized by the three properties given below:

- (i) Only one net is faulty in the circuit

- (ii) The faulty line either can have s-a-1 or  $s-a-\theta$  fault

- (iii) The fault can be on an input or output of a logic gate.

Since the single stuck-at fault model restricts the number of faults that can exist in a circuit to 1, an n line circuit at most can have 2n faults. This number is further reduced considerably by fault collapsing process which is based on fault equivalence [1].

On an average the fault collapsing reduces the total number of faults by 50% to 60% [36]. The single *stuck-at* fault model is simple and computationally efficient for test pattern generation and fault simulation. Furthermore, the total number of modeled faults in this fault model increase linearly with number of circuit nets, which in case of functional testing increase exponentially with circuit size. All these advantages lead to the adoption of structural testing in manufacturing test.

#### Delay fault model

The other fault model currently in practice is delay fault model. The defects which do not change the functionality of the circuit, however, degrade the performance of the circuit are modeled by delay fault model. The delay faults increases the combinational delay of the circuit and makes it to exceed the clock period [113]. The delay faults are becoming more prevalent with decreasing feature size. The delay faults can not be detected by stuck-at fault test. Hence, a separate type of test called delay test is used to detect delay defects. The delay fault detection requires creation of a transition at the fault site and then propagation of that transition to a observable circuit node which could be a primary output (PO) or a clocked flip-flop. The creation of a transition requires a vector pair,  $\langle V_1, V_2 \rangle$ , at the primary inputs (PI) of the combinational circuit [219]. The most commonly practiced delay fault models are transition delay fault (TDF) model [48, 128, 218], path delay fault (PDF) model [192], and segment delay fault model [92, 93]. In most of the delay fault models, the gate input to output delay and interconnect delay are combined together and are represented by gate delay.

Transition Delay Fault (TDF) model assumes that only one gate in the circuit has delay fault. Further, it is assumed that the delay of the fault site is large enough to cause the propagation delay of signal transition passing through the fault site or line exceed the clock period. The TDF model lump the fault at a single gate or line. Hence propagation delay of every path, irrespective of whether it is a short path or long path, which passes through the faulty line or gate exceeds the clock period of circuit. Therefore, the TDF model is also called a gross-delay defect

model. Each gate in the circuit can be subjected to two types of transition delay faults: slow-to-rise fault and slow-to-fall fault. The number of possible transition delay faults in a circuit is 2N, where N is the total number of gates or lines. The number of TDF's are relatively small and increases linearly with number of gates [219]. The assumption of a single gate affected by delay defect and failing of all paths which pass through that gate is not very realistic. However, because of the practical simplicity of TDF model it is most frequently used delay fault model. Furthermore, the ATPG of stuck-at faults can be easily modified to generate TDF test patterns [113, 202].

- Path Delay Fault (PDF) model on the other hand assumes that the delay defect is distributed over the whole combinational path and hence also called distributed delay defect model. In PDF model it is assumed that the cumulative delay of the combinational path, which includes the logic gates and interconnects delays, is large enough that it exceeds the clock period. Similar to the TDF model each path in PDF model may subject to slow-to-rise and slow-to-fall faults corresponding to rising and falling transitions at the starting point of the path. The total possible number of PDF's can be 2N, where N is the total number of combinational paths that exists in a circuit. As the number of paths in a circuit increases exponentially with the circuit size it is practically impossible to enumerate all paths in a practical circuit. Despite the fact that PDF model is more realistic than the TDF model, it is not exercised for all the circuit paths. The PDF model is used only for a small set of timing critical paths [130, 176, 246].

- Segment delay fault (SDF) model is another fault model which offers a trade-off between TDF model and PDF model [113]. The basic assumption in this model is that the delay defect is distributed over a segment of a path or affects several gates in a local region which forms a segment of a path. Further, it assumes that all the paths passing through the affected segment will have delay fault. The length L of the segment can be anywhere between  $L_{max}$  and 1, where  $L_{max}$  represents the

number of gates in the longest path, and L = 1 represents a single gate. When  $L = L_{max}$ , the SDF model becomes equivalent to PDF model. In case, when L = 1, the SDF model becomes equivalent to TDF model. The length of path segment can be decided based on the available manufacturing defect statistics.

#### Transistor fault models

Unlike the *stuck-at* and *delay fault* models which are gate level fault models the *transistor* fault model is a switch level fault model [219]. In this fault model it is assumed that a *MOSFET* transistor can be subjected to two faults: *stuck-open* and *stuck-short* also referred as *stuck-off* and *stuck-on*. In a *stuck-open* fault, the *MOS* transistor always remains in *open* state and in *stuck-short* fault, the *MOS* transistor always remains in *shorted* state. Further, it is assumed that only one transistor is faulty out of the total transistors which realize the *CMOS* logic gate [36].

Transistor faults in *CMOS* logic circuits can not be detected by stuck-at fault test. The output of a logic gate containing the faulty transistor with stuck-open fault remains in a floating state. To detect a transistor *stuck-open* fault, a sequence of two vectors is applied. The first vector initializes the affected output node and the second vector which is a *stuck-at* vector detects the presence of the fault. If the two vectors sequence produces a hazard at the output of the faulty gate then fault detection can not be guaranteed [106, 163].

The transistor *stuck-short* fault on the other hand produces a conducting path between power supply and ground supply rails. The fault is activated by a specific input combination at the gate inputs. Once activated, the fault can affect the output logic level of the gate containing the faulty transistor. The output logic level of the affected gate depends upon the impedance of the shorted transistor. The logic level of the output node of the affected gate may or may not be interpreted as an invalid state by the inputs of the gates driven by the faulty gate. However, the transistor *stuck-short* fault

is detected by quiescent current measurement called  $I_{DDQ}$  test. The transistor stuck-open and stuck-short fault modeling has been extensively studied by the test community [69, 124, 127, 149, 183, 184]. However, these fault models have not been assimilated

into VLSI test flow. The stuck-at fault test detects the transistor stuck-open faults.

However, the fault coverage of transistor stuck-open faults achieved by stuck-at test lags 10% to 15% behind the fault coverage of stuck-at faults [6].

#### Bridging fault model

The bridging fault model represents a short between two (or more) signal wires or nets. The bridging fault commonly happens between signal lines or interconnects which are physically very close to each other in the physical layout. The short can happen between transistor terminals or between interconnects of transistors and logic gates [219]. The bridging fault is modeled at the logic gate level or transistor level [202]. The bridging fault is similar to the real defects which happen in silicon and hence is also called defect-oriented fault [169, 175].

There are many bridging fault models available in literature [1, 66]. The very first bridging fault model called wired-AND/wired-OR model is a simple fault model and is independent of the bridge resistance and the location of the bridged nodes [137]. There are more complex models available which take into account the bridge resistance and location information [2, 135]. Another complication in modeling of bridging faults is formation of feedback paths which may cause oscillation. The wired-AND/wired-OR fault model was developed for bipolar devices and does not model the behavior of bridges in CMOS devices. The bridging defects in CMOS devices are modeled by dominant bridging fault model in which it is assumed that the shorted net is dominated by the powerful driver. It has been shown that a test set which detects all the dominant bridging faults is also guaranteed to detect all wired-AND/wired-OR faults [219]. A recent fault model called dominant-AND/dominant-OR accurately models the behavior of resistive shorts which were not modeled by dominant bridging fault model [198]. The bridging faults closely match with the real defects which commonly occurs in circuit fabrication.

The bridging faults can be detected by  $I_{DDQ}$  test. However, with continuously decreasing feature size the leakage current in CMOS devices is increasing and the change in  $I_{DDQ}$  current due to bridging fault may not be reliable detectable [219]. Also it has been shown that many bridging faults are detected by N-detect single stuck-at fault test vector set with very high fault coverage [77, 82, 155, 164].

#### 1.1.3 Sequential Circuit Testing

Most of the digital system of significant size are sequential in nature. These sequential circuits have internal memory states which makes testing of sequential circuits very difficult. The sequential circuits have internal states which are unknown at the start of the test. To test the sequential circuit, first it must be brought into a known state. Then the fault is activated and after that the fault effect is propagated to the primary outputs. Thus a sequential test can have a long sequence of test vectors which must be applied in a specific order. There are mainly two techniques for test generation for single-clock synchronous sequential circuits: time-frame expansion [114, 157] and simulation-based [35, 182] method.

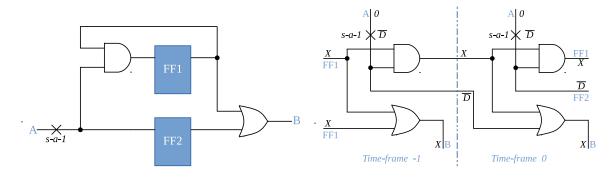

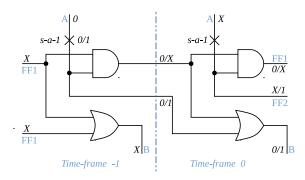

The time-frame expansion method uses a gate level model of the circuit and uses a combinational ATPG [81] for test generation. To use combinational ATPG for sequential test pattern generation, the sequential circuit needs to be unrolled into a larger combinational circuit. To unroll a sequential circuit, all the state elements are removed from the circuit and the outputs of the state elements are made into pseudo primary inputs (PPI). Similarly, the inputs of the state elements are made into pseudo primary outputs (PPO). Now this transformed form of circuit is replicated multiple times as per the test generation requirement. An example sequential circuit along with its time-frame expansion is shown in Figure 1.2. It can be seen from the expanded circuit shown in Figure 1.2(b) that the PPI of one frame is connected to PPO of the preceding frame. The PPI of the very first frame (i.e., left most frame) are initialized to don't-care or X values. This process of unrolling the sequential circuit into a combinational circuit is called time-frame expansion.

- (a) A sequential circuit for test generation

- (b) Test generation with five valued logic

(c) Test generation with nine valued logic

Figure 1.2: Sequential circuit test generation using time-frame expansion method [36]

Now to generate the test pattern the fault is copied in every time-frame. To use the combinational ATPG for the expanded circuit a nine-valued logic is required [36]. Because the five-valued logic which is used for combinational ATPG can not handle initialization fault of state elements, a situation depicted in Figure 1.2(b). To overcome this issue a nine-valued logic system is required which can handle the state initialization issue due to faults in the state elements [144]. It can be observed in Figure 1.2(c) that the nine-valued logic can successfully resolve the initialization problem and generate a valid test. To justify a state the ATPG may have to try  $9^{N_{ff}}$  state vectors or time-frames in the worst case scenario before it declares a fault untestable. With a moderate size state vector  $N_{ff}$  (number of flip-flops) the total number of distinct state vectors become very large. Further, time-frame expansion method is very inefficient for sequential circuit with cyclic structures, multiple-clocks, and asynchronous circuitry [36]. Hence, sequential test generation based on time-frame expansion method is an intractable problem.

The simulation-based method uses a fault simulator and test pattern generation programme. Among simulation-based techniques the concurrent fault simulator (CFC) along with genetic algorithms can provide good efficiency [8, 136]. The existing sequential test pattern generation techniques can not handle the complexity of present day circuits. The use of sequential test generation techniques is practically impossible for present day circuits. The solution to this problem is use of combinational ATPG along with the Scan DfT architecture also called scan design. The main advantage of scan design is that it allows to test a sequential circuit like a combinational one.

### 1.2 Design for Testability

The Design for Testability (DfT) techniques are the design practices that are used to improve the testability of complex logic designs. There are two types of DfT approaches: ad-hoc and structured. The ad-hoc techniques are based on finding testability problems in circuit with manual inspection, and then inserting test points. Algorithmically generated testability measure are also used to find signals with weak controllability and observability and then required changes are made in the design. As the circuit complexity increases, manual inspection becomes difficult. Also the algorithmically generated testability measures are not accurate [5]. Furthermore, the ATPG can not provide a test set with adequate fault coverage for logic circuits with ad-hoc DfT structure.

The complex logic designs require a structured DfT approach to achieve acceptable fault coverage [68]. In structured DfT techniques extra circuitry is added to the regular circuit in a systematic way. Presently, scan design and built-in self-test (BIST) are the two commonly used structured DfT architectures [36]. The BIST technique is based on test signature analysis which is a statistical property of the circuit [229]. The correctness of the chip is determined by comparing the test response signature with the golden signature which is stored on-chip. The signature is generated by compacting the responses of the pseudo-random test sequences applied to the circuit [25]. The test sequence and the corresponding signature are generated on-chip. The test sequence is generated using an

on-chip LFSR [65, 83] and the corresponding signature is generated using a MISR which is also implemented on-chip. The BIST for logic testing as well as for memory testing is available and are called logic-BIST (or LBIST) and memory-BIST (or MBIST) respectively. The MBIST is commonly practised for memory testing, however, the use of LBIST is very limited. The LBIST technique does not require an ATPG programme for test generation and an ATE for test application, which is a very costly equipment. However, the LBIST has low fault coverage and high area overhead as compared to scan design [36]. Further, the BIST technique suffers from poor diagnosis capability and signature aliasing [230, 231].

#### 1.2.1 Scan Architecture and Scan Testing

Presently, scan-based DfT is the only practical test architecture available that can test a present day highly complex VLSI chip with a satisfactory test coverage. The concept of scan was already in use for system level test, however its application in structural testing was first proposed by Williams et al. [228]. It was first adopted by IBM and NEC, which used various implementations of scan design [68]. Later, as the circuit complexities increased, scan DfT architecture gained popularity because of its simplicity and effectiveness in testing complex designs.

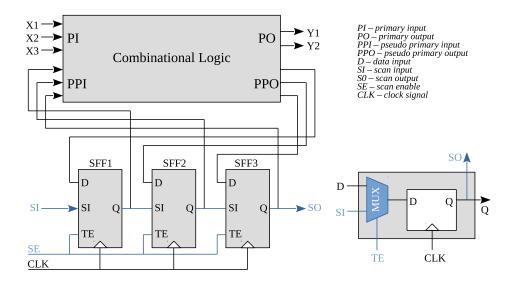

In a scan-based DfT architecture also popularly known as scan design, the main idea is to get controllability and observability of every flip-flops in the CUT. This is achieved by replacing sequential element or flip-flop in a circuit by a scan cell. The scan design in which each and every flip-flop in the CUT is replaced by a scan cell is called full scan design. The main advantage of full scan design is that it allows to test a sequential circuit just like a combinational circuit. Moreover, a combinational ATPG can be used to generate the test vectors and corresponding responses.

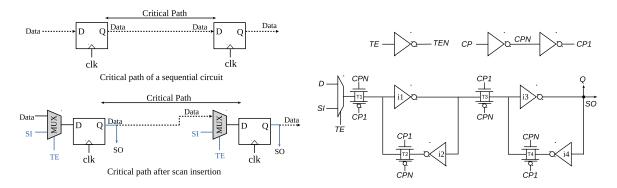

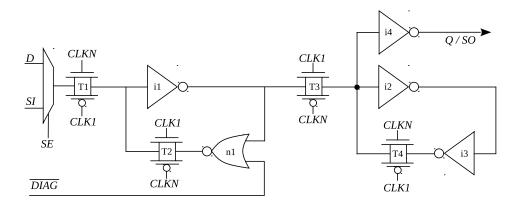

The scan architecture along with the scan cell is depicted in Figure 1.3. The scan cell is a multiplexed input D-type flip-flop. In addition to regular data or functional input (D), the scan cell has one extra input called test or scan input (SI). The scan multiplexer is controlled by a global control signal called scan enable (SE) or test enable

Figure 1.3: Serial scan DfT architecture and basic scan cell [36]

(TE). Using the test enable signal either the regular functional input D or the test input SI can be selected by the multiplexer. The scan design basically adds an extra mode of operation to the circuit functionality which is popularly called scan mode or test mode. During scan mode, all the scan cells are connected serially and form one or more serial shift register(s) popularly known as scan chain(s) among the test community. The scan chain has a scan-in (SI) and scan-out (SO) pin which are controlled through primary input/output (I/O) pins. By using the test enable signal, which is available at users disposal, the circuit can be switched between functional and scan mode anytime. During the scan mode, scan chains can be loaded and unloaded serially via the scan I/O pins. By using the scan feature, the circuit can be brought into any known state and the present state of the circuit can be observed.

The scan based testing is carried out in two steps: test generation and test application. While the test generation is carried out using an ATPG program the test application is performed by an Automatic Test Equipment (ATE). During test application the following operations are performed: test vector shift-in through SI, test vector launch, test response capture (this is performed in functional mode), and test response shift-out through SO. The shift-in and shift-out operations are performed simultaneously. While the next test vector is being shifted-in the response from the previous test vector

is shifted-out. For a scan chain of length l, where l is the number of scan cells in a scan chain, l shift cycles are required to load/unload the test vector/response. Hence the test time directly depends upon the scan chain length. To reduce the test time multiple parallel scan chains are formed with independent scan-in and scan-out port. The scan design with multiple scan chains is generally called multiple serial scan (MSS). The number of shift cycles required to load a test vector depend upon the length of the scan chain. The last shift-in cycle also launches the test vector. The test response is captured by switching the circuit in functional mode and applying a functional clock pulse. The captured response is serially observed at the scan-out pin by the ATE and compared with the golden response. Depending upon the comparison result the CUT is flagged as faulty or fault free.

#### Partial scan design

A variant of full scan design which is called partial scan design, includes only a subset of the total flip-flops in the CUT into the scan chain. It provides a trade-off between ease of testing and the cost associated with the full scan design [28, 200, 237]. The partial scan design performs better in terms of test time and test power dissipation, however, suffers from comparatively lower fault coverage. The increasing circuit complexity has forced the industry to abandon partial scan design, which necessitates a computationally demanding and unaffordable sequential ATPG (or combinational ATPG with time-frame expansion), and to rather adopt full scan despite its cost.

#### Random Access Scan Design

The full scan and partial scan both uses serial shift operation for loading/unloading of test vectors/responses. This causes a lot of switching activity in the scan cells, which also propagates in the combinational logic. Because of this a lot of unnecessary power dissipation occurs in the *CUT* during scan shift operation. As observed by some of the recent studies the test power dissipation could be significantly higher than the functional power and poses a big challenge for test engineers. The high test power dissipation

restricts the internal scan chain shift frequency at nearly 10MHz to 50MHz only. An alternate to serial scan design is Random Access Scan (RAS) design which can effectively reduce the test power along with test time and test data volume. The RAS was first proposed by Ando in 1980 [17]. In RAS the test vector loading is performed in a random-access memory (RAM) like fashion. The write operation for care bits of a test vector care bit and read operation care bit of test response are performed bit-by-bit. Hence there is no serial shift operation and hence very less power dissipation. Also, 90 to 95% bits in a test vector are don't-care bits, there is a significant reduction in test data volume and test application time. Literature shows that RAS can greatly reduce test application time and test data volume along with a reduction in test power up to 99% [3, 20, 21, 23, 143]. It shows that RAS architecture has the potential towards solving the scan shift frequency issue. The main issue that RAS architecture faces in its practical implementation is the routing congestion.

### 1.2.2 Scan based Testing

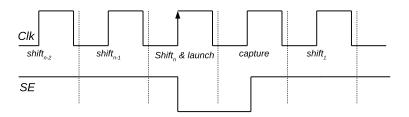

The scan design is commonly used to exercise static (stuck-at) and timing (delay) test. The procedure to carry out stuck-at and delay test is briefly explained below.

#### Stuck-at fault test

The static test is used to detect the presence of stuck-at faults in the circuit. The test vectors are generated by a combinational ATPG using single stuck-at fault model. The stuck-at test application is carried out using an ATE. The test application involves shifting and launch of test vector, response capture, and shift-out of test response. First of all the scan enable (SE) is raised to logic high (1) level to switch the circuit from functional mode to test mode. Now by successive application of test clock the test vector is serially loaded into the scan chain through the scan-in (SI) pin. During the last shift cycle the test vector is also launched at the combinational inputs. After that the circuit is switched back to functional mode by making SE signal 0. Once the circuit is in functional mode, the test response is captured back into the scan cell by applying a clock pulse. Again,

the circuit is switched back to test or shift mode to unload the captured response. The unloading of test response is done with simultaneous loading of next test vector.

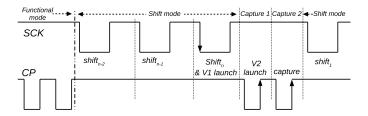

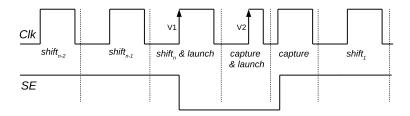

#### Delay fault test

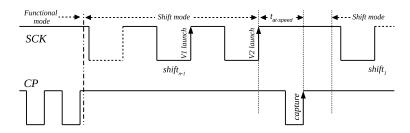

The delay test requires a test vector pair  $\langle V_1, V_2 \rangle$ . The first vector  $V_1$  initializes the circuit and the second vector  $V_2$  launches a transition. In scan based delay test the first vector  $V_1$ , also called initialization vector, is generated using a combinational ATPG. The second vector  $V_2$ , also called transition vector, can be generated in two ways. Depending upon how the  $V_2$  vector is generated the delay test is called Launch-off-Capture (LOC) or Launch-off-Shift (LOS).

- 1. Launch-off-Shift: In LOS based delay test the V<sub>2</sub> vector is one bit shift over initialization vector V<sub>1</sub>. The LOS test is also called skewed-load delay test [178]. The V<sub>1</sub> vector is launched in the last shift cycle. The response of V<sub>1</sub> is not captured in scan cells and the circuit is kept in test mode. To generate V<sub>2</sub> which is one bit shift over V<sub>1</sub> one clock pulse is applied. This extra shift clock pulse generates and launches the transition vector V<sub>2</sub>. To detect the presence of transition delay fault the response of transition vector needs to be captured at-speed. Hence, the SE signal must get disabled before the arrival of at-speed functional clock [179]. Hence in order to apply LOS test, the scan enable (SE) signal must be timing closed [134]. The SE signal is also a global signal just like the functional clock signal. To make SE signal timing closed is a very costly task. In general, the LOS test is not exercised into industry due to its very high implementation cost.

- 2. Launch-off-Capture: The LOC test is also called broad-side delay test because the second vector of the test vector pair is provided in a broad-side fashion, namely through the logic [179]. In LOC test the  $V_2$  vector is functional response of initialization vector  $V_1$ . The initialization vector  $V_1$  is loaded and launched into similar manner as in stuck-at test. The combinational response of vector  $V_1$ , which also acts as launch of vector  $V_2$ , is captured keeping the SE signal low and then applying

a clock pulse. The response of  $V_2$  is captured at-speed or at functional frequency. After the at-speed capture, SE is pulled up to logic high (1) again to shift-in the next test vector. Unlike LOS test the LOC test does not require timing closed SE signal [134].

#### 1.2.3 Issues in Scan Test

Over the years, serial scan design has become the de-facto Design for Testability (DFT) technique. The ease of testing and high test coverage has made it gain widespread industrial acceptance. Furthermore, scan design also plays a critical role in diagnosis and post-silicon debug. Despite all the good things that scan offers, it has some inherent issues which need urgent attention. The issues that scan design is currently facing are:

#### 1. Security Issue

- (a) Scan based side-channel attacks

- 2. Testability Issues

- (a) Test time and data volume

- (b) Test power

- (c) Scan performance overhead

Presently, scan security is one of the burning issue which needs urgent attention. The scan DFT architecture is posing a threat to security of hardware chips implementing cryptographic algorithms such as Advanced Encryption Standard (AES). Recently it has been shown in literature that the scan design can be exploited to steal sensitive data embedded on-chip such as secret encryption key.

The chip security and testability have orthogonal objectives. From a testability point of view, each and every storage element in the circuit must be observable and controllable through primary I/O pins. On the other hand, from security point of view, the visibility of circuit's internal information must be as less as possible. The scan architecture

has been designed to meet the testability requirements without considering the security requirements. A test engineers operates the scan design to shift in the test vector and shift out the corresponding test response. On the other hand, an attacker can exploit the scan design and apply crafted inputs and observe the corresponding sensitive data. So, there is a strong need to secure the scan DfT architecture which can effectively test the chip without compromising on the security of the chip.

Other then security the scan design also inherits some testability related issues because of its serial nature. The test related attributes of scan test like test power, test data volume, and test application time are also getting difficult to control with increasing circuit complexity. The test data volume and test time directly impacts the test cost and hence the final product cost. The test power is another very critical issue. It has impact on both the test time and yield. This thesis targets both security and testability aspects of scan design for present day complex SoC chips. Both the security as well as the testability issues are discussed in detail in Chapter 2.

### 1.3 Scope of Thesis

This thesis targets two main issues faced by modern day *VLSI* chips. In first part of the thesis the security issues in chip testing has been investigated. We have proposed techniques to secure the scan design against scan-based side-channel attacks. The proposed techniques secure the scan architecture without compromising on the testability aspects of scan design.

In second part of the thesis, we have worked on some outstanding scan test issues like test power, test time, and test data volume. We have explored an alternate test architecture called Joint-scan test which minimizes all the above said testability issues all together. We have proposed a unified framework to integrate both serial scan and RAS into a hybrid architecture to harness the best of both the architecture. Further, we also have targeted implementation issues in Joint-scan test architecture.

Moreover, we have also explored structural techniques to eliminate scan cell performance and unnecessary power dissipation in combinational logic during scan shift operation. Basically, we have proposed modified scan cell designs to eliminate these scan overheads. Furthermore, an area efficient hardware-assisted scan chain diagnosis technique has been proposed.

#### 1.3.1 Thesis Organization

The rest of the thesis has been organized as follows: Chapter 2 gives an elaborate introduction to security and testability issues in scan-based *VLSI* testing. It also discusses the state-of-the-art. Chapter 3 describes our proposed secure scan test techniques in detail. In Chapter 4 we delve into testability issues in scan test. We explore a new Jointscan test architecture to resolve testability issues of conventional scan design. Chapter 5 explains our proposed hardware-assisted area efficient scan chain diagnosis technique. Chapter 6 explores opportunity in scan cell design to eliminate combinational test power and scan performance overhead. Finally, we summarize the whole thesis in Chapter 7 along with summary of present key contribution of this work. The future directions where this work could be taken forward has also been discussed in this chapter.

- \* - \* -

## Chapter 2

## Motivation and the State-of-the-art

Scan design is the only practical test technique available today which can effectively test the complex modern day *VLSI* chips. However, scan inherits some which were touched upon in Chapter 1. In this Chapter, we discuss the security and testability cahallenges in scan test. We also explore the existing literature addressing these issues. We first discuss the vulnerabilities in scan design that made it a target of attackers to steal sensitive dat stored on-chip. Section 2.1 explains the mechanism of scan-based side-channel attacks. The state-of-the-art is reviewed in Subsection 2.1.2. The testability issues in scan test are explained in detail in Section 2.2. A brief review of the available literatue on these issues is also given in Subsection. The Chapter concludes in Section 2.3.

### 2.1 Security Issues in Scan Test

In modern era of information technology, security of the information has become vital. The communication of confidential information over an unprotected channel must be secure and need to be protected from intruders. The common practice is to encrypt the secret information using a cryptographic algorithm before transmission. Several cryptographic algorithms have been proposed and practiced for centuries. Presently, the Advanced Encryption Standard (AES) is the most commonly used symmetric cryptographic algorithm. In a symmetric cryptographic algorithm, the data is encrypted and

decrypted using a single private key which is also called encryption key. The private key is kept confidential and is not disclosed to any third party. The AES supports a fixed block size or plain text size of 128bit and an encryption key of 128bit, 192bit, or 256bit. The AES is implemented in both software as well as in hardware.

Over the last two-three decades, the amount of data to be exchanged has increased tremendously and hence high speed encryption algorithm is required. In order to communicate bulk data securely at a very high data rate, the data needs to be encrypted in real-time with very high throughput. The software-based AES implementation can not satisfy the requirement of encryption/decryption of data with very high throughput. In order to achieve very high throughput, the AES is implemented on a dedicated hardware. This dedicated hardware which implements cryptographic algorithm is often called cryptographic chip or crypto chip. There are two kinds of hardware implementations of AES: pipelined architecture and iterative architecture. In a fully pipelined implementation, every cycle there is a 128bit cipher text available at the outputs. The fully pipelined implementation offers highest possible throughput. However, it requires comparatively very large area. The iterative implementations, on the other hand offers reasonably good throughput and requires comparatively very less area. In iterative architecture, the plain text is converted into cipher text over a fixed number of iterative rounds of encryption. The number of rounds required to achieve sufficient level of encryption is a function of the key size. For a key size of 128bit, ten rounds of encryption are used. The level of encryption achieved after ten rounds is considered strong enough against any mathematical attack [151].

The AES is considered as a highly secure cryptographic algorithm and so far no brute-force or crypt-analytic attack have been reported in the literature that can break it in practical time. However, the cryptographic chips implementing AES cipher are found vulnerable to side channels attacks based on timing analysis, power analysis, and scan based DfT. As far as the security of crypto chips is concerned scan based DfT is a necessary evil. Despite the threat that it brings to crypto chips, the use of scan-based DfT can not be avoided because of the high fault coverage and diagnostic capability

that it offers. Presently scan-based DfT is the only practical test architecture available that can test a present day highly complex VLSI chip with a satisfactory fault coverage. As explained in Chapter 1, scan design adds one extra mode of operation to the circuit functionality. The extra mode of operation is popularly known as scan mode or test mode among the VLSI test community. By using the scan enable signal, which is available at the users disposal, the circuit can be switched between functional and test mode at anytime. During the scan mode, scan chains can be loaded and unloaded serially via the scan I/O pins. Hence, the circuit can be brought into any known state and the present state of the circuit can be observed.

The scan architecture generally is operated by a test engineer to perform three basic operations: test stimuli loading, stimuli launch, response capture (this is performed in functional mode) and response shift-out through scan-out pin. However, a malicious user can exploit the scan architecture to observe the intermediate state of the crypto chip during encryption operation. The fact that the level of encryption of intermediate states is not very high makes them the target of attackers. The level of encryption of the intermediate state after the first round of encryption is very poor. Because of this reason, almost all the known scan-based attacks target the first round intermediate data. The intermediate data for a sufficient number of plain-text input pairs are collected through scan operation. The attacker then analyzes these intermediate states to retrieve the secret encryption key.

### 2.1.1 AES and Scan-based Attack

A high-level block diagram of an iterative AES cipher is shown in Figure 2.1. In AES algorithm, initially, plain-text P is bit-wise XORed with private encryption key K. This step is called pre-round and is performed before the first round operation only. The XORed data is then transformed by three successive layers: S-Box, ShiftRows, and MixColumn. Finally, the transformed data is again XORed with Round key (RK) and stored in the round register R. This completes a single round. The transformed data stored in the round register is used as input for the next round. As stated earlier, for a

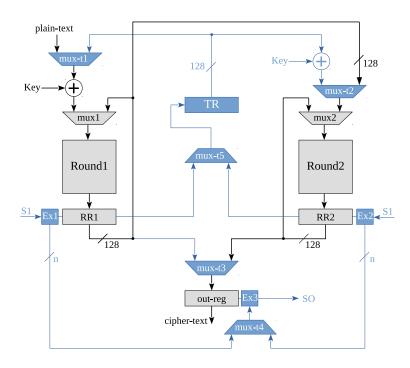

Figure 2.1: Schematic diagram of an AES cipher along with scan design

key size of 128bit, ten such rounds are performed iteratively to convert the plain-text into cipher-text. At the end of each round, transformed data is stored in the round register R. During the last round, i.e., the tenth round, the MixColumn operation is not used to make the encryption and decryption operations symmetric [151]. For every round, it uses a separate round key RK which is derived from the encryption key K. The RK is either pre-generated and stored on-chip or it is generated on-the-fly using round key generation logic. The level of encryption achieved in ten rounds is considered to have sufficient security against any known mathematical attack [151].

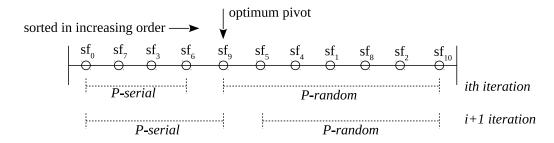

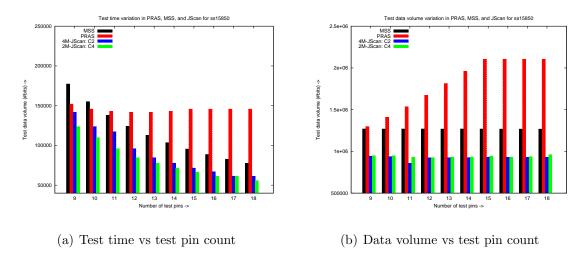

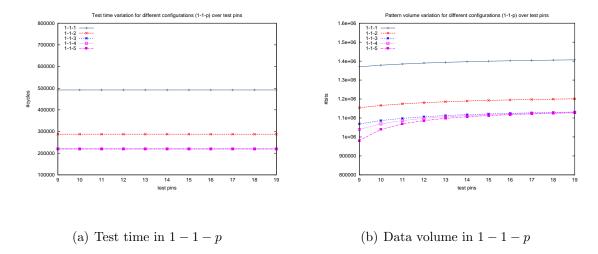

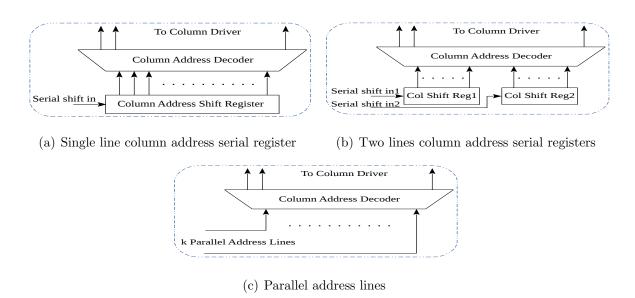

Now to make the AES circuitry fully testable, the round register R has to be included in the scan chain. As explained in the Introduction section, using the scan enable signal SE, the circuit can be switched at any time from functional mode to test mode and viceversa. In test mode, the scan chain values can be unloaded serially through the scan-out